原创:应用串行原创:应用串行NOR闪存提升内存处理能力闪存提升内存处理能力

在嵌入式系统中,NOR闪存一直以来仍然是较受青睐的非易失性内存,NOR器件的低延时特性可以接受代码执

行和数据存储在一个单一的产品。虽然NAND记忆体已成为许多高密度应用的首选解决方案,但NOR仍然是低

密度解决方案的首选之一。

Improve Memory Throughput with SPI NOR Flash

■ Spansion公司

在嵌入式系统中,

未来闪存产品具有快速发展的趋势,可以发现,闪存产品从低密度、低性能、低功能的发展特点转变为高密度、高性能、高功

能的发展特点。Spansion的NOR闪存广泛运用于汽车电子、医疗设备、通讯设备、机顶盒等。

SPI Flash特性

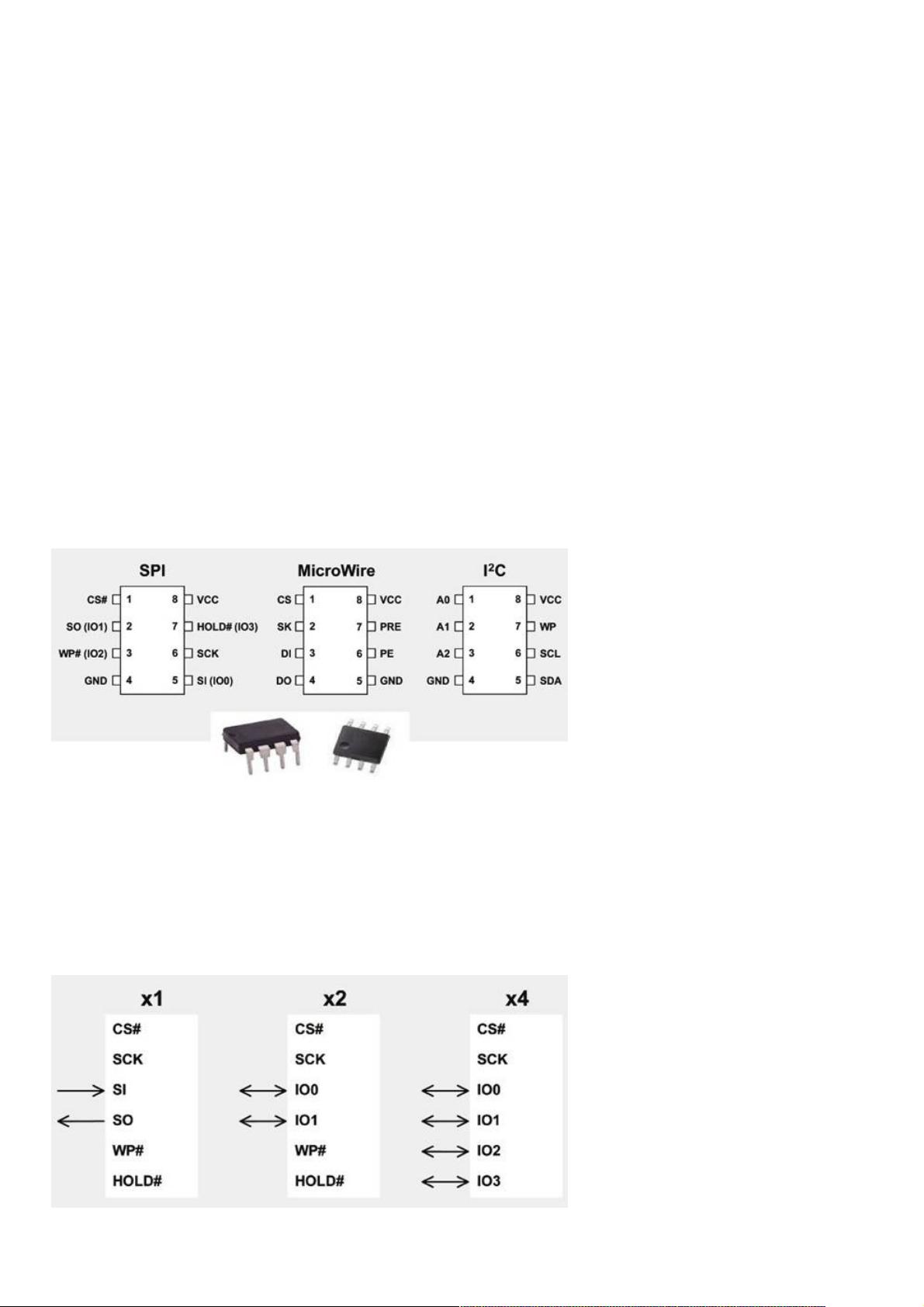

SPI串行结构的EEPROM最早出现于20世纪80年代中期,由摩托罗拉在其MC68HC系列中首先引入,MicroWire是由国半制定

的总线标准,它和SPI非常相似,只是MicroWire的时钟极性CPOL和时钟相位CPHA是固定的,均为0。I2C也是出现在80年

代,由Philips制定,它通过一条数据线和一条时钟线实现半双工通信,I2C总线接口实现了最简单的总线接口方式。三种标准

如图1所示。

SPI和MicroWire很相近,速度非常快,且在设计中无需上拉电阻,可以支持全双工通信操作,抗干扰能力强,缺点是需要占

用较多的数据总线,且需要为设备分配单独的片选信号,没有接收数据的硬板机制。对I2C总线来说,它占用的总线较少,可

以多个设备共同用一根总线,支持接收数据的硬板机制,缺点是速度较低,为3.4MHz以下,只支持半双工的操作,设计时需

要上拉电阻,且对噪声的干扰相对敏感。

图1 三种总线标准

SPI的接口从传统的单进单出已经提升到双进双出或者四进四出。如图2所示,通过单向输入SI,输出SO变为双向的传输,同

时将WP引脚和HOLD引脚复用为双向的IO口来实现多IO口的接口通信,其协议及基本的读写操作和原始EEPROM兼容,同时

硬件上实现简单的完全兼容。

相对于传统的并行NOR Flash而言,SPI NOR Flash只需要6个引脚就能够实现单I/O,双I/O和4个I/O口的接口通信,而并行的

NOR Flash则至少需要40个引脚。人们普遍使用的是标准NOR Flash异步读模式,而ADM及地址数据信号复用,这种并行

NOR Flash引脚数相对较少,通过实现突发读模式,其数据输出最快可超过120MB/s,SPI具有较少的引脚,同时,通过采用

DDR的方式读操作,在80MHz的时钟下,其数据输出可以达到80MB/s,甚至超过并行NOR Flash的异步读速度。

图2 SPI的接口转变