Verilog中阻塞赋值与非阻塞赋值语句的区别详解

需积分: 10 88 浏览量

更新于2024-09-16

收藏 462KB PDF 举报

"阻塞赋值与非阻塞赋值详解"

阻塞赋值和非阻塞赋值是Verilog中两种类型的赋值语句,它们在设计和仿真中扮演着非常重要的角色。正确理解阻塞赋值和非阻塞赋值的区别对于Verilog的设计和仿真非常重要。

阻塞赋值语句使用“=”符号,例如:`Q1=D;`,它的执行顺序是从右到左,先计算右侧的表达式,然后将结果赋值给左侧的变量。在阻塞赋值语句中,变量的赋值顺序是从上到下,例如:

```verilog

always @(posedge Clk) begin

Q1 = D;

Q2 = Q1;

Q3 = Q2;

end

```

在上面的例子中,首先将D的值赋值给Q1,然后将Q1的值赋值给Q2,最后将Q2的值赋值给Q3。这样,Q1、Q2和Q3的值都是在同一个时钟周期内赋值的。

非阻塞赋值语句使用“<=”符号,例如:`Q1<=D;`,它的执行顺序是从左到右,先将左侧的变量赋值给右侧的表达式,然后计算右侧的表达式。在非阻塞赋值语句中,变量的赋值顺序是从下到上,例如:

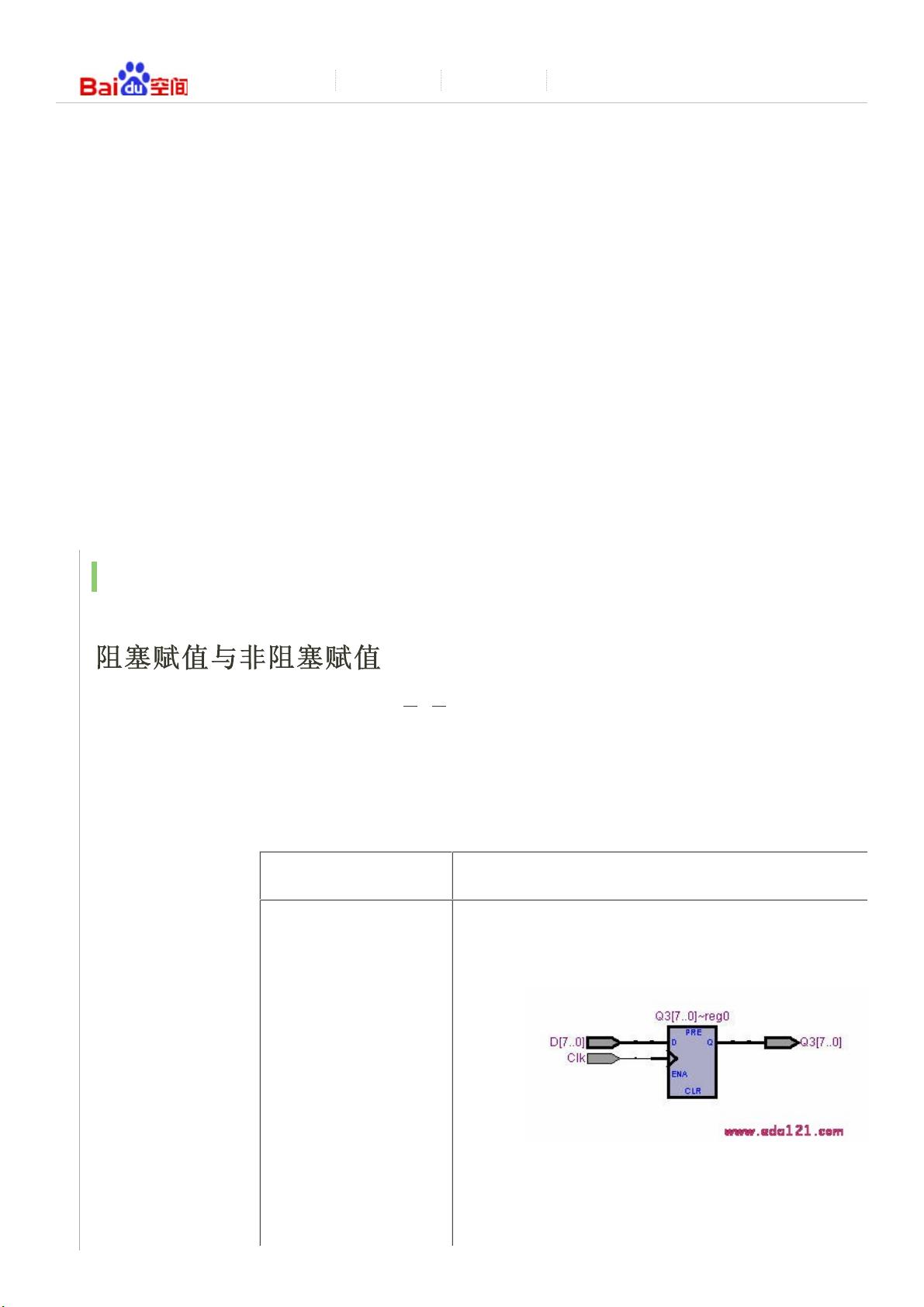

```verilog

always @(posedge Clk) begin

Q1 <= D;

Q2 <= Q1;

Q3 <= Q2;

end

```

在上面的例子中,首先将D的值赋值给Q1,然后将Q1的值赋值给Q2,最后将Q2的值赋值给Q3。这样,Q1、Q2和Q3的值都是在同一个时钟周期内赋值的。

在阻塞赋值语句中,如果变量的赋值顺序是从上到下,那么在同一个时钟周期内,变量的值都是最新的。在非阻塞赋值语句中,如果变量的赋值顺序是从下到上,那么在同一个时钟周期内,变量的值都是旧的。

阻塞赋值语句和非阻塞赋值语句的区别在于变量的赋值顺序和执行顺序。阻塞赋值语句的执行顺序是从右到左,变量的赋值顺序是从上到下;非阻塞赋值语句的执行顺序是从左到右,变量的赋值顺序是从下到上。

在设计和仿真中,正确理解阻塞赋值和非阻塞赋值的区别非常重要,因为它们对设计和仿真的结果有很大的影响。如果不正确理解阻塞赋值和非阻塞赋值的区别,可能会导致设计和仿真的结果不正确。

在Verilog中,阻塞赋值语句和非阻塞赋值语句都可以用于描述数字电路的行为,但它们的执行顺序和变量的赋值顺序是不同的。因此,在设计和仿真中,需要根据实际情况选择合适的赋值语句,以确保设计和仿真的结果正确。

182 浏览量

2008-10-24 上传

114 浏览量

264 浏览量

472 浏览量

2022-11-07 上传

105 浏览量

2019-05-27 上传

247 浏览量

大时代的小人物

- 粉丝: 7

最新资源

- Android平台DoKV:小巧强大Key-Value管理框架介绍

- Java图书管理系统源码与MySQL的无缝结合

- C语言实现JSON与结构体间的互转功能

- 快速标签插件:将构建信息轻松嵌入Java应用

- kimsoft-jscalendar:多语言、兼容主流浏览器的日历控件

- RxJava实现Android多线程下载与断点续传工具

- 直观示例展示JQuery UI插件强大功能

- Visual Studio代码PPA在Ubuntu中的安装指南

- 电子通信毕业设计必备:元器件与芯片资料大全

- LCD1602显示模块编程入门教程

- MySQL5.5安装教程与界面展示软件下载

- React Redux SweetAlert集成指南:增强交互与API简化

- .NET 2.0实现JSON数据生成与解析教程

- 上海交通大学计算机体系结构精品课件

- VC++开发的屏幕键盘工具与源码解析

- Android高效多线程图片下载与缓存解决方案