Cadence设计系统详解:清华大学微电子所讲义

需积分: 9 2 浏览量

更新于2024-08-01

1

收藏 3.62MB PPT 举报

"Cadence讲义_清华微电子所"

这篇讲义主要涵盖了Cadence设计系统在微电子领域的应用,特别是针对集成电路设计。Cadence是全球领先的电子设计自动化(EDA)软件供应商,其工具广泛用于IC设计、模拟和混合信号电路设计、版图设计和验证等多个环节。

首先,Cadence系统概述部分介绍了Cadence设计工具的重要性,特别是在面对集成电路设计复杂度不断提升的情况下。随着工艺技术的发展,例如特征尺寸从250nm逐渐减小到50nm,电源电压降低,芯片面积和晶体管数量大幅度增加,设计师需要借助Cadence这样的强大工具来应对挑战。讲义还提到了市场需求对设计复杂度的影响,以及学习Cadence工具的必要性。

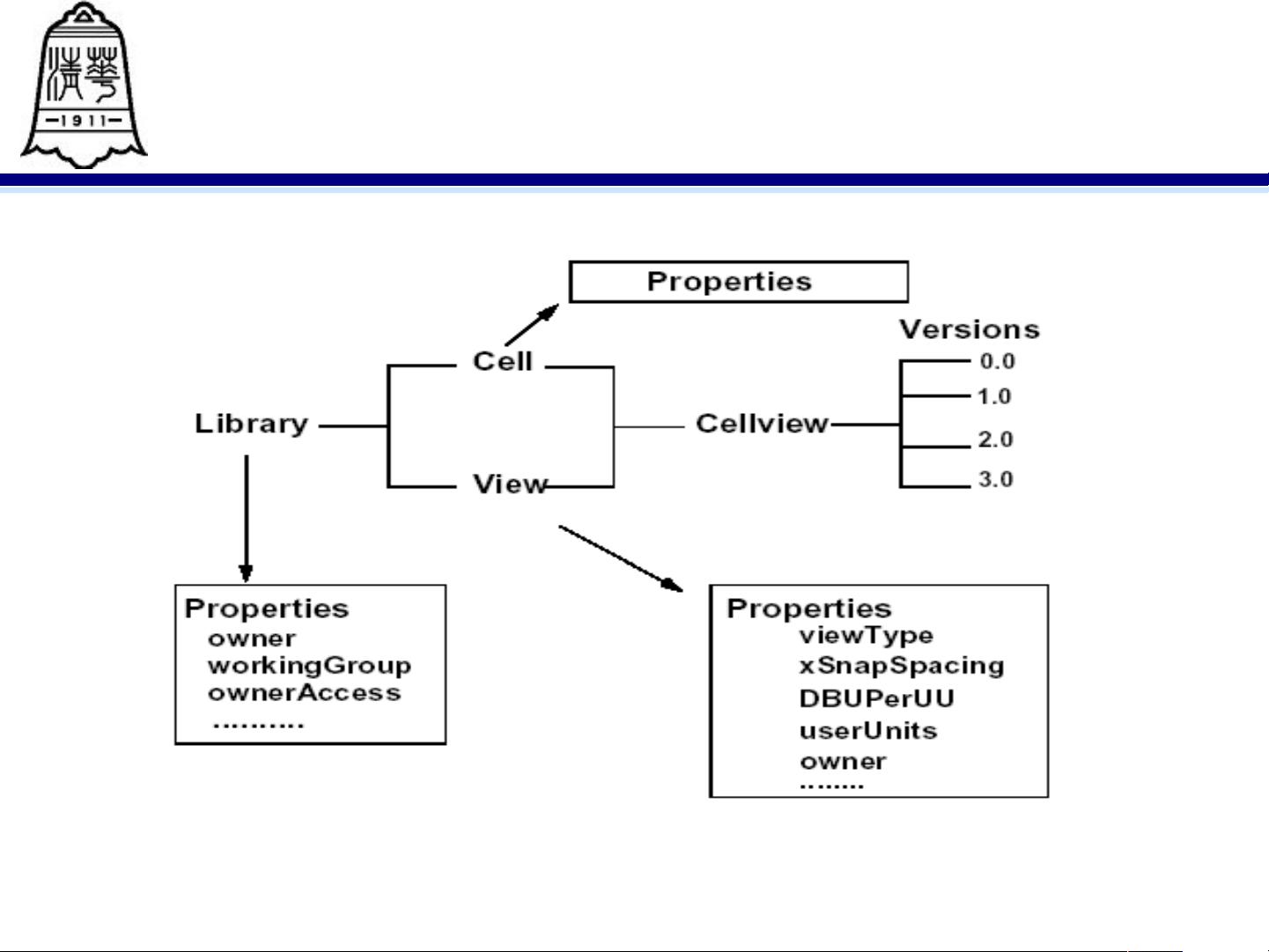

接着,讲义列出了Cadence系统的主要组成部分,包括设计流程、系统组织结构、系统启动和帮助系统。这表明用户不仅需要了解如何操作Cadence,还需要理解整个设计流程的上下文,以便有效地运用这些工具。

在详细内容中,提到了几个关键的Cadence工具,如Virtuoso用于版图设计,Diva和Dracula用于版图验证。Virtuoso是一款高级的模拟IC设计环境,支持复杂电路的布局与布线。Diva和Dracula则专注于版图的检查和验证,确保设计符合规格和工艺限制。

此外,讲义还提到了设计流程中的不同阶段,包括VHDL仿真(用于验证设计行为)、行为综合(将高级语言描述转化为逻辑门级表示)、逻辑综合(优化逻辑设计以适应特定工艺)、可测性设计(确保设计可以被有效测试)和低功耗设计(减少芯片功耗)。这些步骤展示了从概念设计到物理实现的完整过程。

最后,讲义指出,随着晶体管密度的增加,功耗和发热成为设计中的关键问题,因此低功耗设计变得越来越重要。Cadence工具集提供了相应的解决方案,帮助设计师在满足性能要求的同时降低功耗。

这份“Cadence讲义_清华微电子所”提供了关于Cadence设计系统的全面介绍,强调了它在应对现代集成电路设计挑战中的核心地位,并涵盖了从设计到验证的关键步骤。对于微电子专业的学生和工程师来说,理解和掌握Cadence工具是至关重要的。

122 浏览量

528 浏览量

2011-08-14 上传

122 浏览量

101 浏览量

EEYYEE

- 粉丝: 14

- 资源: 3

最新资源

- NCRE二级C语言程序设计辅导

- basic linux command

- Java笔试时可能出现问题及其答案.doc

- 同济大学线性代数第四版课后习题答案

- A Guide to MATLAB for Beginners and Experienced Users - Hunt Lipsman & Rosenberg

- Oracle9i:SQL Ed 2.0.pdf

- ejb3.0实例教程

- oracle-commands-zh-cn

- inno setup 脚本集

- IT服务能力成熟度模型

- PCB转原理图方法攻略

- PHP登录注册制作过程

- 硬件工程师手册_华为资料

- 神奇的-----ant的使用

- XILINXSPARTAN_start_kit_3manual.pdf

- R1762_R2632_R2700 RGNOS10.2配置指南_第一部分 基础配置指南