Synopsys DesignWare CDC解决方案详解:跨时钟域信号同步与Verilog应用

需积分: 9 155 浏览量

更新于2024-07-16

收藏 1.01MB PDF 举报

跨时钟域信号同步是现代集成电路设计中的关键挑战,尤其是在系统级芯片(SoC)中,由于多时钟域的广泛使用和复杂性提升。《跨时钟域Yuchuli》这篇文章由Rick Kelly,Synopsys的研发经理于2009年撰写,针对设计人员如何有效地解决这一问题提供了深入的指导。

文章首先强调了确保异步时钟域间信号稳定传输的重要性,因为错误的同步可能导致系统不稳定,甚至导致严重的性能问题。设计人员需要确保时钟和数据信号在跨越不同频率的时钟域之间保持一致,以避免潜在的亚稳态现象和时序收敛问题。

文中提到的主要同步解决方案包括:

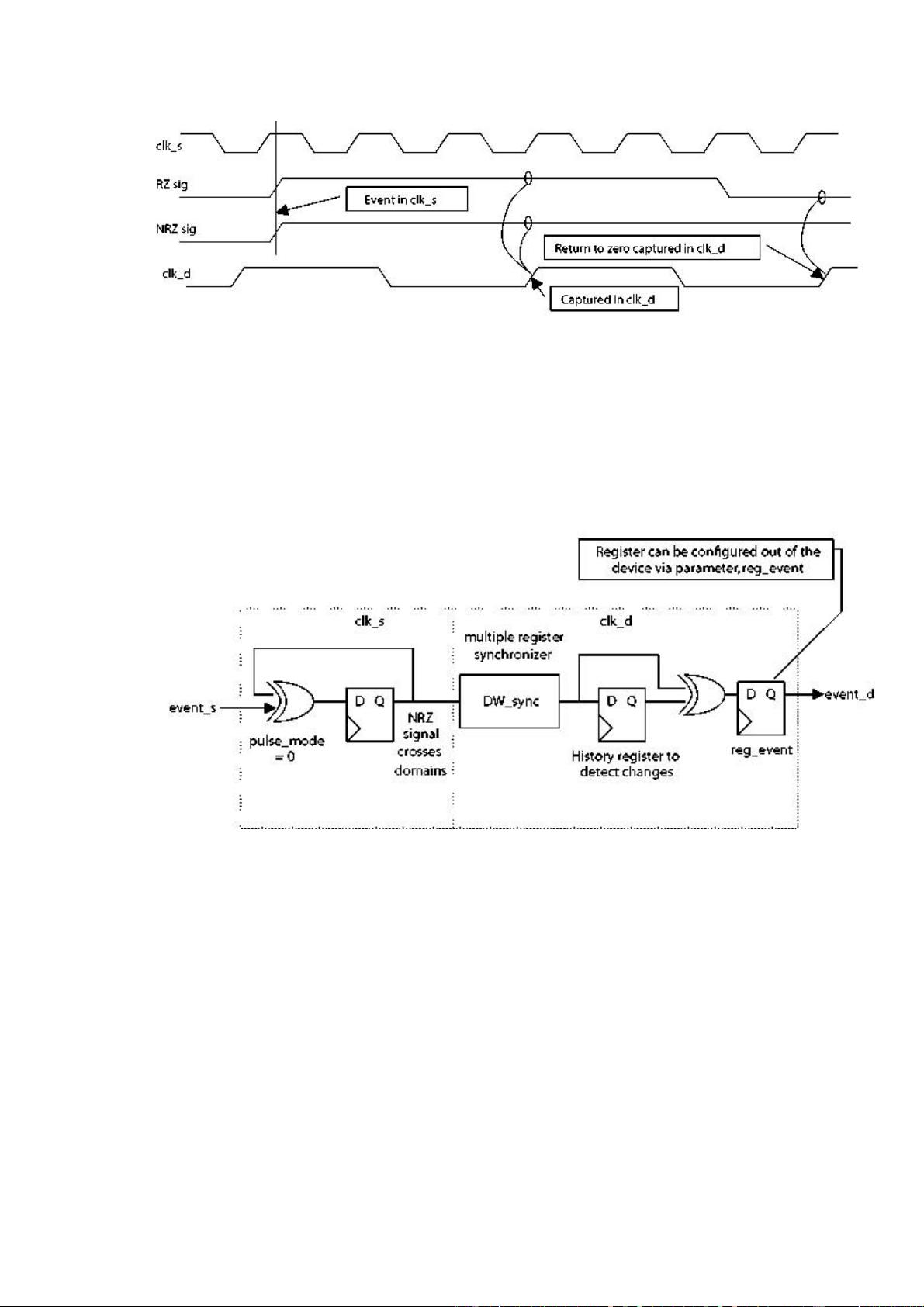

1. **基本同步** - DW_sync:这是最基础的同步方法,涉及使用单个寄存器来将一个时钟域的信号适配到另一个时钟。然而,这种同步可能会导致亚稳态问题,需要额外措施来解决。

2. **临时事件同步** - DW_pulse_sync和DW_pulseack_sync:针对临时的脉冲信号,提供了一种特殊的同步机制,可以精确控制信号的触发时机。

3. **简单数据传输同步** - DW_data_sync、DW_data_sync_na和DW_data_sync_1c:这些解决方案适用于数据传输,可能包括不同的优化级别,旨在减小同步延迟并确保数据一致性。

4. **数据流同步** - DW_fifo_s2_sf、DW_fifo_2c_df和DW_stream_sync:利用FIFO(先进先出队列)或其他流式处理技术,对连续的数据流进行有效同步,减少时钟抖动的影响。

5. **复位排序** - DW_reset_sync:在复位操作中,不同时钟域的复位信号也需要正确同步,以防止混乱。

6. **相关时钟系统数据同步** - DW_data_qsync_hl和DW_data_qsync_lh:这些高级同步技术关注于在保持信号质量和性能的同时,处理具有特定时间关系的多时钟数据流。

通过这些解决方案,设计人员可以根据具体场景选择最适合的方法,确保跨时钟域的设计不仅功能可靠,而且性能高效。在实践中,理解这些概念和工具的使用至关重要,因为它们直接影响到整个SoC设计的稳定性和性能。此外, Synopsys DesignWare库提供的这些预集成解决方案简化了跨时钟域设计的过程,降低了实现复杂同步任务的难度。

2018-09-12 上传

2022-07-15 上传

2022-07-15 上传

2022-07-13 上传

2022-07-14 上传

2021-10-03 上传

暖h暖h

- 粉丝: 2

- 资源: 3