基于TMS320C6416的数字下变频技术在数字接收机中的应用

184 浏览量

更新于2024-09-01

收藏 191KB PDF 举报

“数字接收机中基于TMS320C6416的数字下变频技术”

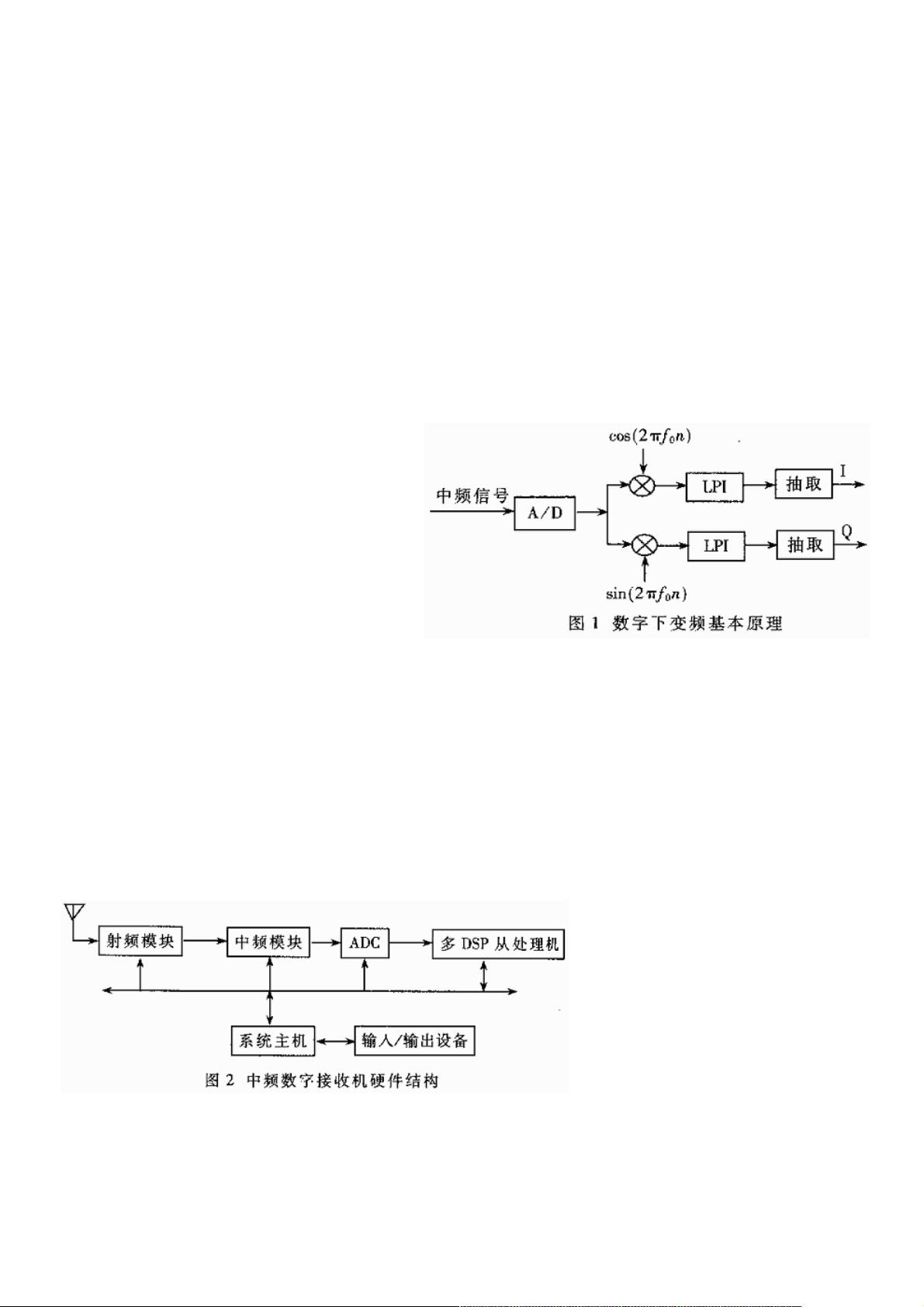

在现代通信和雷达系统中,数字接收机扮演着至关重要的角色,尤其是在高采样率和大带宽的应用场景下。数字下变频(Digital Down Conversion,DDC)是一种关键技术,它能够将中频信号转换成基带信号,从而降低数据速率,减轻后续信号处理的复杂性和计算负担。中频数字接收机通常采用DDC来实现这一目的。

传统的数字下变频器通常由专用集成电路(如Harris公司或Gray-Chip公司的产品)构建,但它们可能无法满足特定应用,如雷达对抗侦察数字接收机的高性能要求。在这种情况下,采用高性能的数字信号处理器(DSP)如TI公司的TMS320C6416成为一种可行的选择。

TMS320C6416是一款强大的浮点DSP,具有高处理能力和快速响应,适合执行复杂的数字信号处理任务。在数字下变频过程中,它能有效地进行混频、滤波和抽取操作。基本的数字下变频原理包括将经过模数转换(A/D)的中频信号与两个参考信号相乘,生成I(In-phase)和Q(Quadrature)两路信号。然后,I和Q信号通过低通滤波器去除高频成分,并通过抽取操作降低采样率,形成基带信号。

以一个具体例子说明,假设中频频率fc为200MHz,带宽B为20MHz,采样频率fs为500MHz。为了避免混叠,下变频可以选择将中频频率变到非零值,例如190MHz,这样下变频后的信号位于0至20MHz之间。通过10倍抽取,将采样频率降低到50MHz,有效地处理下变频后的信号。

在实际应用中,选择TMS320C6416作为处理器是因为它具备高速处理能力,能够处理500MHz的采样频率,满足了混频运算的实时性需求。此外,DSP还需要具备足够的内存来存储中间计算结果和滤波器系数,以及足够的并行处理能力来执行快速傅里叶变换(FFT)和其他计算密集型算法,以实现高效的数字下变频。

基于TMS320C6416的数字下变频技术提供了一种灵活且可扩展的解决方案,适用于需要处理高带宽、高采样率信号的雷达对抗侦察等应用场景。这种技术通过优化的算法设计和高效的硬件平台,实现了对复杂信号的实时处理,提升了系统的整体性能和可靠性。

2020-12-10 上传

116 浏览量

2020-12-08 上传

2020-10-21 上传

2020-10-21 上传

点击了解资源详情

2020-07-31 上传

183 浏览量

235 浏览量

weixin_38744270

- 粉丝: 329

- 资源: 2万+

最新资源

- 新经济及创新商业模式企业改制

- newage-slowmonitor-viewer:慢速监控器

- Bayes:贝叶斯定理:离散情况。-matlab开发

- 基于 zircon 并提供 Linux 兼容操作系统内核

- 上海省乡镇级区划图 shp格式

- 1c-server-repo:1C配置存储服务器

- Code-Quiz:测验您的JS知识的测验

- scatplot:用颜色表示数据密度的散点图。-matlab开发

- 詹戈

- 商业模式与品牌快速成长之道

- 基于socket通讯的文件续传!

- 编译好的OSG-3.4.0库文件

- Collatz:检查 Collatz 序列的工具。-matlab开发

- RadioStationHub

- flask-survey

- 用于全志 SOC 的微型 FEL 工具