Introduction

18 Datasheet, Volume 2

§

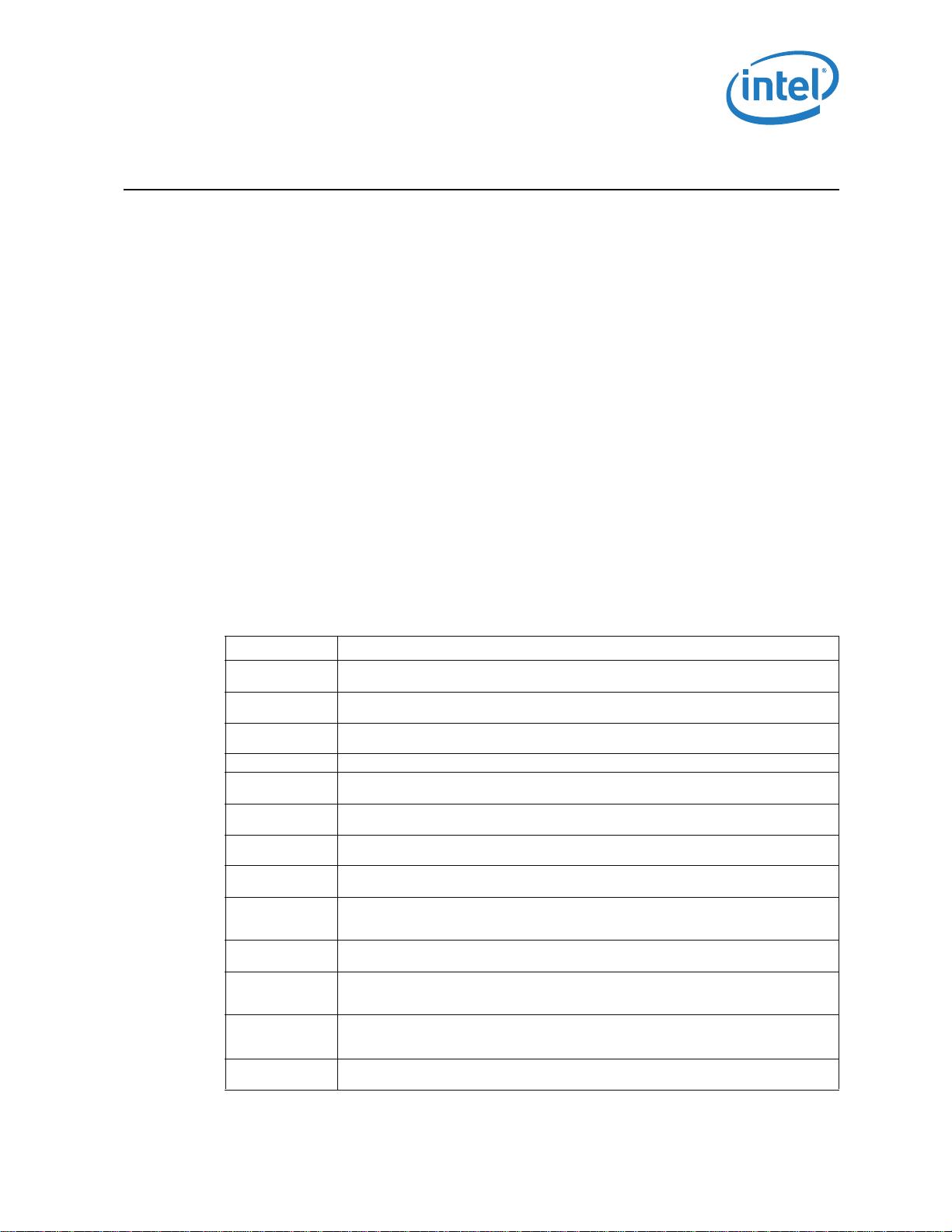

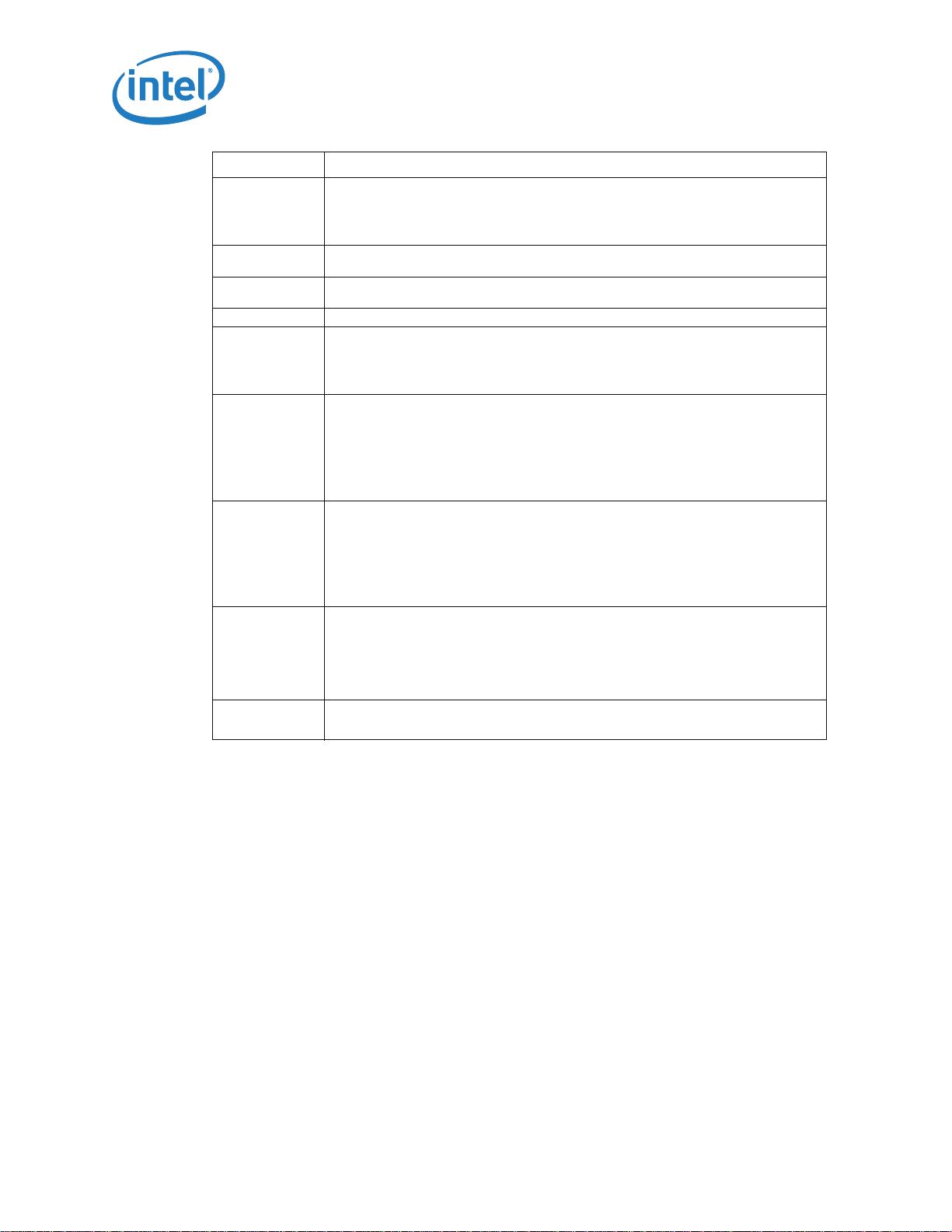

RWO

Read/Write Once. A register bit with this attribute can be written to only once after

power up. After the first write, the bit becomes read only. This attribute is applied on a bit

by bit basis. For example, if the RWO attribute is applied to a 2-bit field, and only one bit

is written, then the written bit cannot be rewritten (unless reset). The unwritten bit, of the

field, may still be written once. This is special case of RWL.

RWDS

RW and Sticky. Re-initialized to default value only with POWERGOOD reset. Value

written will take effect on the next Link layer init.

RRW

Read/Restricted Write. This bit can be read and written by software. However, only

supported values will be written. Writes of non supported values will have no effect.

L Lock. A register bit with this attribute becomes Read Only after a lock bit is set.

RSVD/RV

Reserved Bit. This bit is reserved for future expansion and must not be written. The

latest version of the PCI Local Bus Specification, requires that reserved bits must be

preserved. Any software that modifies a register that contains a reserved bit is

responsible for reading the register, modifying the desired bits, and writing back the

result.

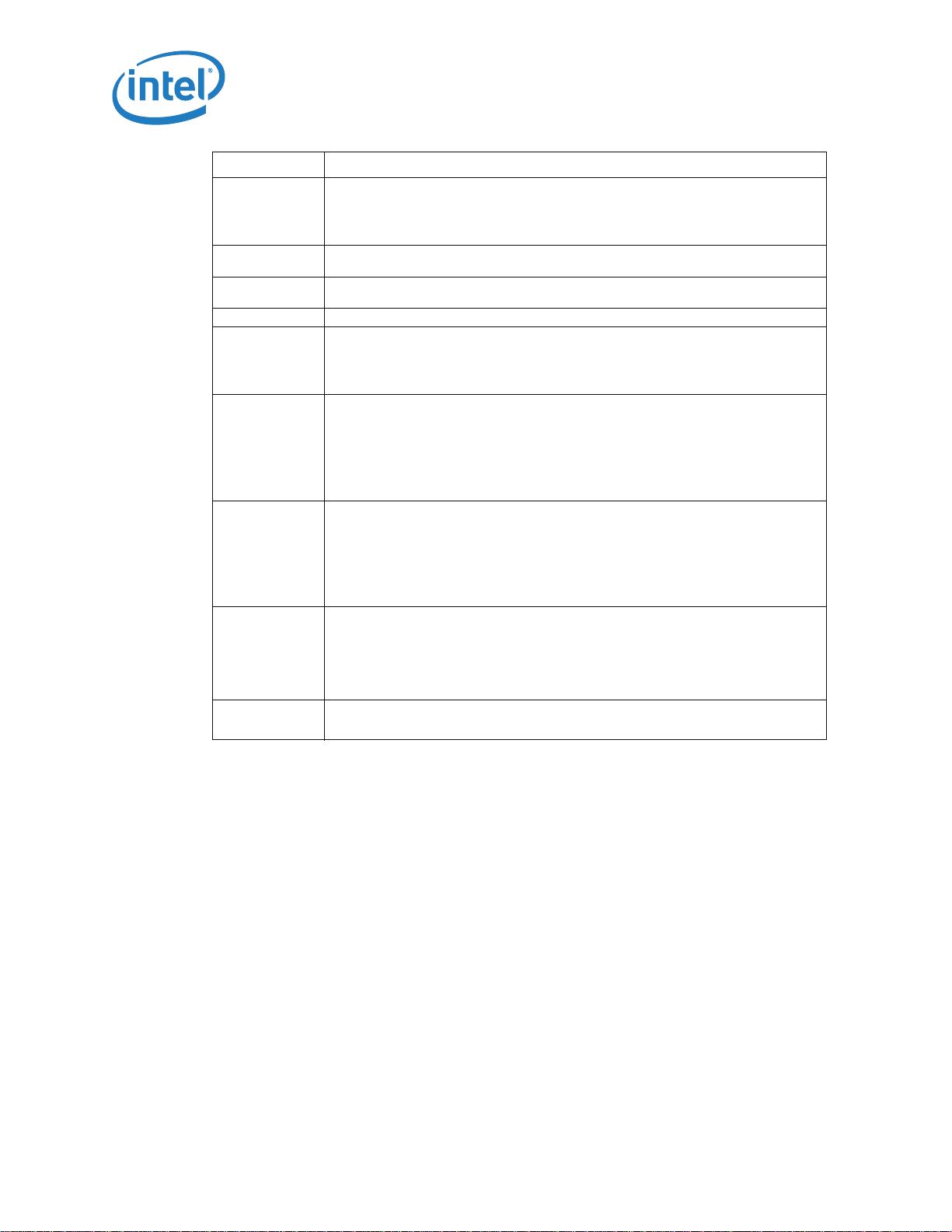

Reserved Bits

Some of the processor registers described in this section contain reserved bits. These bits

are labeled “Reserved”. Software must deal correctly with fields that are reserved. On

reads, software must use appropriate masks to extract the defined bits and not rely on

reserved bits being any particular value. On writes, software must ensure that the values

of reserved bit positions are preserved. That is, the values of reserved bit positions must

first be read, merged with the new values for other bit positions and then written back.

Note that software does not need to perform a read-merge-write operation for the

Configuration Address (CONFIG_ADDRESS) register.

Reserved

Registers

In addition to reserved bits within a register, the processor contains address locations in

the configuration space that are marked either “Reserved” or “Intel Reserved”. The

processor responds to accesses to “Reserved” address locations by completing the host

cycle. When a “Reserved” register location is read, a zero value is returned. (“Reserved”

registers can be 8, 16, or 32 bits in size). Writes to “Reserved” registers have no effect on

the processor. Registers that are ®marked as “Intel Reserved” must not be modified by

system software. Writes to “Intel Reserved” registers may cause system failure. Reads to

“Intel Reserved” registers may return a non-zero value.

Default Value

upon a Reset

Upon a reset, the processor sets all of its internal configuration registers to predetermined

default states. Some register values at reset are determined by external strapping

options. The default state represents the minimum functionality feature set required to

successfully bring up the system. Hence, it does not represent the optimal system

configuration. It is the responsibility of the system initialization software (usually BIOS) to

properly determine the DRAM configurations, operating parameters and optional system

features that are applicable, and to program the processor registers accordingly.

“ST” appended to

the end of a bit

name

The bit is “sticky” or unchanged by a hard reset. These bits can only be cleared by a

PWRGOOD reset.

Term Description