基于FPGA和SoC的高速数据采集系统设计

版权申诉

DOC格式 | 346KB |

更新于2024-08-29

| 86 浏览量 | 举报

"高速数据采集系统设计说明书"

高速数据采集系统是一种关键的技术,广泛应用于自动测试、生产控制、通信和信号处理等领域。随着科技的进步,尤其是SoC(System on Chip)单片机的发展,数据采集系统得以高度集成,使得在单芯片上集成了多路模拟信号的A/D转换和CPU核心,这显著减小了系统的体积,提升了性价比。FPGA(Field-Programmable Gate Array)因其高速性能、内置逻辑门和嵌入式存储器,成为实现高速数据采集的理想选择。FPGA的优势在于其可编程性,允许系统轻松升级,缩短开发周期。

设计要求明确指出,要构建一个高速数据采集系统,能够处理频率为200KHz、幅度为Vpp=0.5V的正弦信号,采用25MHz的采样频率。系统应能通过按键启动,每次连续采集128点数据,并在LCD模块上实时显示回放的信号波形。

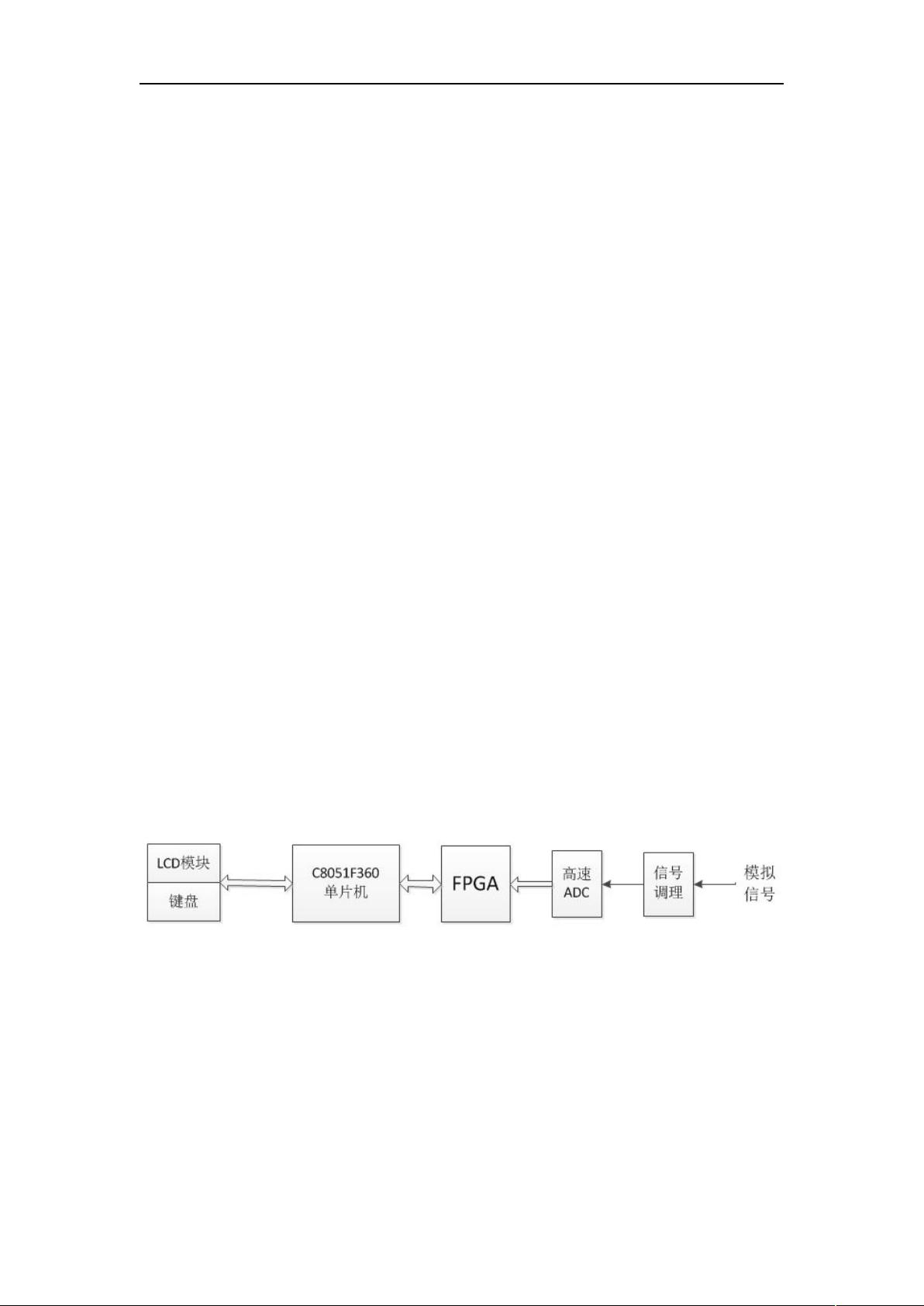

整体方案设计中,高速数据采集系统由三个主要部分构成:单片机最小系统、FPGA最小系统和模拟量输入通道。模拟量输入通道包括高速A/D转换器和信号调理电路。信号调理电路负责将输入信号放大、滤波和调整直流电平,以适应A/D转换器的需求。A/D转换器以25MHz的速率进行采样,生成的数字信号存储在FPGA内部的FIFO(First In First Out)存储器中,随后由单片机读取并在LCD上展示。

FPGA模块的设计关键在于FIFO数据缓冲电路。FIFO的写端口直接连接到A/D转换器,两者共享同一时钟信号。读端口则与单片机的并行总线连接,通过三态缓冲器输出数据。FIFO的片选信号和读信号由地址译码器生成,确保数据传输的正确性和同步性。

这个高速数据采集系统的设计涵盖了信号调理、高速A/D转换、FPGA中的数据缓冲和单片机的数据处理等多个关键技术环节。通过优化这些环节,系统能够在保持高采样率的同时,实现快速的数据处理和实时显示,为现代工业控制和科学研究提供了高效的数据获取手段。

相关推荐

天泽通信

- 粉丝: 3

最新资源

- Node.js中使用multer上传多图并在MongoDB存储路径

- 点击图片实现放大特效的CSS3代码教程

- 鲜花网页模板下载:香萦满屋设计典范

- SQLiteStudio 3.3.1:高效数据库查看与管理工具

- Flask框架全文搜索引擎实现指南

- 构建个人网站:HTML基础与实践

- 打造健康生活:蔬菜水果主题网站模板

- Node.js项目实战:使用Express, Passport和JWT构建Rest API

- 记事本设计工作室模板:简洁风格网页设计

- AnimeGAN: Tensorflow下的照片动画快速转换技术

- React-Leaflet组件:打造动态传单地图应用

- 实现全屏图片模糊切换的HTML5响应式特效

- Node.js实现PNG文件上传功能指南

- Smallpdf:一站式PDF编辑、压缩与转换解决方案

- 构建基于scikit-learn的Flask预测API

- Libsvm-3.23工具箱:机器学习中的支持向量机源代码