ADF4157在数字预失真系统中的高性能时钟设计

需积分: 5 128 浏览量

更新于2024-08-11

收藏 279KB PDF 举报

"ADF4157在数字预失真时钟方案中的应用,电子器件,张福洪,罗晚会,杨小海,2010年4月"

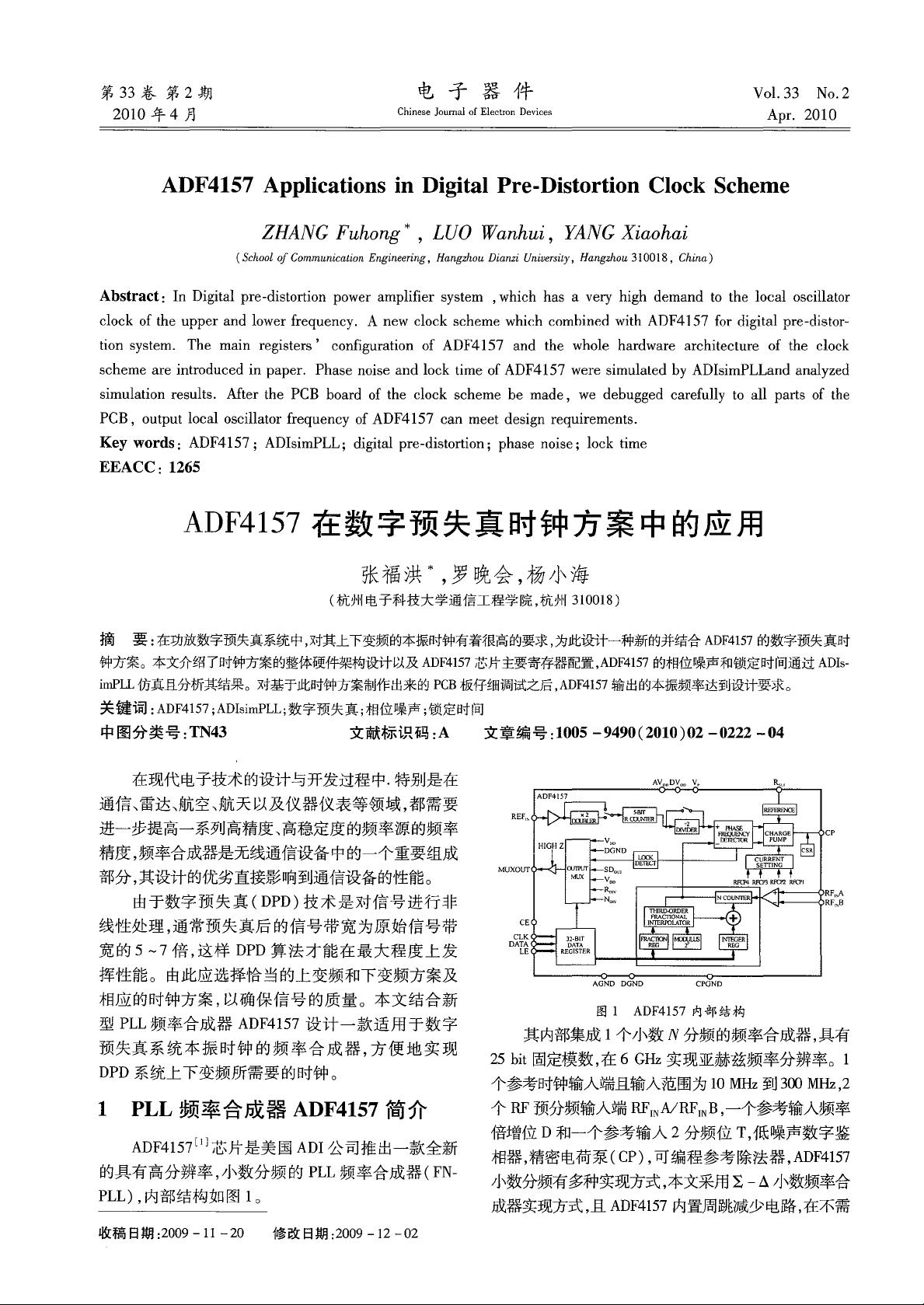

在数字通信系统,尤其是高功率放大器(Power Amplifier, PA)的设计中,数字预失真(Digital Pre-Distortion, DPD)技术是一种重要的线性化手段,它通过在信号输入到功率放大器之前对其进行逆向失真来补偿放大器在大功率工作时产生的非线性效应。ADF4157是ADI公司生产的一款高性能的频率合成器,常用于需要精确频率控制的应用中。该芯片在数字预失真时钟方案中的应用,主要涉及到其内部寄存器配置、硬件架构设计以及性能分析。

在论文中,作者提出了一种基于ADF4157的数字预失真时钟系统设计方案。ADF4157的主要特点是具有高精度和低相位噪声,这对于保证数字预失真系统的性能至关重要。文章详细阐述了ADF4157的主要寄存器配置,这些寄存器通常用于设定锁相环(Phase-Locked Loop, PLL)的工作参数,如参考频率、分频比、输出频率等,以实现所需的本振(Local Oscillator, LO)时钟。

硬件架构部分,作者介绍了如何将ADF4157集成到数字预失真系统的时钟模块中。这通常包括ADC/DAC接口、数字信号处理器(DSP)以及其他必要的支持电路。时钟方案的正确设计能确保预失真算法的实时性和系统稳定性。

此外,论文还通过ADIsimPLL进行了ADF4157的相位噪声和锁定时间的仿真分析。相位噪声直接影响到信号的质量,而锁定时间则关系到系统能否快速稳定到期望的工作状态。仿真结果有助于优化芯片的参数设置,以满足系统的性能指标。

在实际的PCB板级设计完成后,作者对整个时钟方案进行了详尽的调试,验证了ADF4157输出的本振频率能够满足数字预失真系统的设计需求。这一成果对于提升功率放大器的线性度,降低互调失真(Intermodulation Distortion, IMD)和提高射频系统的整体效率具有重要意义。

关键词:ADF4157;ADIsimPLL;数字预失真;相位噪声;锁定时间

该论文深入探讨了ADF4157在数字预失真系统时钟方案中的应用,包括芯片的特性、设计方法和性能评估,为相关领域的工程师提供了有价值的参考。

2020-11-03 上传

2020-07-29 上传

点击了解资源详情

点击了解资源详情

2020-10-25 上传

2020-12-04 上传

2020-11-05 上传

2021-09-09 上传

2021-02-01 上传

weixin_38627234

- 粉丝: 4

- 资源: 934

最新资源

- 前端协作项目:发布猜图游戏功能与待修复事项

- Spring框架REST服务开发实践指南

- ALU课设实现基础与高级运算功能

- 深入了解STK:C++音频信号处理综合工具套件

- 华中科技大学电信学院软件无线电实验资料汇总

- CGSN数据解析与集成验证工具集:Python和Shell脚本

- Java实现的远程视频会议系统开发教程

- Change-OEM: 用Java修改Windows OEM信息与Logo

- cmnd:文本到远程API的桥接平台开发

- 解决BIOS刷写错误28:PRR.exe的应用与效果

- 深度学习对抗攻击库:adversarial_robustness_toolbox 1.10.0

- Win7系统CP2102驱动下载与安装指南

- 深入理解Java中的函数式编程技巧

- GY-906 MLX90614ESF传感器模块温度采集应用资料

- Adversarial Robustness Toolbox 1.15.1 工具包安装教程

- GNU Radio的供应商中立SDR开发包:gr-sdr介绍