2003-2012 Microchip Technology Inc. DS21801G-page 15

MCP2515

3.0 MESSAGE TRANSMISSION

3.1 Transmit Buffers

The MCP2515 implements three transmit buffers. Each

of these buffers occupies 14 bytes of SRAM and are

mapped into the device memory map.

The first byte, TXBnCTRL, is a control register

associated with the message buffer. The information in

this register determines the conditions under which the

message will be transmitted and indicates the status of

the message transmission (see Register 3-2).

Five bytes are used to hold the standard and extended

identifiers, as well as other message arbitration

information (see Register 3-4 through Register 3-7).

The last eight bytes are for the eight possible data

bytes of the message to be transmitted (see

Register 3-8).

At a minimum, the TXBnSIDH, TXBnSIDL and

TXBnDLC registers must be loaded. If data bytes are

present in the message, the TXBnDm registers must

also be loaded. If the message is to use extended

identifiers, the TXBnEIDm registers must also be

loaded and the TXBnSIDL.EXIDE bit set.

Prior to sending the message, the MCU must initialize

the CANINTE.TXInE bit to enable or disable the

generation of an interrupt when the message is sent.

3.2 Transmit Priority

Transmit priority is a prioritization within the MCP2515

of the pending transmittable messages. This is

independent from, and not necessarily related to, any

prioritization implicit in the message arbitration scheme

built into the CAN protocol.

Prior to sending the SOF, the priority of all buffers that

are queued for transmission is compared. The transmit

buffer with the highest priority will be sent first. For

example, if transmit buffer 0 has a higher priority setting

than transmit buffer 1, buffer 0 will be sent first.

If two buffers have the same priority setting, the buffer

with the highest buffer number will be sent first. For

example, if transmit buffer 1 has the same priority

setting as transmit buffer 0, buffer 1 will be sent first.

There are four levels of transmit priority. If

TXBnCTRL.TXP<1:0> for a particular message buffer

is set to 11, that buffer has the highest possible priority.

If TXBnCTRL.TXP<1:0> for a particular message buf-

fer is 00, that buffer has the lowest possible priority.

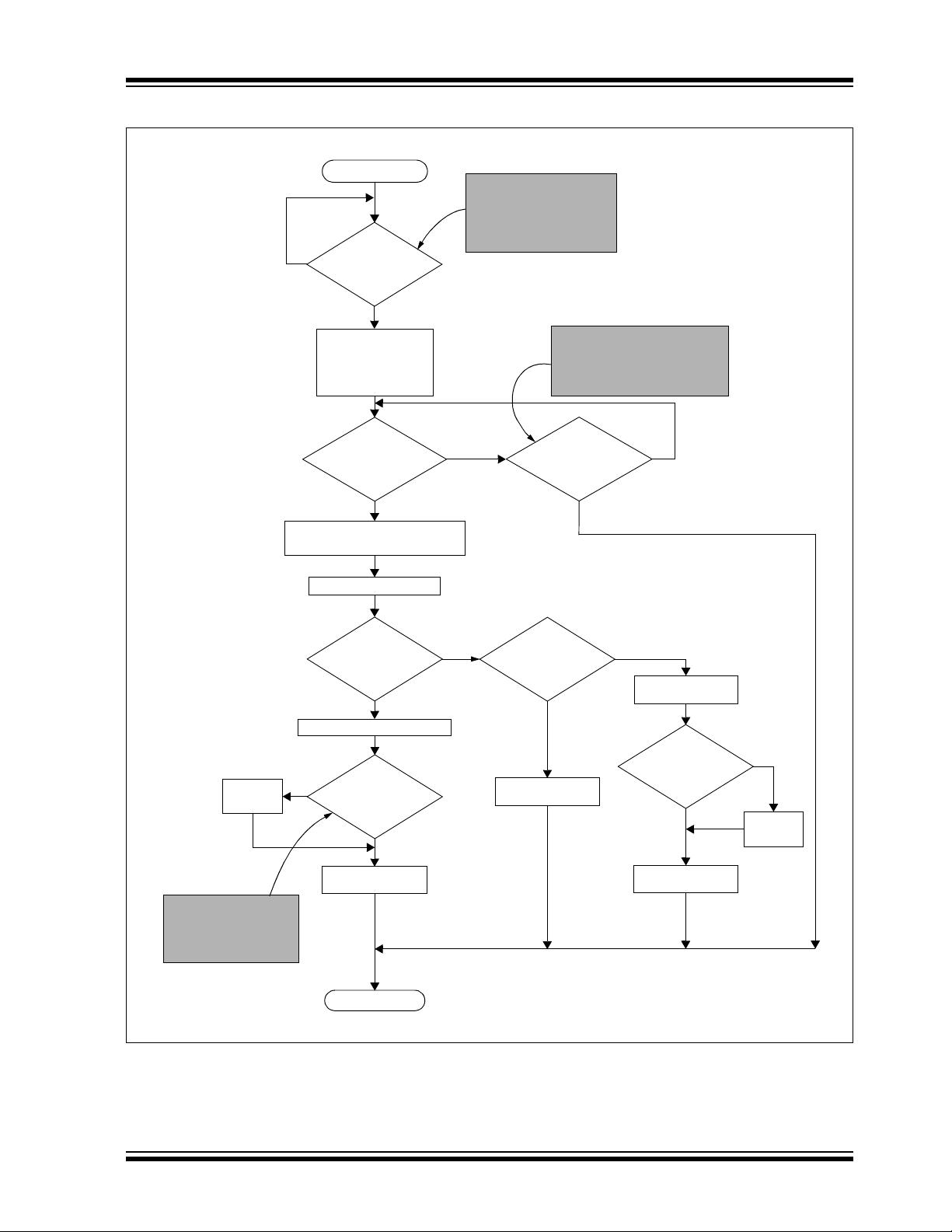

3.3 Initiating Transmission

In order to initiate message transmission, the

TXBnCTRL.TXREQ bit must be set for each buffer to

be transmitted. This can be accomplished by:

• Writing to the register via the SPI write command

• Sending the SPI RTS command

• Setting the TX

nRTS pin low for the particular

transmit buffer(s) that are to be transmitted

If transmission is initiated via the SPI interface, the

TXREQ bit can be set at the same time as the TXP

priority bits.

When TXBnCTRL.TXREQ is set, the TXBnCTRL.ABTF,

TXBnCTRL.MLOA and TXBnCTRL.TXERR bits will be

cleared automatically.

Once the transmission has completed successfully, the

TXBnCTRL.TXREQ bit will be cleared, the

CANINTF.TXnIF bit will be set and an interrupt will be

generated if the CANINTE.TXnIE bit is set.

If the message transmission fails, the

TXBnCTRL.TXREQ will remain set. This indicates that

the message is still pending for transmission and one

of the following condition flags will be set:

• If the message started to transmit but encoun-

tered an error condition, the TXBnCTRL.TXERR

and the CANINTF.MERRF bits will be set and an

interrupt will be generated on the INT

pin if the

CANINTE.MERRE bit is set

• If the message is lost, arbitration at the

TXBnCTRL.MLOA bit will be set

3.4 One-Shot Mode

One-Shot mode ensures that a message will only

attempt to transmit one time. Normally, if a CAN

message loses arbitration, or is destroyed by an error

frame, the message is retransmitted. With One-Shot

mode enabled, a message will only attempt to transmit

one time, regardless of arbitration loss or error frame.

One-Shot mode is required to maintain time slots in

deterministic systems, such as TTCAN.

Note: The TXBnCTRL.TXREQ bit must be clear

(indicating the transmit buffer is not

pending transmission) before writing to

the transmit buffer.

Note: Setting the TXBnCTRL.TXREQ bit does

not initiate a message transmission. It

merely flags a message buffer as being

ready for transmission. Transmission will

start when the device detects that the bus

is available.

Note: If One-Shot mode is enabled

(CANCTRL.OSM), the above conditions

will still exist. However, the TXREQ bit will

be cleared and the message will not

attempt transmission a second time.