Xilinx SMPTESD/HD/3G-SDI3.0 核心设计与实现指南

需积分: 22 98 浏览量

更新于2024-06-30

收藏 1.64MB PDF 举报

"PG071-v-SMPTE-SDI是关于SMPTESD/HD/3G-SDI3.0 LogiCORE IP产品指南的文档,详细介绍了该IP核的功能、规范、设计指导、定制、约束、仿真、综合与实现、示例设计以及测试 bench等重要内容。"

在数字视频领域,SMPTE(Society of Motion Picture and Television Engineers)制定了一系列标准来确保设备之间的互操作性和兼容性。SMPTESD/HD/3G-SDI(Serial Digital Interface)是一种用于传输高质量无压缩视频信号的接口标准,涵盖了标准清晰度(SD)、高清晰度(HD)和3吉比特(3G)速率。这个IP核允许设计者在Xilinx FPGA或SoC中集成这种接口,支持各种视频应用。

1. **概述**:

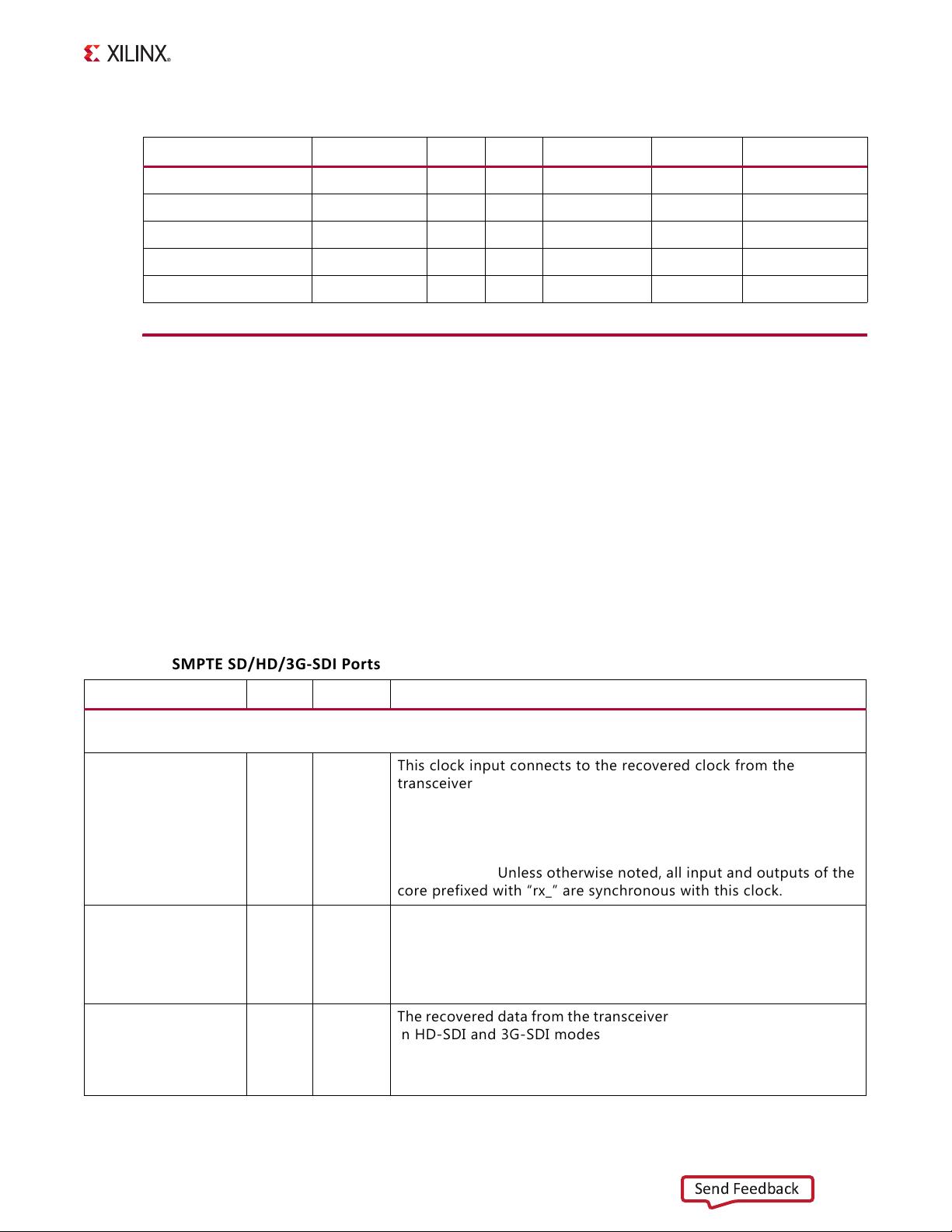

- SMPTE接口标准:描述了SDI的不同规格,如SD-SDI、HD-SDI和3G-SDI,它们分别对应不同的带宽和视频质量。

- 功能概览:提供了IP核的主要特性,包括支持的视频格式、数据速率和同步机制。

- 应用场景:可能包括广播、专业视频制作、视频会议、医疗影像等多个领域。

- 许可:详细说明了IP核的使用许可条件和政策。

2. **产品规格**:

- 标准:详细列出了遵循的SMPTE标准,确保符合业界规范。

- 性能:涵盖了IP核的性能指标,例如数据速率、延迟和错误率。

- 资源利用率:阐述了在不同FPGA或SoC平台上实现该IP核所需的逻辑资源、时钟周期和其他硬件资源。

3. **设计指导**:

- 通用设计准则:提供了在系统设计中集成IP核的最佳实践,包括信号路由、时钟管理等方面。

- 重置:详细说明了IP核的复位机制,如何正确处理复位信号以保持数据完整性。

4. **定制与生成IP核**:

- Vivado集成设计环境:利用Xilinx的Vivado工具进行IP核的配置和生成,包括接口定制、输出生成等步骤。

5. **约束**:

- 必需的约束:列出了为了正确实现和运行IP核必须满足的XDC(Xilinx Design Constraints)文件设置。

- 时钟频率:详细说明了时钟信号的要求,包括主时钟和其他辅助时钟。

6. **仿真**、**综合与实现**和**详细示例设计**章节提供有关验证IP核功能、优化设计流程和理解实际应用场景的指导。

7. **测试bench**:

- 示范测试平台:包含一个用于验证IP核功能和性能的测试平台设计。

8. **附录**:

- 验证、合规性和互操作性:讨论了硬件测试方法,以确保IP核符合SMPTE标准并与其他设备兼容。

- 升级:提供了将设计迁移到Vivado设计套件的指南和在Vivado环境中升级IP核的步骤。

- 调试:指导用户在遇到问题时如何在Xilinx官网上寻找帮助和进行调试。

通过这份PG071文档,设计人员可以获得全面的指导,以有效地在他们的系统中集成和利用SMPTESD/HD/3G-SDI3.0 LogiCORE IP,创建高性能的视频处理解决方案。

2021-04-01 上传

2011-11-17 上传

2021-12-17 上传

2019-05-16 上传

2022-09-24 上传

2019-08-12 上传

2019-08-12 上传

caojian1013

- 粉丝: 0

- 资源: 2

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率