"深入剖析:ASIC芯片综合流程与技术"

需积分: 5 168 浏览量

更新于2024-02-02

收藏 2.07MB PPT 举报

Advanced ASIC chip synthesis is a crucial process in the design and development of application-specific integrated circuits (ASICs). It involves the comprehensive definition and execution of the ASIC design flow, leveraging tools such as Synopsys Design Compiler and technology library to achieve logic synthesis, interface with layout using the LTL, post-layout optimization, and generation of SDF files.

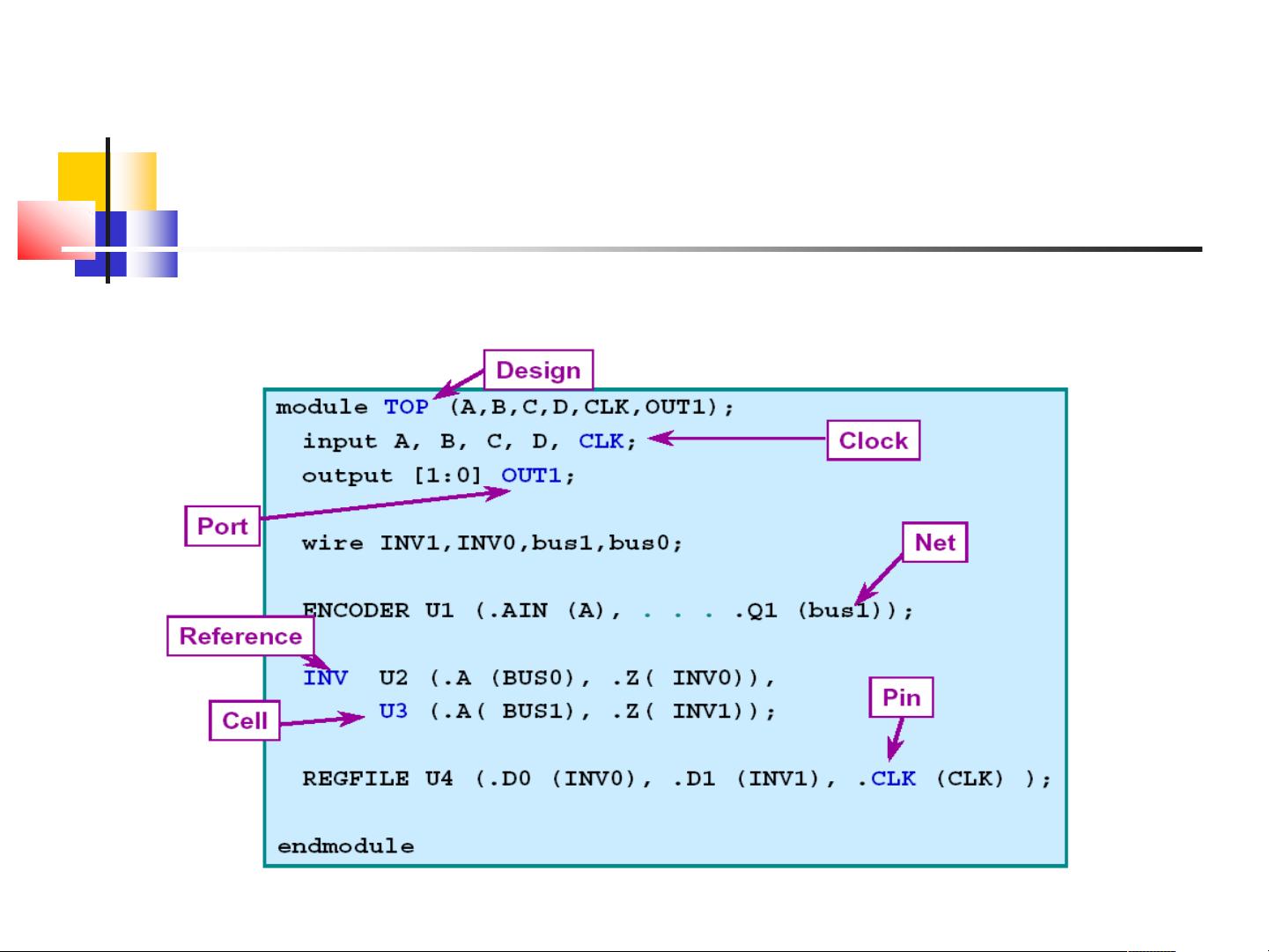

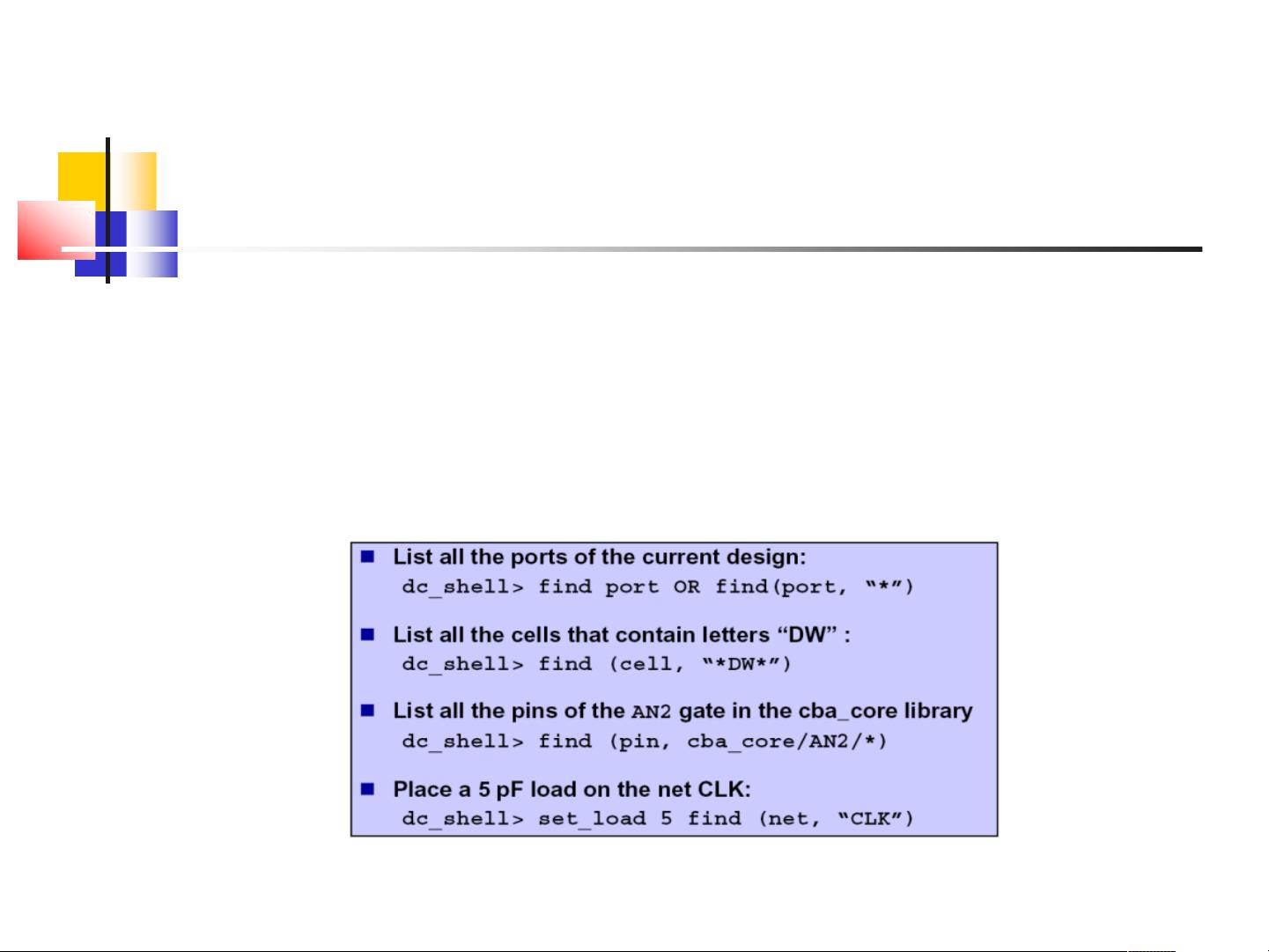

Logic synthesis is a pivotal stage of ASIC chip synthesis, as it determines the interconnection of design circuit logic gates and aims to balance timing, area, and power consumption, as well as enhance circuit testability. The process begins with the analysis of HDL code by synthesis tools, mapping the HDL to a technology-independent model (GTECH). Following this, the designer sequentially undergoes logical optimization and mapping, and gate-level optimization to map the logic to specific target cell libraries, resulting in a synthesized netlist.

Throughout the ASIC design flow, various critical stages are managed, including verified RTL design, constraints, IP and library models, logic synthesis, and ultimately, the synthesis and layout interface using LTL. This comprehensive process culminates in the successful generation of the application-specific integrated circuit, ensuring a balanced and optimized design in terms of logic, timing, area, and power consumption. Tangoblues Advanced ASIC Chip Synthesis provides a detailed and systematic framework for engineers and designers to achieve efficiency and high performance in ASIC development.

274 浏览量

2008-11-26 上传

178 浏览量

294 浏览量

298 浏览量

164 浏览量

157 浏览量

253 浏览量

滕杰

- 粉丝: 8

- 资源: 191

最新资源

- Lotus关于获取URL字符串参数

- jsp数据库经典案例

- 基于LabVIEW步进电机PID控制系统的设计

- GNU映像原理-映像文件及执行机理

- 编程错误中英对照.txt

- 一个智能卡相关的类 PCSC.txt

- CDMA2000系统中的鉴权分析

- Oracle日期时间(Date/Time)操作

- PL/SQL 库程序设计语言介紹

- 什么是RUIM卡,可移动用户识别模块

- 转自名为“来自我心”的博客《中国移动面经、薪酬全攻略》

- 毕业论文—jsp技术实现的系统

- Matlab神经网络工具箱应用介绍

- Office SharePoint Server 2007 规划和基础架构 -2.pdf

- 开源技术选型手册精选版.pdf

- J2EE完全参考手册-J2EE概述-pdf.pdf