DDR3硬件设计与布局:飞思卡尔官方设计指南

版权申诉

本文档《DDR3-硬件设计和Layout设计官方设计参考资料.pdf》是由飞思卡尔提供的官方指南,专注于DDR3 SDRAM内存接口的硬件设计和布局。它旨在帮助系统和板级工程师实现PCB设计的灵活性和高效性,特别是在信号完整性、时序等方面进行精确控制。

文章首先介绍了文档的历史修订记录,强调了设计验证的重要性,推荐在实际制板之前对终端匹配电阻、信号线拓扑和走线长度等关键参数进行仿真优化。飞思卡尔指出,当在DDR与控制器之间使用ODT技术时,可以省去额外的终端匹配电阻,因为ODT本身提供了信号终结功能。

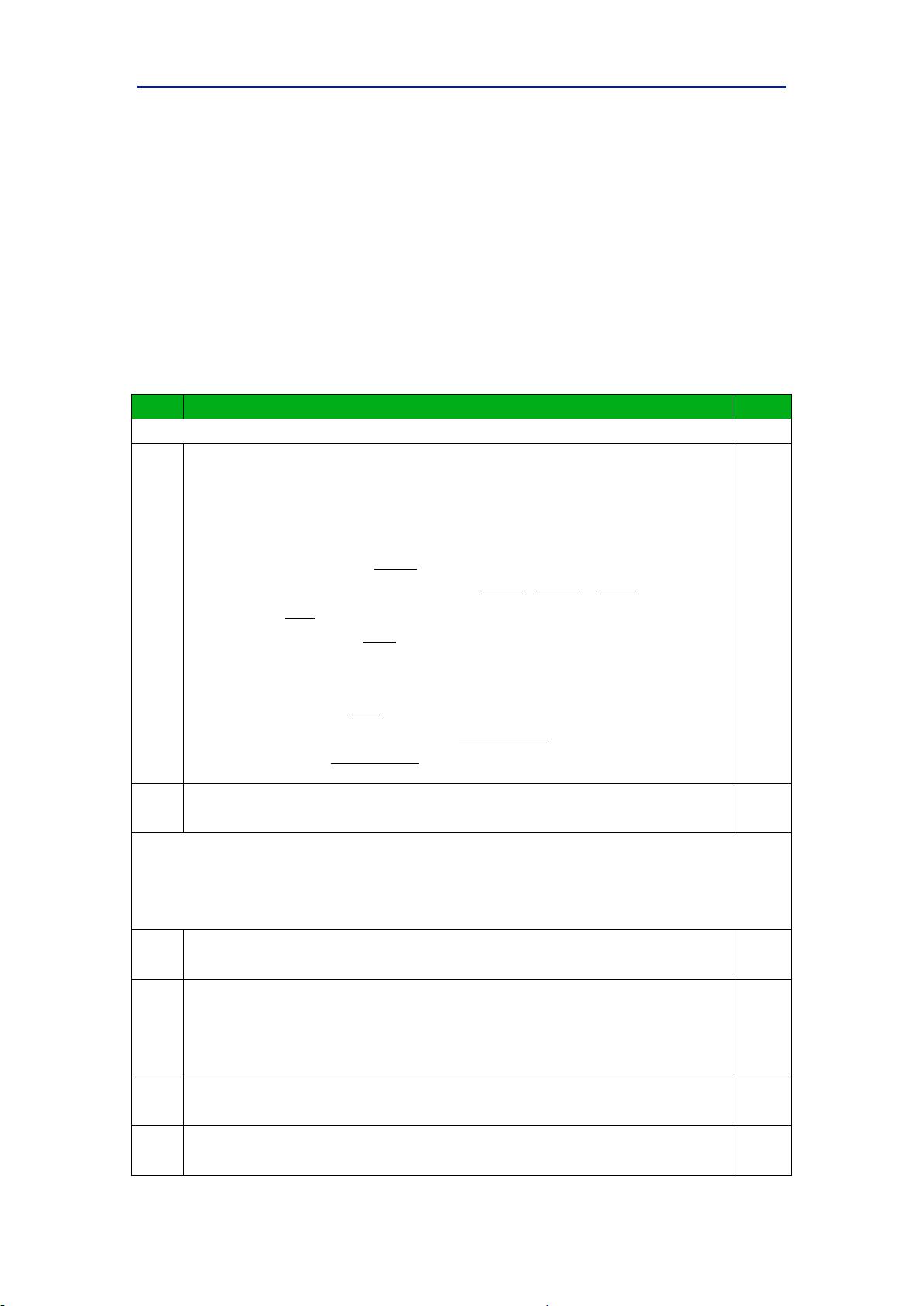

文档详细列出了DDR3设计的检查清单,包括但不限于:

1. **终端匹配电阻**:确保优化了数据线(MDQ[0:63]、MDQS[0:8]、MDM[0:8]、MECC[0:7])的终端匹配电阻值,考虑到AC参数(电平、转换速率、过冲/过载)的要求。

2. **信号线配置**:DDR分组被划分为数据组(包括MDQS、MDM、MDQ和MECC)、地址/命令组(MBA和MA)、控制组(包括控制信号如MCKE和MODT)以及时钟组(MCK)。数据组有72位,其中可能因产品差异而有所不同,比如某些仅支持32位数据线或不完全信号集。

3. **特殊信号处理**:对于某些产品,可能包含支持DIMMs注册的异步信号MAPAR_OUT,需将其归类为地址/命令组。

4. **仿真验证**:强烈建议通过仿真工具来评估设计的完整性和性能,确保所有设计参数符合规范,减少潜在的信号问题。

此外,文档还包含了电源电压轨(VREF和VTT)的设计要点以及DDR布线的具体建议,以及仿真和扩展阅读的相关链接,便于读者深入学习和进一步探索DDR3硬件设计的最佳实践。

这份参考资料是DDR3 SDRAM设计者不可或缺的工具,提供了全面且实用的设计指南,帮助工程师在实际工作中实现高效、稳定和兼容的PCB设计。

140 浏览量

768 浏览量

239 浏览量

103 浏览量

184 浏览量

230 浏览量

185 浏览量

175 浏览量

GJZGRB

- 粉丝: 2975

最新资源

- Windows DOS命令详解:8个网络操作必备工具

- MPEG-4:新一代视听多媒体标准白皮书

- NC50账务处理:集团企业财务管理全方位解析

- Oracle Data Integrator:统一企业数据集成的全能平台

- Oracle数据库常用函数详解

- Tomcat基础配置详解:从安装到环境配置

- Java JDK详设与安装测试指南

- Java多态性详解:动态行为与实现机制

- 使用Flash技术模拟神舟六号发射动画设计

- ASP技术实现的用户注册登录系统设计与安全

- ETL自动化工具2.6.0中文使用手册

- InfoQ中文版《深入浅出Struts2》免费在线阅读

- VB技术驱动的电脑销售管理系统优化与应用

- Struts快速入门与MVC架构详解

- Perl编程速成指南:初学者入门必备

- Domino E50喷码机操作指南