边沿D触发器详解:电路结构与工作原理

需积分: 50 53 浏览量

更新于2024-09-09

1

收藏 76KB DOC 举报

本文主要介绍了D触发器的原理和电路结构,特别关注了边沿D触发器的工作方式,包括其如何抵抗干扰、电路内部的逻辑功能以及触发器的状态转换。

D触发器是一种基本的数字逻辑电路,常用于存储数据或作为其他数字系统中的时序电路的一部分。它具有一个数据输入端D和两个互补输出端Q和Q'。D触发器的主要特点是其状态只在时钟脉冲的边缘(通常是上升沿或下降沿)改变,从而提高了抗干扰性能和工作速度。

边沿D触发器,也称为维持-阻塞边沿D触发器,其工作原理在于允许在时钟脉冲的边缘到来之前稳定输入信号D。这样,即使在时钟脉冲期间输入端受到干扰,也不会影响触发器的当前状态,因为输入信号在时钟脉冲到来前已经确定。这种设计显著减少了错误触发的可能性。

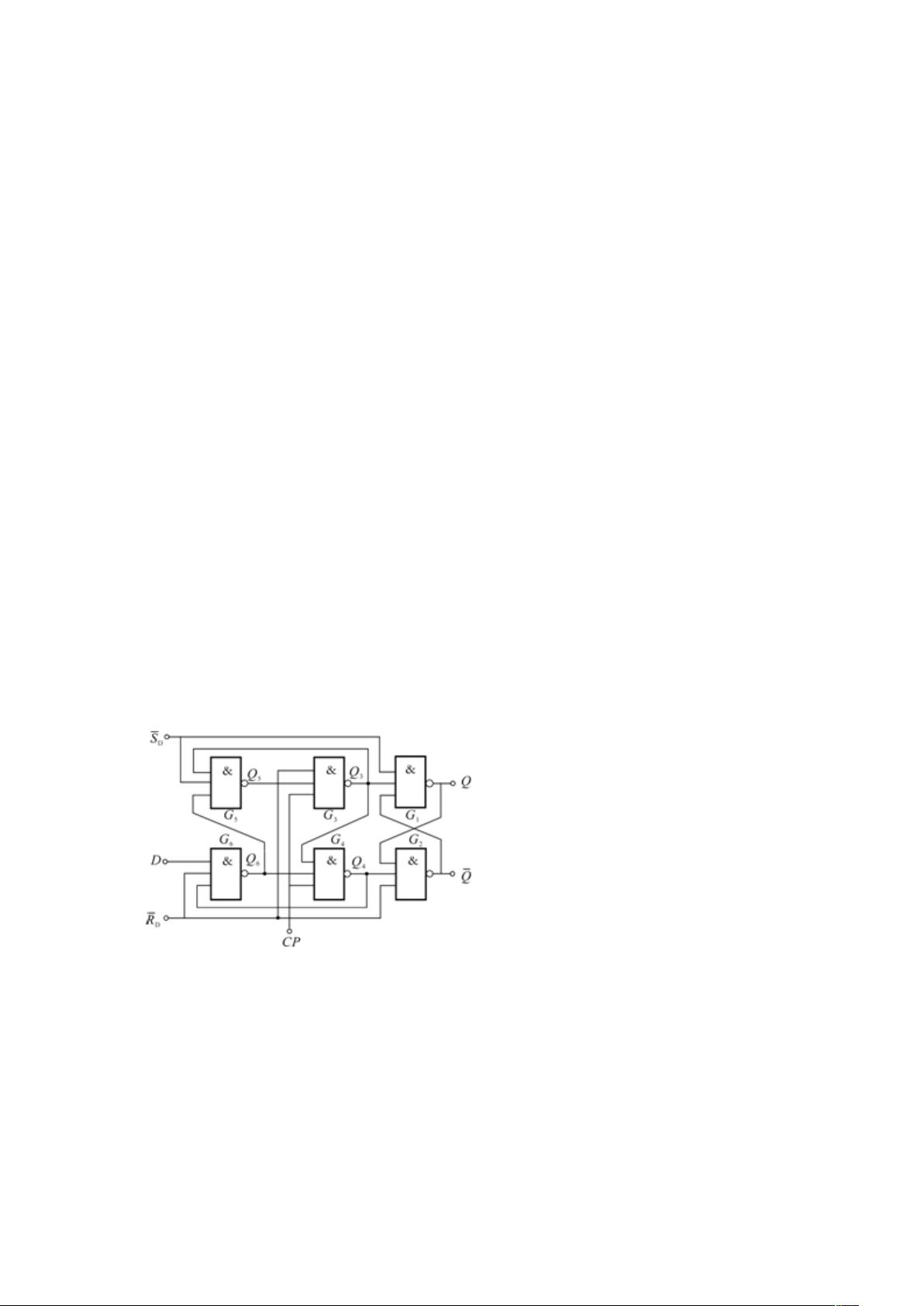

电路结构上,边沿D触发器通常由多个与非门(如G1到G6)组成,其中G1和G2构成了基本的RS触发器。在这个电路中,SD和RD是预置和清零端,它们分别通过低电平有效来设置触发器为1或0状态。在正常操作中,这些端口通常被拉高,以不影响电路的工作。

工作流程如下:

1. 当时钟CP为0时,与非门G3和G4关闭,保持触发器的当前状态不变,并允许新的输入D进入。

2. CP上升沿到来时,G3和G4打开,根据输入D和前一状态Q,更新输出Q和Q'。基本RS触发器的逻辑使得Q在下一个时钟周期结束时等于D。

3. 在CP为1期间,输入D被封锁,防止在时钟脉冲的高电平期间任何变化影响输出。这种封锁机制是由G3和G4的互补输出实现的,它们提供了维持和阻塞功能,确保触发器在时钟脉冲后的状态保持稳定。

D触发器的特征方程为Qn+1=D,表明在下一个时钟沿,输出Q将等于当前输入D的值。状态转移图显示了D触发器在不同输入D和时钟CP条件下,输出Q的变化情况。脉冲特性通常包括建立时间和保持时间,它们定义了时钟边沿前后输入D必须稳定的时间窗口,以保证正确触发。

边沿D触发器因其优秀的抗干扰能力和高速工作性能,广泛应用于各种数字系统中,如计数器、移位寄存器和序列发生器等。与主从触发器相比,边沿D触发器在相同工艺下通常具有更优的性能。

362 浏览量

622 浏览量

点击了解资源详情

137 浏览量

3366 浏览量

3464 浏览量

点击了解资源详情

点击了解资源详情

306 浏览量

zheng_zeyu

- 粉丝: 2

最新资源

- Laravel框架下分配注册客户票据的App应用

- ASP影片租赁管理系统源代码与论文资料包

- TC358743XBG详细技术文档与应用资料解析

- VectorCalculator: 掌握Android矢量计算的神器

- Android平台的libevent库调试与实践

- VueScan图像扫描软件v9.6.14新版发布,性能升级!

- 鲁大师电脑温度测量工具:CPU、显卡、硬盘和内存

- ASP技术构建的商场管理系统设计与实现详解

- RegLinker:正则表达式优化蛋白质网络交互研究

- React App 开发入门与构建指南

- ASP二手电子产品交易网站源代码及论文详解

- PSP平台上的Lua自制游戏:路易吉世界的开发与兼容性

- 解决ORA-39405错误的Oracle 19.3时区版本33补丁发布

- PHP开发的新闻内容管理系统与数据导入指南

- 深入理解基于Java的Tomcat服务器技术

- CAML Designer 2013:SharePoint开发者的代码生成利器