CMOS反相器:电压传输特性与噪声容限分析

需积分: 50 47 浏览量

更新于2024-07-16

收藏 1.1MB PDF 举报

"第5章(课件)CMOS反相器2004年9月29日.pdf"

本课件主要讲述了关于CMOS反相器的理论和特性,重点关注了电压传输特性、噪声容限以及逻辑门的基本要求。CMOS反相器是数字集成电路的基础单元,其性能直接影响整个集成电路的性能和可靠性。

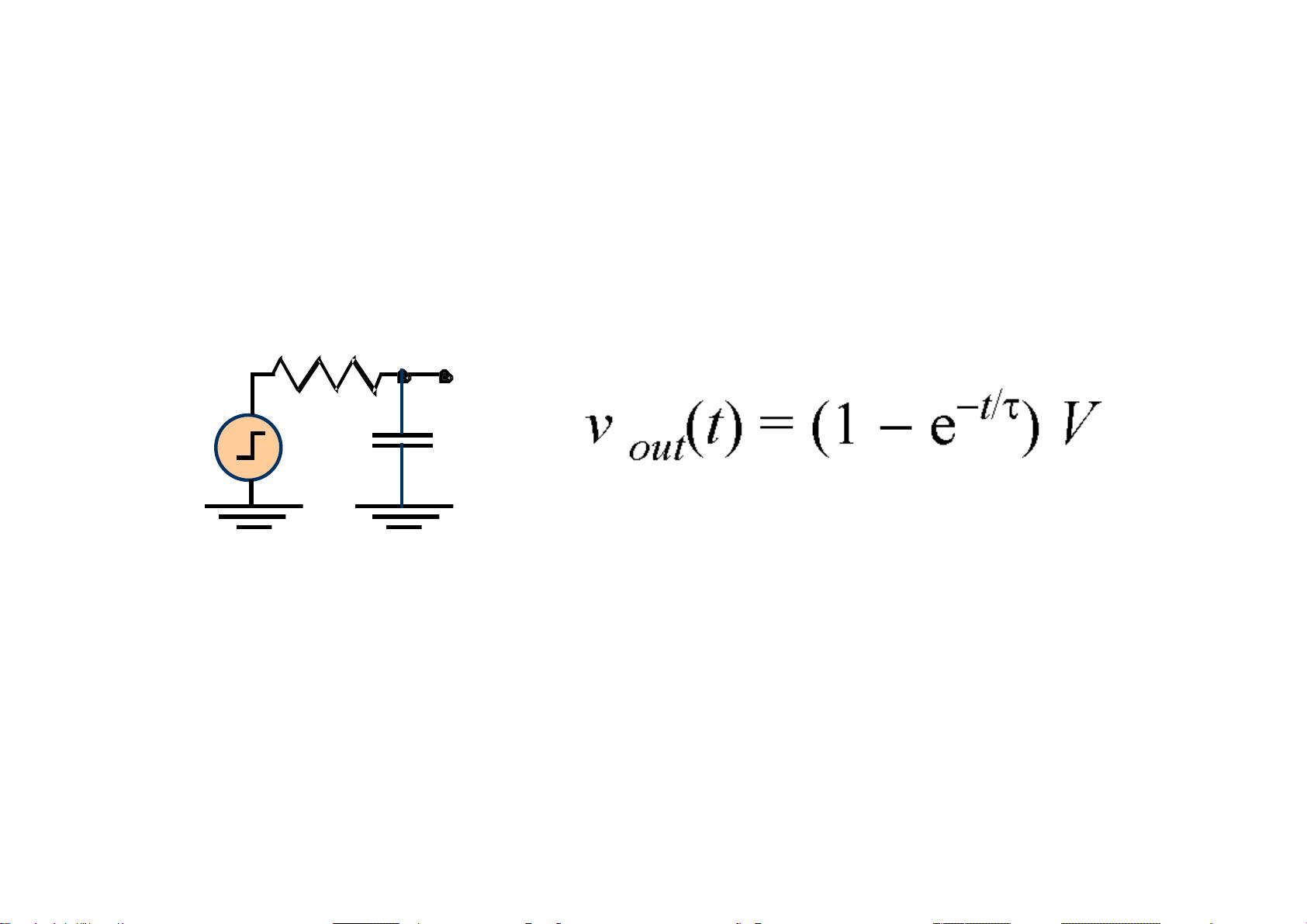

首先,电压传输特性(VTC)是衡量CMOS反相器静态特性的关键指标。VTC展示了输出电压VOH(高电平)与VOL(低电平)与输入电压Vx之间的关系。在理想的VTC曲线中,VOH随Vx增加而增加,VOL随Vx减小而减小,且存在一个中间点VM,称为开关阈值电压。这个阈值电压决定了反相器的转换点,当输入电压超过此阈值时,输出状态会发生翻转。

课程中提到了鲁棒性这一概念,这是数字集成电路的一个基本要求,意味着电路应具有良好的静态特性,即使在制造过程中存在偏差,也能保证功能的正常实现。电压传输特性上的特征点如VIL(输入低电平)、VIH(输入高电平)、VOL和VOH定义了逻辑门的工作区间。噪声容限(Noise Margin)是衡量电路抗噪声能力的重要参数,包括高电平噪声容限NMH和低电平噪声容限NML,它们分别定义了在保持逻辑状态不变的情况下,输入可以承受的噪声范围。

噪声是数字集成电路中的一大挑战,它可能来源于串扰、电源与地线噪声、干扰以及失调等。设计时需要考虑这些噪声源,并分配总的噪声容限以确保电路在各种噪声环境下仍能正常工作。浮空节点相对于有低阻抗电压源驱动的节点更容易受到噪声影响。噪声容限定义了在不引起逻辑错误的情况下,输入和输出允许的最大噪声幅度。

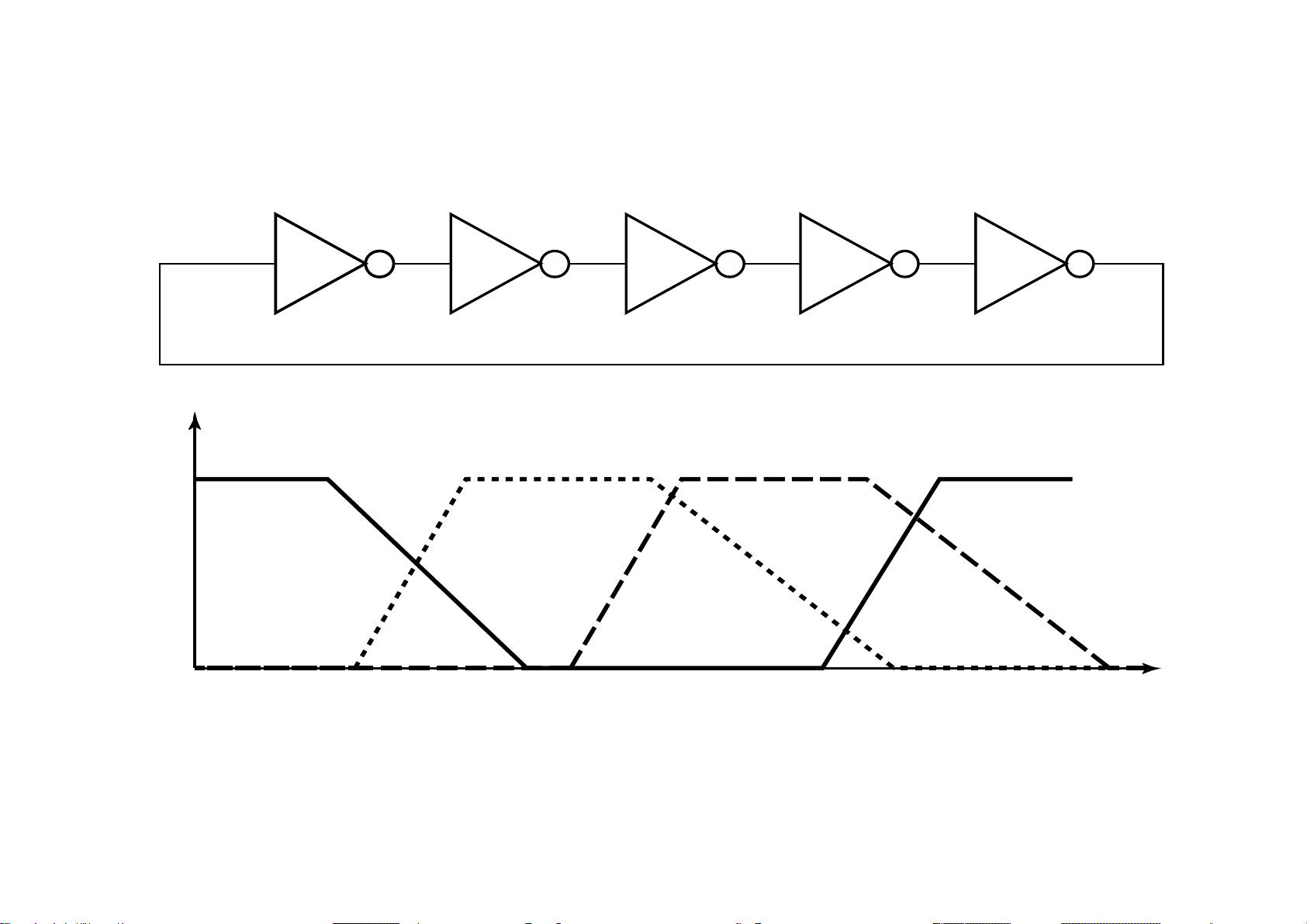

理想逻辑门被假设为输入电阻无穷大(Ri=∞),输出电阻为零(Ro=0),扇出无限大(Fanout=∞),并且高电平和低电平噪声容限相等(NMH=NML=VDD/2)。然而,实际中的逻辑门无法达到这些理想条件,例如早期的逻辑门可能会表现出非理想的噪声容限分布,如图所示。

理解和优化CMOS反相器的电压传输特性和噪声容限对于设计高效、可靠的数字集成电路至关重要。这包括选择合适的阈值电压、提高噪声免疫能力和确保电路的鲁棒性。在实际设计中,需要综合考虑工艺参数、功耗、速度和面积等多方面因素,以实现最佳的性能和稳定性。

1429 浏览量

2459 浏览量

2021-09-02 上传

105 浏览量

573 浏览量

134 浏览量

559 浏览量

壹零捌

- 粉丝: 226

- 资源: 101

最新资源

- python-3.4.4

- elemental-lowcode:元素低码开发平台

- Logger:记录工具

- SheCodes-WeatherApp:挑战3

- 阿宾贝夫前端测试

- 银灿IS917U盘PCB电路(原理图+PCB图)-其它其他资源

- registry-url:获取设置的npm注册表URL

- ST-link驱动.rar

- keen-gem-example:一个 Sinatra 应用程序,使用敏锐的 gem 异步发布事件

- 行业分类-设备装置-一种抗菌纸.zip

- Pearl-Hacks-2021:线框的htmlcss骨架

- a2s-rs:源代码查询的Rust实现

- DotFiles:我的Dotfiles <3

- Magisk Manager-20.1.zip

- ScheduleReboot:此实用程序用于在特定时间重新引导计算机,解决了在目标时间内处于睡眠模式的计算机在唤醒后实施重新引导的问题。

- Online-Face-Recognition-and-Authentication:Hsin-Rung Chou、Jia-Hong Lee、Yi-Ming Chan 和 Chu-Song Chen,“用于人脸识别和认证的数据特定自适应阈值”,IEEE 多媒体信息处理和检索国际会议,MIPR 2019