优化高性能ADC性能:差分驱动器的应用与分析

下载需积分: 9 | PDF格式 | 533KB |

更新于2024-09-08

| 156 浏览量 | 举报

"MT-074:精密ADC用差分驱动器.pdf"

ADC(Analog-to-Digital Converter,模拟到数字转换器)是电子系统中的核心组件,它负责将连续的模拟信号转换为离散的数字信号。在高精度和高速度的应用中,全差分ADC因其卓越的共模抑制能力、较低的二阶失真和简便的直流校准而受到青睐。差分驱动器在这样的ADC前端扮演着至关重要的角色,尤其当需要扩展频率响应至直流或处理宽广输入信号带宽时。

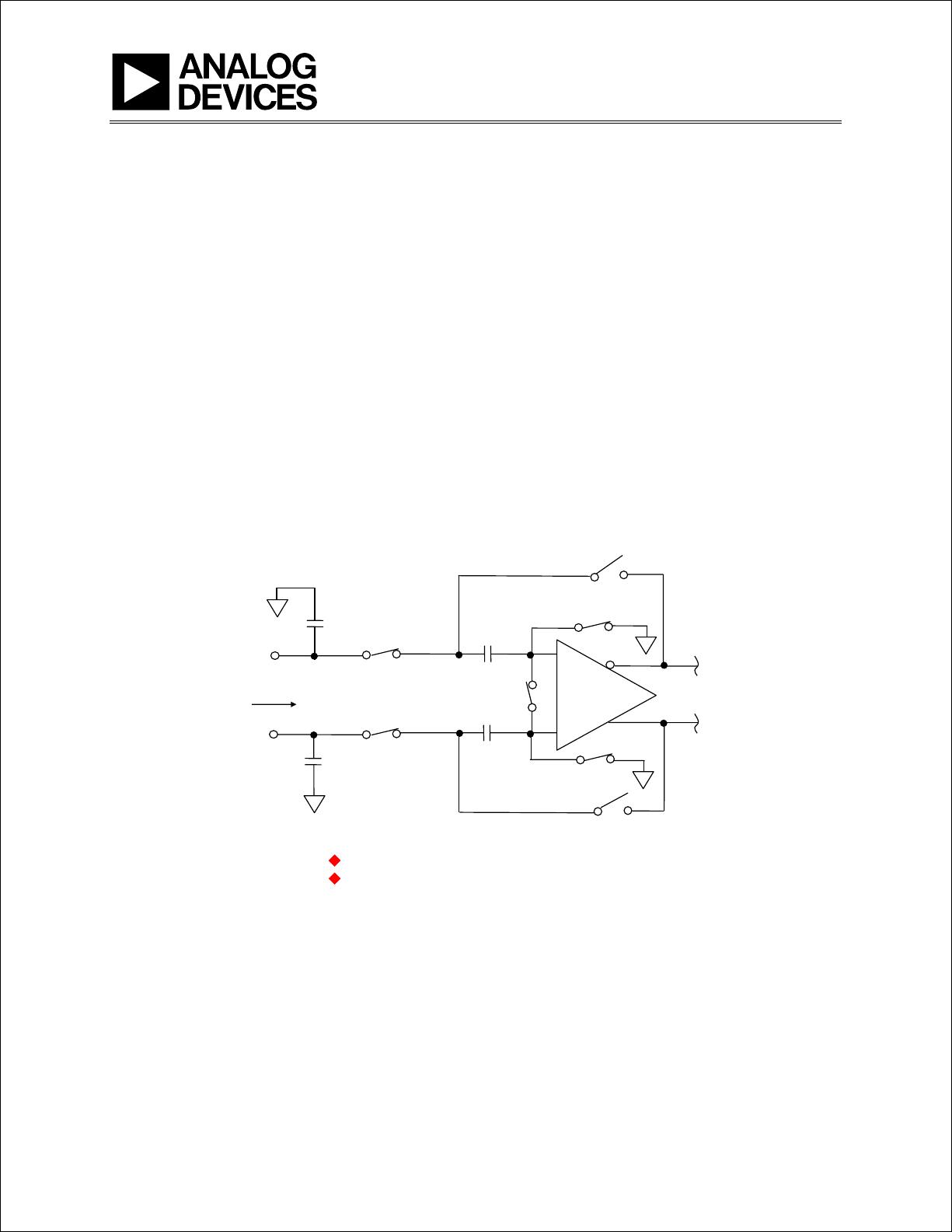

差分输入ADC的设计主要优势在于其能够有效抑制共模噪声,这是因为它们能捕获信号的相对变化而非绝对水平。图1展示了一个典型的非缓冲开关电容CMOS采样保持输入电路,这是许多高性能ADC的常见结构。这种差分配置简化了匹配要求,减少了谐波失真,并有助于提高信噪比。

差分驱动器的任务是为ADC提供对称且精确的差分信号,以确保准确的采样。在驱动高分辨率(如16至18位)和高速(如10MSPS)的ADC时,输入信号的带宽通常限制在几兆赫兹。驱动器需要在跟踪模式下跟随输入信号的变化,并在保持模式下维持稳定电压,以便ADC进行采样。选择合适的驱动器时,要考虑其输入阻抗、输出驱动能力、上升/下降时间以及与ADC的匹配程度。

MT-074教程主要探讨了如何有效地驱动这种类型的ADC,强调在直流到高频范围内的性能。同时,文档指出,差分充电瞬变是关于中间标度的对称,并由线性成分主导,这在保持共模瞬变最小化方面非常重要。理想的差分驱动器应提供相等的源阻抗,以实现共模瞬变的相互抵消。

在实际应用中,采样时钟同步和开关的布局也对系统的整体性能至关重要。SHA(Sample-and-Hold Amplifier,采样保持放大器)的开关直接连接到每个输入通道,确保在采样期间正确捕获信号。采样时钟的上升沿和下降沿需要精确控制,以避免引入不必要的噪声或失真。

MT-075教程进一步讨论了用于驱动更高速度ADC的差分放大器,这意味着随着ADC采样速率的增加,驱动器需要处理更高的信号带宽和更快的转换速率,这需要更高级的驱动技术,包括更快速的开关和更低的输出电容。

选择和设计适合的差分驱动器对于实现高精度和高速ADC系统的性能至关重要。设计者需要考虑ADC的特性,如采样速率、分辨率和输入带宽,以及驱动器的动态性能、电源抑制比、共模抑制比等参数,以确保整个系统的一致性和可靠性。

相关推荐

jing918

- 粉丝: 0

最新资源

- 昆仑通态MCGS嵌入版_XMTJ温度巡检仪软件包解压教程

- MultiBaC:掌握单次与多次组批处理校正技术

- 俄罗斯方块C/C++源代码及开发环境文件分享

- 打造Android跳动频谱显示应用

- VC++实现图片处理的小波变换方法

- 商城产品图片放大镜效果的实现与用户体验提升

- 全新发布:jQuery EasyUI 1.5.5中文API及开发工具包

- MATLAB卡尔曼滤波运动目标检测源代码及数据集

- DoxiePHP:一个PHP开发者的辅助工具

- 200mW 6MHz小功率调幅发射机设计与仿真

- SSD7课程练习10答案解析

- 机器人原理的MATLAB仿真实现

- Chromium 80.0.3958.0版本发布,Chrome工程版新功能体验

- Python实现的贵金属追踪工具Goldbug介绍

- Silverlight开源文件上传工具应用与介绍

- 简化瀑布流组件实现与应用示例