MSP430F5529开发板电路解析:TI官方设计

需积分: 21 122 浏览量

更新于2024-08-04

收藏 111KB PDF 举报

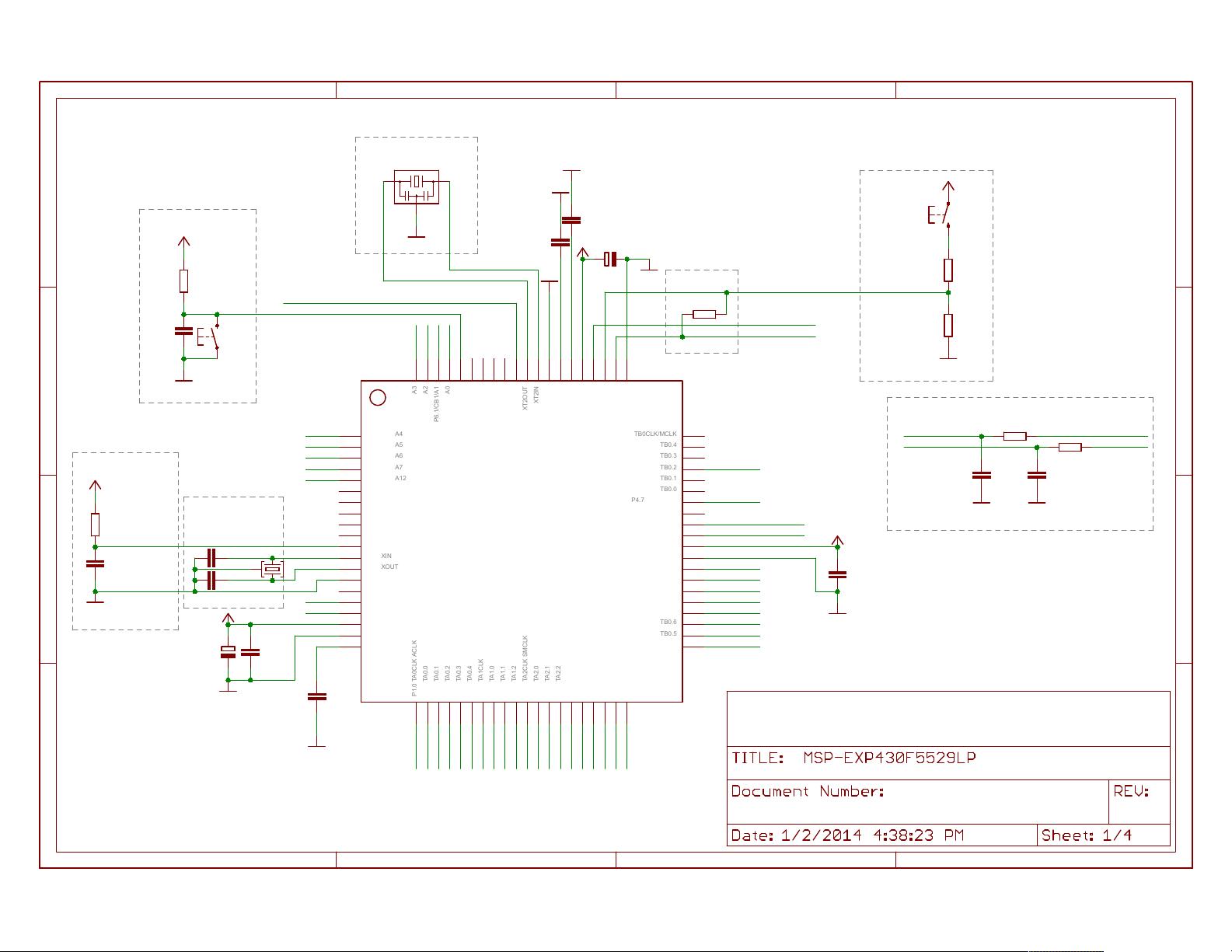

"TI官方MSP430F5529开发板的原理图涉及到微控制器、电源管理、时钟系统、调试接口以及GPIO端口的配置。"

TI的MSP430F5529是一款低功耗、高性能的16位微控制器,适用于各种嵌入式应用。该开发板的原理图展示了如何将这个芯片连接到外围电路,以实现完整的功能。

1. **微控制器单元**:

MSP430F5529是主要的处理核心,提供丰富的数字输入输出(I/O)引脚和多种外设接口。例如,S3可能是用于编程或调试的串行通信接口,而TEST/SBWTCK可能是指令时钟输入,用于内置串行背景调试系统(BSL)。

2. **电源管理**:

开发板支持+3V3和+5V电源轨,用于供电不同的电路模块。例如,VUSB和VBUS可能用于连接USB设备,V18可能是辅助电源。同时,板上可能有电源管理电路,如去耦电容C14, C15, C16等,以确保稳定的工作电压。

3. **时钟系统**:

设计中包括了晶体振荡器(如P5.3/XT2OUT和P5.2/XT2IN)以产生精确的时钟信号。XT2可能是外部晶体振荡器,用于提供高速时钟,而LFXTCLK可能是一个低频晶体,用于节能模式下的操作。主时钟MCLK可能由这些振荡器或其他内部时钟源生成。

4. **调试接口**:

BSL(串行背景调试系统)允许通过GND、1k4电阻和1M欧姆电阻进行编程和调试。BSL Speed表示调试速度,可能用于控制调试速率。RST/NMI/SBWTDIO是复位/非中断请求/BSL数据输入/输出引脚,用于调试和系统管理。

5. **模拟电源与接地**:

Analog VCC可能为模拟电路供电,C17, C18, C19等电容用作模拟电源的去耦,以降低噪声影响。

6. **GPIO端口**:

P6.3到P6.0、P7.7到P7.4、P5.7到P5.0等是通用I/O端口,可以配置为输入或输出,用于连接各种外设。例如,P4.3到P4.0可能用于I2C或SPI通信,而P1.0到P1.3则可能作为定时器输入或输出。

7. **其他功能**:

清单中的某些引脚如P3.7/TB0OUTH/SVMOUT和P4.6/PM_NONE可能是定时器输出或特定外设的专用引脚。还有PJ.x (4) 表示PJ端口的四个引脚可自由配置。

8. **电容和电阻**:

电容如100n, 220n, 470n等用作滤波和去耦,电阻如100R, 1k4, 27R等在电路中起分压、限流或匹配阻抗的作用。12p和10p电容可能是晶振的负载电容,确保其正常工作。

9. **重置功能**:

RST引脚是复位信号,可能通过100n电容和10u电容网络实现上电复位或软件复位功能。

这个开发板原理图详细描述了如何构建一个基于MSP430F5529的系统,包括电源、时钟、调试、I/O和模拟电路的配置,为开发者提供了清晰的硬件平台,方便进行项目开发和实验。

2576 浏览量

1145 浏览量

2012-03-12 上传

2012-07-02 上传

117 浏览量

123 浏览量

169 浏览量

1145 浏览量

657 浏览量

风正豪

- 粉丝: 4w+

- 资源: 9

最新资源

- DirectX93D游戏程序设计入门.doc

- java调用存储过程实例

- EXTJS简明中文教程

- BluePage通用分页类助开发者提高开发效率5

- BluePage通用分页类助开发者提高开发效率4

- Head+First+C#+中文版+图文皆译+第三章+翻译完毕+PDF下载.pdf

- BluePage通用分页类助开发者提高开发效率2

- 学习教程\C语言程序设计

- BluePage通用分页类助开发者提高开发效率1

- 如何使用PHP中的字符串函数

- phpMyAdmin2.6以上版本数据乱码问题

- 轻松实现php代码防注入,保护代码安全

- ObjectARX开发实例教程-20070715.pdf

- C语言嵌入式系统编程

- CAS 协议 票据、url介绍,包括cas1.0和cas2.0

- PHP中的代码安全和SQL Injection防范4