CD4046锁相环频率合成器设计与实现

版权申诉

“基于CD4046锁相环频率合成器设计”

本文主要探讨了如何利用CD4046芯片设计一个锁相环频率合成器,该设备在通信、雷达、测控和仪表等领域有着广泛应用。锁相频率合成器虽然在频率转换时间和分辨率上可能不及直接式和直接数字式频率合成器,但其结构简洁、成本较低,并能提供与前两者相当的输出频率精度。

在设计过程中,作者提到了几个关键的技术环节:

1. **设计和制作任务**:这包括明确设计目标,例如确定所需的输出频率范围、频率稳定性和转换速度等。

2. **主要技术指标**:这些指标可能包括锁相环的锁定时间、输出频率的线性范围、噪声性能和频率分辨率等。

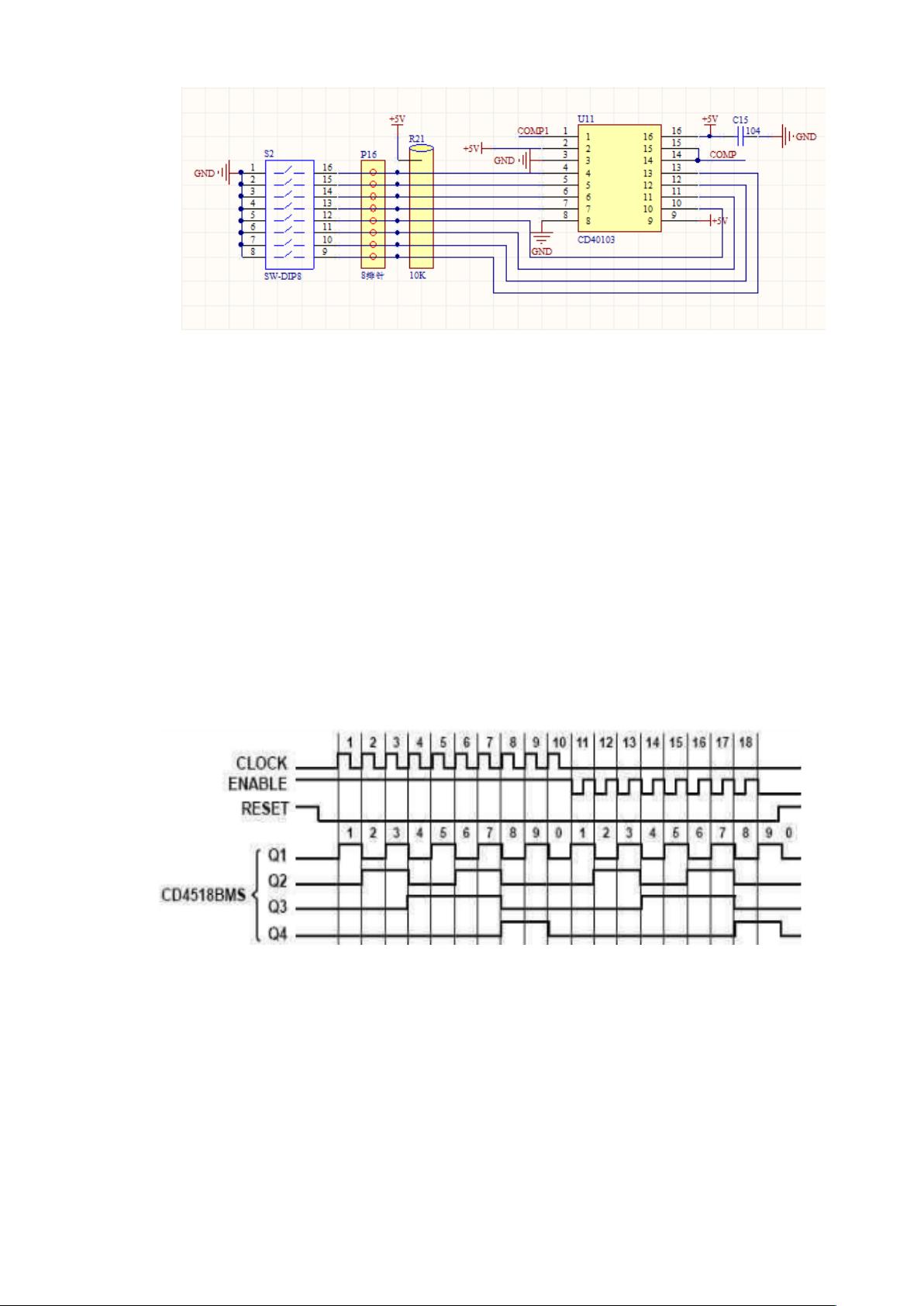

3. **电路设计方案**:振荡源是频率合成器的基础,通常需要具有良好的频率稳定性和可调性。文中提到了几种分频方案,如BCD码减法计数器CD4522,单片机编程分频,以及减法计数器CD40103。不同的分频方案会影响系统的灵活性和复杂性。

4. **0.1KHZ标准信号源设计**:这是为了确保输出频率的精确性,通过特定的分频器设计来实现。

5. **锁相环参数设计**:锁相环由鉴相器、环路滤波器和压控振荡器组成。文中介绍了锁相环的工作原理,即通过比较输入参考信号与环路内部产生的信号之间的相位差,调整压控振荡器的频率,使得两信号的相位保持一致。

6. **电路板制作**:这部分涉及PCB布局和布线,以确保信号的纯净和系统的稳定性。

7. **电路调试**:调试阶段是验证设计是否符合预期,包括检查各个部分的功能,确保锁定状态,以及测试频率输出的准确性和稳定性。

8. **心得体会**:作者分享了实验过程中的体验和学习成果,提供了个人对设计和实现过程的理解。

9. **缺陷与不足**:这一部分分析了设计中存在的问题和可以改进的地方,对于未来优化设计具有指导意义。

10. **参考文献**和**附录**:提供了进一步的研究资料和具体实现的代码或硬件细节。

本文详尽地阐述了基于CD4046的锁相环频率合成器的设计过程,从理论到实践,从电路设计到实际操作,全面覆盖了各个环节,对于理解和构建此类系统具有很高的参考价值。

543 浏览量

244 浏览量

153 浏览量

2024-11-04 上传

2024-11-03 上传

2024-11-10 上传

老帽爬新坡

- 粉丝: 98

- 资源: 2万+

最新资源

- 行业文档-设计装置-一种带语音录入和播放功能的历史教具.zip

- rp-study.github.io:ACM IMC 2020论文“关于衡量RPKI依赖方”

- data_preprocessing:使用Pandas,Numpy,Tensorflow,KoNLPy,Scikit Learn进行数据预处理的方法

- First-android-app:那是我的第一个android应用。 它基于Google的教程

- redhat离线静默安装oracle11g资源

- MinecraftVirus:这是由GamerFiveYT制造的病毒

- spring boot动态多数据源demo

- R代表数据科学

- x86_64-支持x86_64特定的指令,寄存器和结构-Rust开发

- contact-functions

- 行业文档-设计装置-一种具有储冷功能的平行流蒸发器芯体.zip

- TinyMCE(可视化HTML编辑器) v5.0.4

- dusty:玩具多线程沙“游戏”

- Space Invaders Remake-开源

- hello-python-project:从头开始探索CLI工具的PyPI打包

- 欧姆食品