Quartus RAM-Based移位寄存器IP核用户指南

需积分: 0 76 浏览量

更新于2024-07-15

收藏 1.2MB PDF 举报

"Quartus基于ram的移位寄存器源文档"

Quartus基于RAM的移位寄存器(ALTSHIFT_TAPS)IP核用户指南详细介绍了如何在FPGA/CPLD设计中使用这种高效的存储元件。该文档是针对Altera Complete Design Suite版本14.0a10编写的,更新日期为2014年8月。Altera公司,位于101 Innovation Drive, San Jose, CA 95134,是提供此技术文档的机构。

移位寄存器是一种数字电路,能够根据时钟信号将输入数据逐位向左或向右移动。在基于RAM的实现中,移位寄存器利用片上内存资源来存储数据,从而提供高速、灵活的移位操作。这对于处理串行数据传输、并行到串行转换、串行到并行转换以及各种数据处理应用非常有用。

ALTSHIFT_TAPS IP核是Altera FPGA和CPLD设计中的一个重要组件,它允许用户自定义移位寄存器的特性,如移位方向、数据宽度、深度和预加载数据的能力。用户可以根据设计需求配置这些参数,以优化性能和资源利用率。

该用户指南可能包含以下内容:

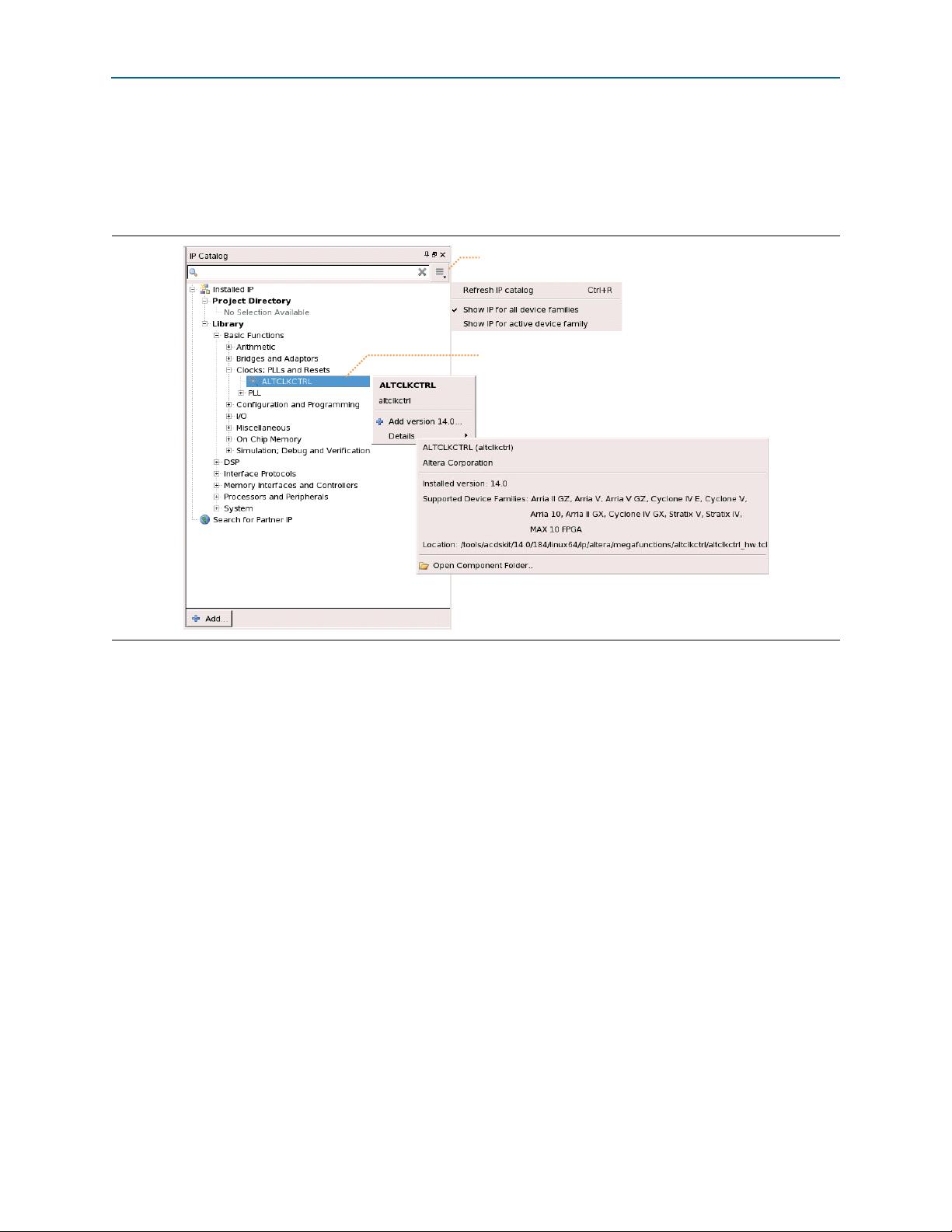

1. **IP核配置**:详细说明如何在Quartus集成开发环境中配置ALTSHIFT_TAPS IP核,包括选择合适的内存类型、设定移位方向、设置移位长度等。

2. **接口说明**:定义了IP核与用户逻辑之间的接口信号,如数据输入(Data In)、数据输出(Data Out)、移位时钟(Shift Clock)和控制信号(如Load、Clear等)。

3. **性能评估**:指导用户如何评估IP核的性能,包括时序分析、功耗计算和资源占用情况。

4. **例程和应用示例**:提供实际设计示例,演示如何在实际工程中使用该IP核,可能包括系统级设计和综合。

5. **约束文件和VHDL/Verilog代码**:提供必要的硬件描述语言代码模板和约束文件,帮助用户在设计中集成IP核。

6. **故障排查和调试**:提供了一些常见问题的解决方案和调试技巧,以帮助用户解决设计过程中遇到的问题。

此外,文档还强调了Altera对半导体产品的性能保证,遵循其标准保修政策,并提醒用户,尽管Altera会持续改进产品和服务,但不承担因应用或使用任何信息、产品或服务而产生的责任或赔偿。

总结来说,"Quartus基于ram的移位寄存器源文档"是针对Altera FPGA和CPLD设计者的一份关键参考资料,涵盖了基于RAM的移位寄存器IP核的配置、使用和优化,是实现高效、灵活数字系统设计的重要工具。

139 浏览量

806 浏览量

1965 浏览量

2024-11-11 上传

1047 浏览量

541 浏览量

133 浏览量

406 浏览量

learn_huang

- 粉丝: 4

- 资源: 1