华为内部大规模逻辑设计指南:Verilog与VHDL编程实践

需积分: 32 118 浏览量

更新于2024-07-25

收藏 3.45MB PDF 举报

"华为大规模逻辑设计指导书是一份详尽阐述逻辑设计方法和Verilog编码规范的内部参考资料,适用于FPGA开发。这份140页的文档由华为研究管理部文档中心编纂,旨在帮助工程师理解和掌握高效、高质量的逻辑设计技巧。"

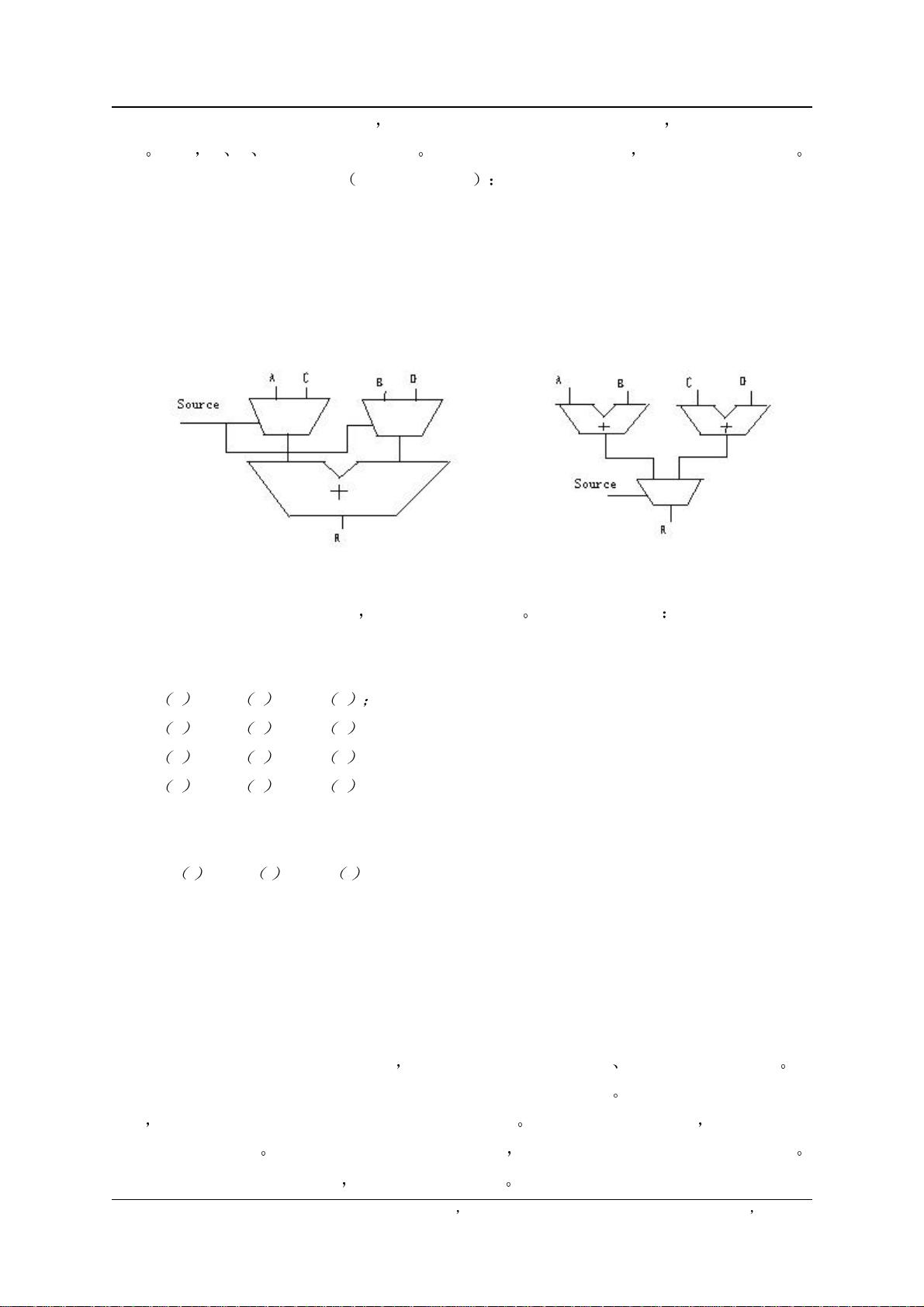

文档主要分为多个章节,覆盖了从设计的基本原则到具体的编程实践。在"第一篇方法论"中,它强调了选择有意义的信号和变量名的重要性,这些命名应能反映信号或变量的来源和状态,有助于提高代码的可读性和可维护性。此外,文档还涵盖了Verilog编码风格,包括5.1节中的各种编码建议,如使用`if`语句、`case`语句、函数、组合逻辑与时序逻辑的区分,以及如何避免使用可能引发问题的结构,如latch。

文档还深入探讨了VHDL语言的编写范例,包括保留字的使用、函数和程序包的书写实例,这些都是进行复杂逻辑设计的基础。此外,还提到了代码模块划分的原则,这是实现可重用和可扩展设计的关键。文档特别指出,应该注意代码编写中可能出现的问题,如使用FSM(有限状态机)时的陷阱,以及如何有效地处理资源分享和多赋值语句。

在优化设计方面,文档提到了考虑综合的执行时间和避免使用可能导致不确定性的latch。它还讨论了组合逻辑的不同描述方式,以及如何通过资源共享来提高设计效率。文档的附录部分提供了更多的参考资料和实例,以供读者深入学习和实践。

总结起来,这份华为的大规模逻辑设计指导书是一份全面的教程,适合于希望提升FPGA设计能力的工程师,通过遵循其中的指导,可以编写出更高效、更易于理解的逻辑设计代码。

133 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

102 浏览量

2010-03-29 上传

芯片验证日记作者

- 粉丝: 8

最新资源

- 掌握Android ExoPlayer实现高效视频播放

- 科技企业商务PPT模板设计

- C#实现CRC校验工具:源码学习与应用

- WPF中实现CallOut箭头指向鼠标点击位置的方法

- 开发devtwitter模块:Linux下的Twitter驱动实现

- A4纸张排版神器:PrintDocPlus打印模板工具

- 自定义化Bootstrap 3:快速集成与页面展示

- So Sánh Các Sở不定詞 Hoc Edumall, Unica, Kyna 使用 CRX 插件

- 全面介绍Visio 2000的中文学习教程PDF

- 工艺生产PPT模板:针线手工活设计资源

- 网名大汇总:Excel文件里找创意昵称

- Kotlin实现协程友好型Android Debug Bridge客户端

- 易语言实现获取电脑历史登录QQ号的方法

- 家谱先生7.1:宗谱制作软件,便捷电子化与纸质化

- 多种图像去噪算法及其实现原理详解

- MQ-2气体传感器的数据传输与环境侦测