提升抗干扰性能:详解迟滞比较器电路设计与计算

需积分: 20 28 浏览量

更新于2024-08-04

5

收藏 589KB PDF 举报

迟滞比较器电路原理介绍、设计计算

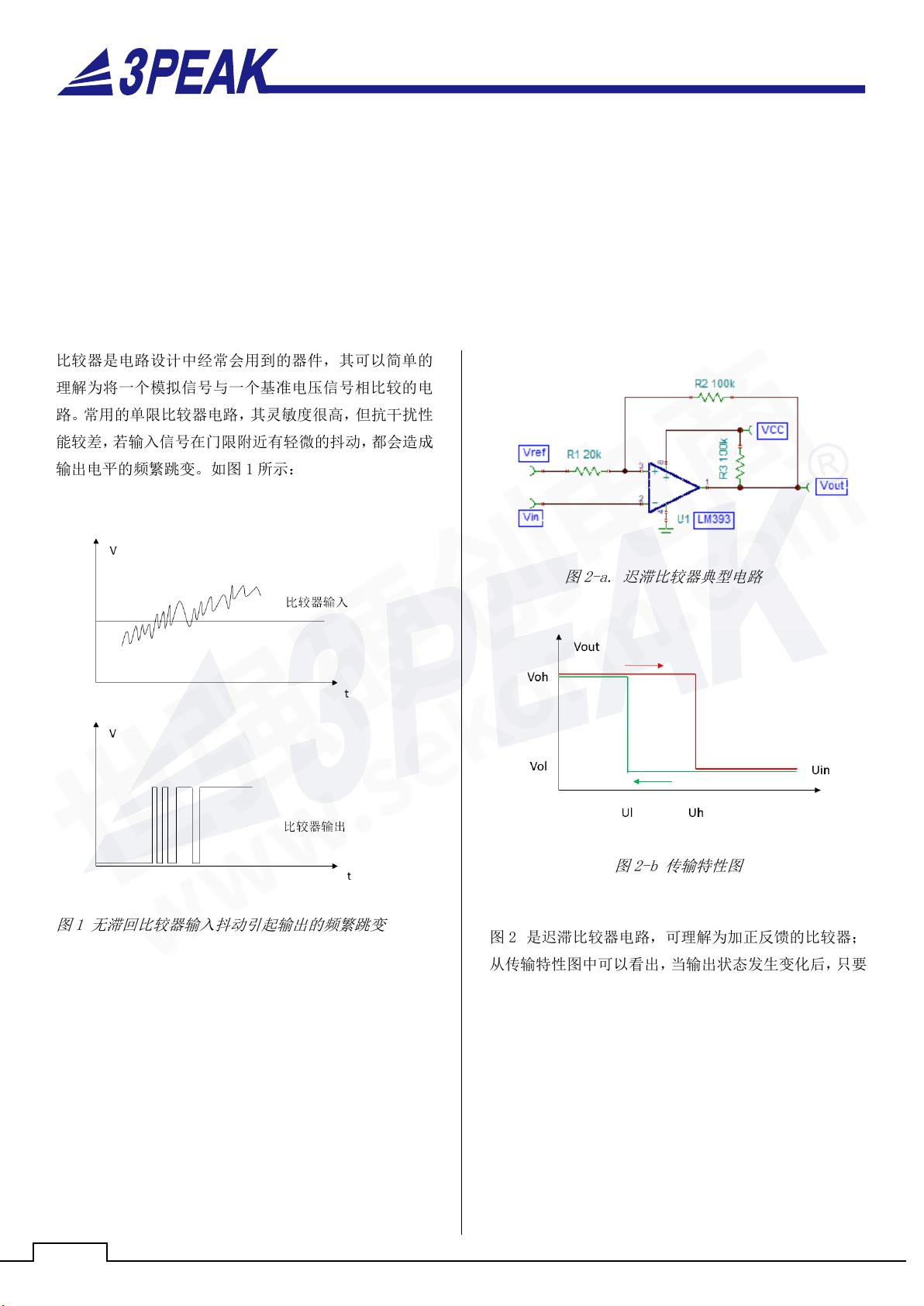

迟滞比较器是电路设计中的一种特殊类型,用于增强模拟信号比较器的抗干扰性能,尤其是在输入信号存在较大抖动时。它不同于常规的单限比较器,单限比较器虽然灵敏度高,但对输入信号的微小变化很敏感,容易导致输出电压的频繁跳变。迟滞比较器通过引入正反馈和设置不同上升和下降阈值来解决这个问题。

迟滞比较器的基本原理是利用运算放大器构成,比如使用LM358运放。电路结构包含一个参考点,通常使用稳压管实现,以及两个串联的分压电阻R1和R2。信号从运放的负输入端进入,通过电阻网络进行比较。当输入电压的变化超出设定的滞回电压范围(约为5mV至10mV),输出才会发生切换,从而限制了因输入抖动引起的输出不稳定。

电路设计的关键参数包括输入门限Uh(当输出为高电平时对应的输入电压)、输入下限Ul(当输出为低电平时对应的输入电压)和滞回电压宽度ΔU(Uh和Ul之间的电压差)。计算公式为:

- Uh = Vref * R2 / (R1 + R2) + Voh * R1 / (R1 + R2)

- Ul = Vref * R2 / (R1 + R2) + Vol * R1 / (R1 + R2)

- ΔU = Uh - Ul = (Voh - Vol) * R1 / (R1 + R2)

其中,Vref是参考电压,Voh是输出高电平电压,Vol是输出低电平电压,VCC代表电源电压,GND代表地。

迟滞比较器的优点在于提高了抗干扰能力,即使输入信号有较大的波动,也能保持输出的稳定。然而,这种稳定性是以牺牲灵敏度为代价的,它可能无法准确检测小于滞回电压变化的输入电压。因此,在选择使用迟滞比较器时,需要权衡灵敏度和抗干扰性的需求。

总结来说,迟滞比较器电路设计的关键在于理解其工作原理,合理配置电阻和参考电压,以便在实际应用中达到所需的效果。这对于在噪声环境中稳定信号处理或者需要高抗干扰能力的系统设计至关重要。

2020-07-11 上传

2023-01-17 上传

2020-10-16 上传

2021-09-15 上传

2022-07-09 上传

2021-10-01 上传

点击了解资源详情

点击了解资源详情

挖矿大亨

- 粉丝: 165

- 资源: 17

最新资源

- libcsv-开源

- RESTful-API:RESTful API已在Postman,Robo 3T和MongoDB上测试

- ultrasound

- hw-3

- QuickSort-Asm:装配中快速排序的实现

- learnPython:包含我所有的工作样本和学习进度

- real-time:实时通讯

- 这里是我的MySql和Jdbc的学习笔记, 要重点整理, 日后作为讲课使用.zip

- leson-1.2:第2课,第1课,任务2

- model-t-electronics:BrewBit Model-T 电子产品

- flutterui_fragrance

- SQLServer2005_SSMSEE%2864位系统用%29.zip

- platform-code-ex

- pycocotools_windows-2.0.0.2-cp38-cp38-win_amd64.whl

- Insta资讯提供:Insta后端的资讯提供

- 用于自动记录学习时间、统计学习情况、自动生成图表的程序,QT+mysql实现,有图形化界面.zip