FPGA设计思想与技巧:乒乓操作与流水线

需积分: 3 9 浏览量

更新于2024-09-16

收藏 220KB PDF 举报

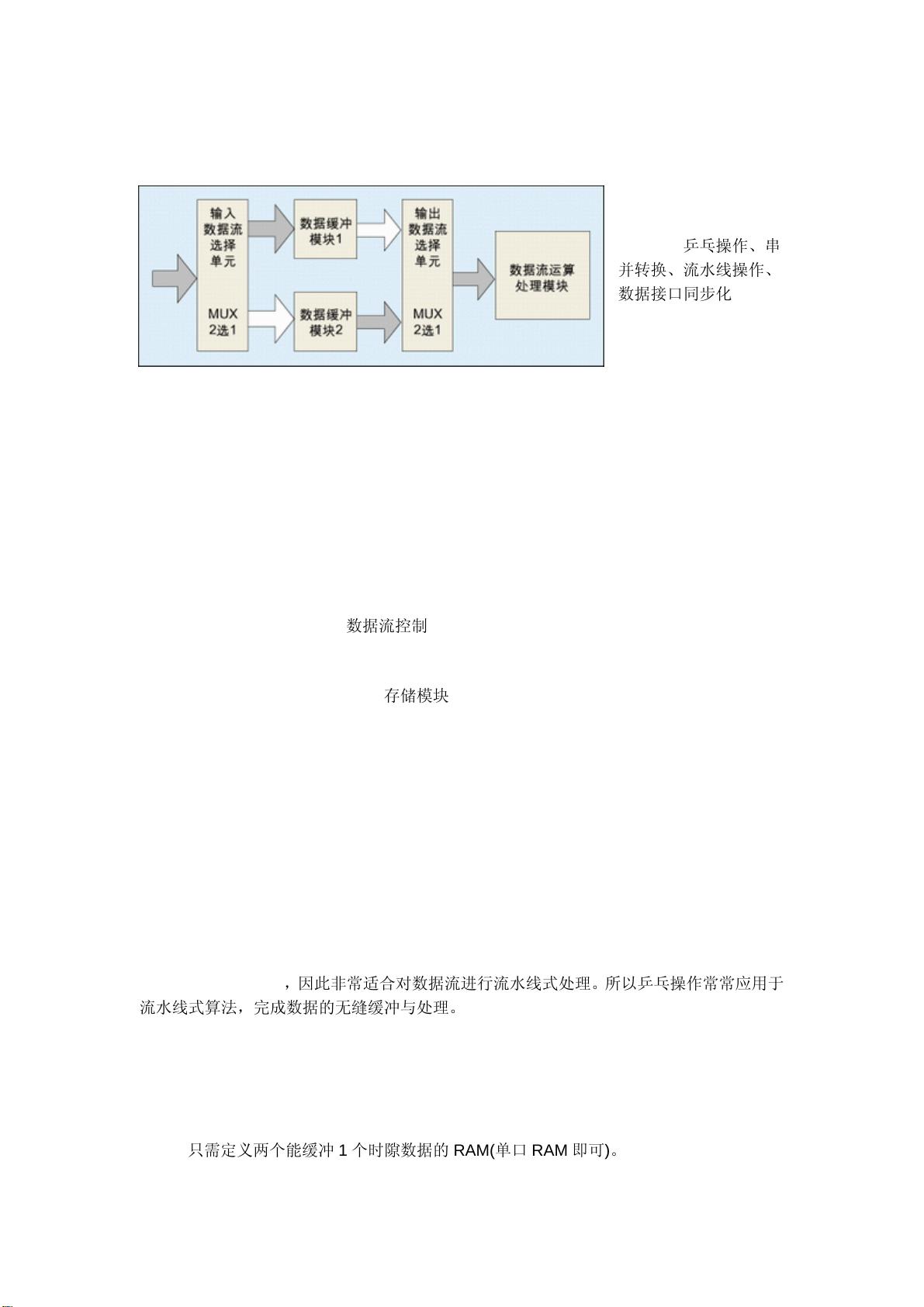

"FPGA设计的关键思想与技巧,包括乒乓操作、串并转换、流水线操作和数据接口同步化,是提升FPGA/CPLD设计效率的重要方法。乒乓操作利用双缓冲区实现连续数据流处理,节约存储空间,并适用于流水线算法。"

在FPGA设计领域,Verilog语言是广泛使用的硬件描述语言,它为实现复杂逻辑功能提供了强大的工具。FPGA(CPLD)设计不仅依赖于扎实的硬件知识,还需要巧妙地运用各种设计思想和技术。本文主要探讨了四个关键的设计策略:

1. **乒乓操作**:这种设计技巧源自于数据流控制,通过两个交替使用的数据缓冲区(例如双口RAM或FIFO)来保持数据处理的连续性。数据依次进入一个缓冲区,同时另一个缓冲区中的数据被处理,通过数据选择单元实现无缝切换,避免了数据处理的中断。乒乓操作在需要实时处理连续数据流的场合,如通信系统的基带处理中,具有显著优势,能够有效减少存储需求并提高系统性能。

2. **串并转换**:在FPGA设计中,串行和并行数据之间的转换是常见的操作。例如,串行数据可能来自外部接口,而内部逻辑往往需要并行处理。通过串并转换器,可以将串行数据并行化,提高处理速度,反之亦然,将并行数据串行化以便于传输。这种转换在高速数据传输和接口适配中尤其重要。

3. **流水线操作**:流水线技术是FPGA设计中的核心优化手段,它将复杂的处理任务分解为多个阶段,每个阶段在一个时钟周期内完成一部分工作。通过乒乓操作,数据可以在流水线的不同阶段连续流动,从而提高系统吞吐量,降低了延迟。流水线设计尤其适用于处理大量重复数据的任务,如图像处理和数字信号处理。

4. **数据接口同步化**:在多模块系统中,确保不同模块之间数据传输的同步至关重要。这通常通过时钟管理和同步电路实现,以防止数据丢失或错误。同步化处理可以避免竞争条件和亚稳态,保证系统稳定性。

理解并熟练运用这些设计思想和技巧,对于FPGA/CPLD的高效设计至关重要。在实际工程中,根据应用场景灵活组合运用,可以显著提高设计的效率和系统的性能。同时,随着技术的发展,如DDR接口、PCIe等高速接口的集成,以及高级综合工具的应用,这些基础设计原则仍然是优化FPGA设计的基础。通过不断学习和实践,工程师可以更好地应对日益复杂的硬件设计挑战,实现更加先进和高效的系统。

2017-12-23 上传

2014-07-20 上传

2010-01-09 上传

2019-01-28 上传

2013-01-06 上传

2010-01-16 上传

2010-04-22 上传

2014-08-16 上传

xuan1989

- 粉丝: 0

- 资源: 3

最新资源

- Android圆角进度条控件的设计与应用

- mui框架实现带侧边栏的响应式布局

- Android仿知乎横线直线进度条实现教程

- SSM选课系统实现:Spring+SpringMVC+MyBatis源码剖析

- 使用JavaScript开发的流星待办事项应用

- Google Code Jam 2015竞赛回顾与Java编程实践

- Angular 2与NW.js集成:通过Webpack和Gulp构建环境详解

- OneDayTripPlanner:数字化城市旅游活动规划助手

- TinySTM 轻量级原子操作库的详细介绍与安装指南

- 模拟PHP序列化:JavaScript实现序列化与反序列化技术

- ***进销存系统全面功能介绍与开发指南

- 掌握Clojure命名空间的正确重新加载技巧

- 免费获取VMD模态分解Matlab源代码与案例数据

- BuglyEasyToUnity最新更新优化:简化Unity开发者接入流程

- Android学生俱乐部项目任务2解析与实践

- 掌握Elixir语言构建高效分布式网络爬虫