DDR3内存布线详解:菊花链与飞越技术应用

本文档提供了关于DDR3内存布线的深入指南,主要针对系统级PCB设计者和FPGA接口开发者。DDR3内存技术相比于DDR2有着显著的变化,包括更高的数据速率(400-800Mbps提升至800-1600Mbps)和新的布线要求。文档重点介绍了以下几个关键知识点:

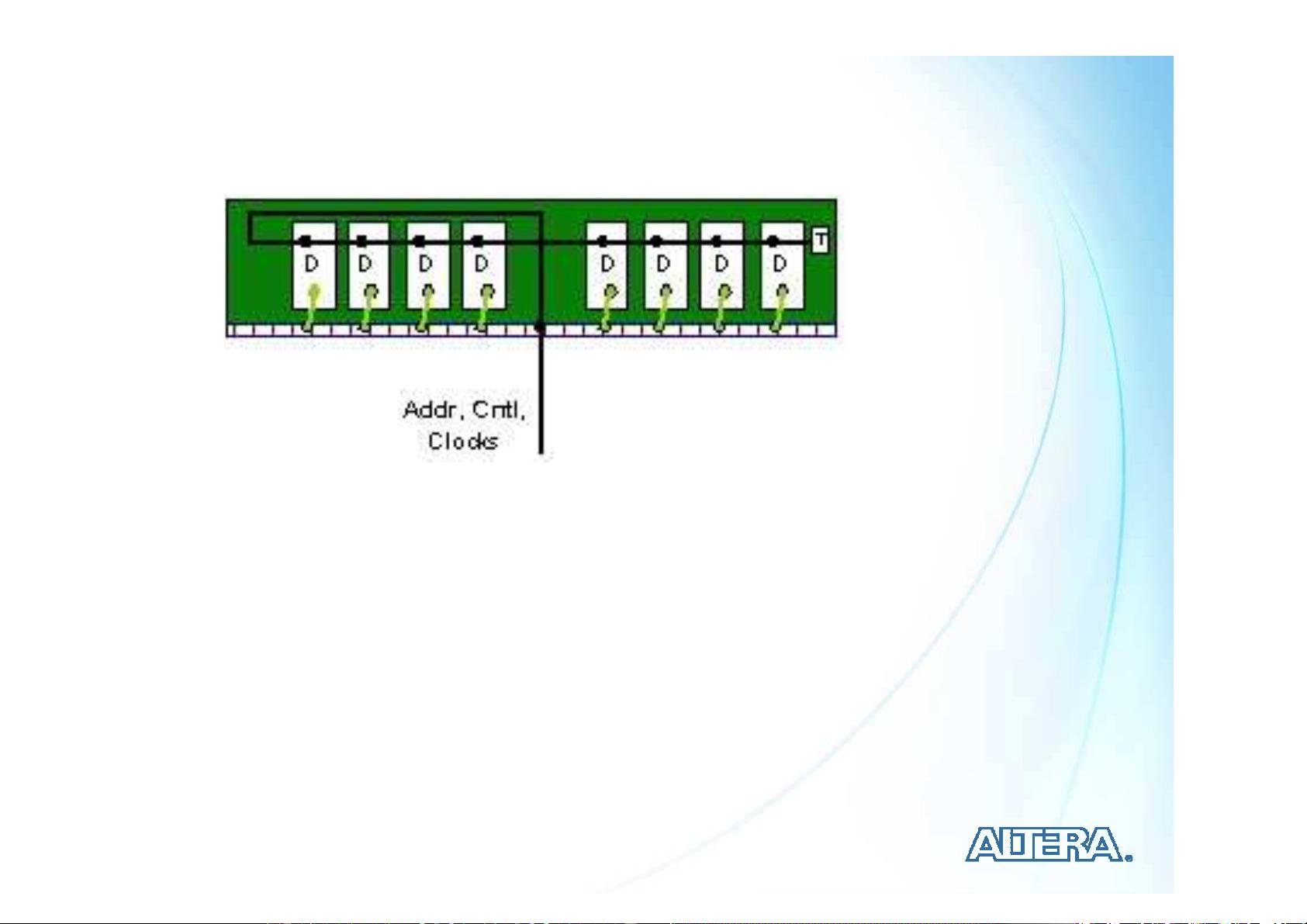

1. **迁移至DDR3**:从DDR2到DDR3的过渡是一个重要的考虑因素,这涉及到了芯片级别的接口升级,如地址(Addr)和数据(Data)线的处理方式变化。DDR3的地址线采用飞by(Fly-by)布线方法,而DDR2则使用菊花链(Daisy-chain)路由。这意味着在新设计中,必须优化这些线路以适应DDR3的高速和低延迟特性。

2. **动态ODT(On-Die Termination)**:DDR3引入了动态ODT技术,即地址和时钟信号(Addr, Clk)采用树状路由(Treerouted),以实现更有效的信号完整性管理。而数据线则采用点对点连接(Point-to-point),这有助于减少串扰并提高信号质量。

3. **电压和速率**:DDR3工作在1.8V SSTL标准下,数据速率比DDR2高一倍。这就要求PCB设计者对电源和地线布局更加谨慎,以确保足够的电压稳定性和信号传输效率。

4. **负载均衡**:DDR3内存的读写 leveling是另一个挑战,设计者需确保所有内存颗粒之间的信号负载均衡,以避免性能差异。这涉及到接口的初始化设置和分析,以确保系统的稳定运行。

5. **工具与方法论**:文中提到使用Altera公司的产品如Stratix, Arria, Cyclone等进行DDR3接口设计,可能涉及使用Quartus等工具进行设计、仿真和布局。文档还可能提供了一套实施DDR3内存接口的方法论,以帮助开发人员顺利实现硬件和软件的集成。

总结来说,本文档是一份实用的参考资源,涵盖了DDR3内存布线的关键技术要点,对PCB设计师和FPGA开发人员在面临DDR3内存升级项目时,理解和解决接口挑战具有重要意义。它强调了在设计过程中应遵循的策略,包括选择正确的布线方法、电压管理以及接口性能分析,以确保最终产品满足DDR3内存的高速和稳定性要求。

2262 浏览量

3529 浏览量

296 浏览量

215 浏览量

1714 浏览量

462 浏览量

735 浏览量

1276 浏览量