EDA技术:系统优化与时序分析详解

需积分: 5 48 浏览量

更新于2024-07-09

收藏 1.25MB PDF 举报

"本章主要介绍了系统优化和时序分析在电子设计自动化(EDA)中的应用。内容涵盖了资源优化、速度优化以及优化设置与时序分析的相关技术,并提供了相关的实践练习题目。"

在电子设计自动化领域,系统优化和时序分析是确保设计效率和性能的关键步骤。第8章详细阐述了这些概念和技术。

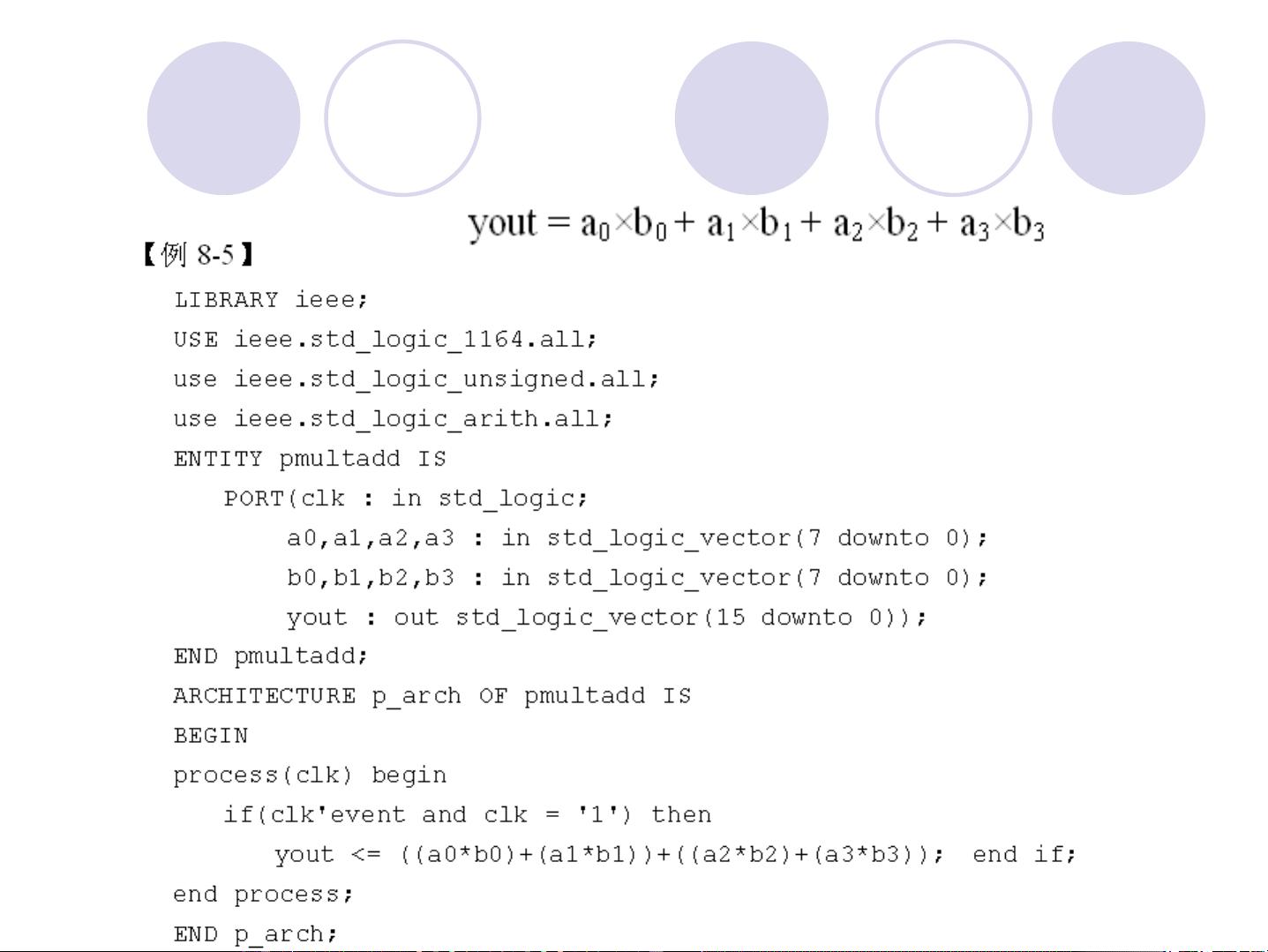

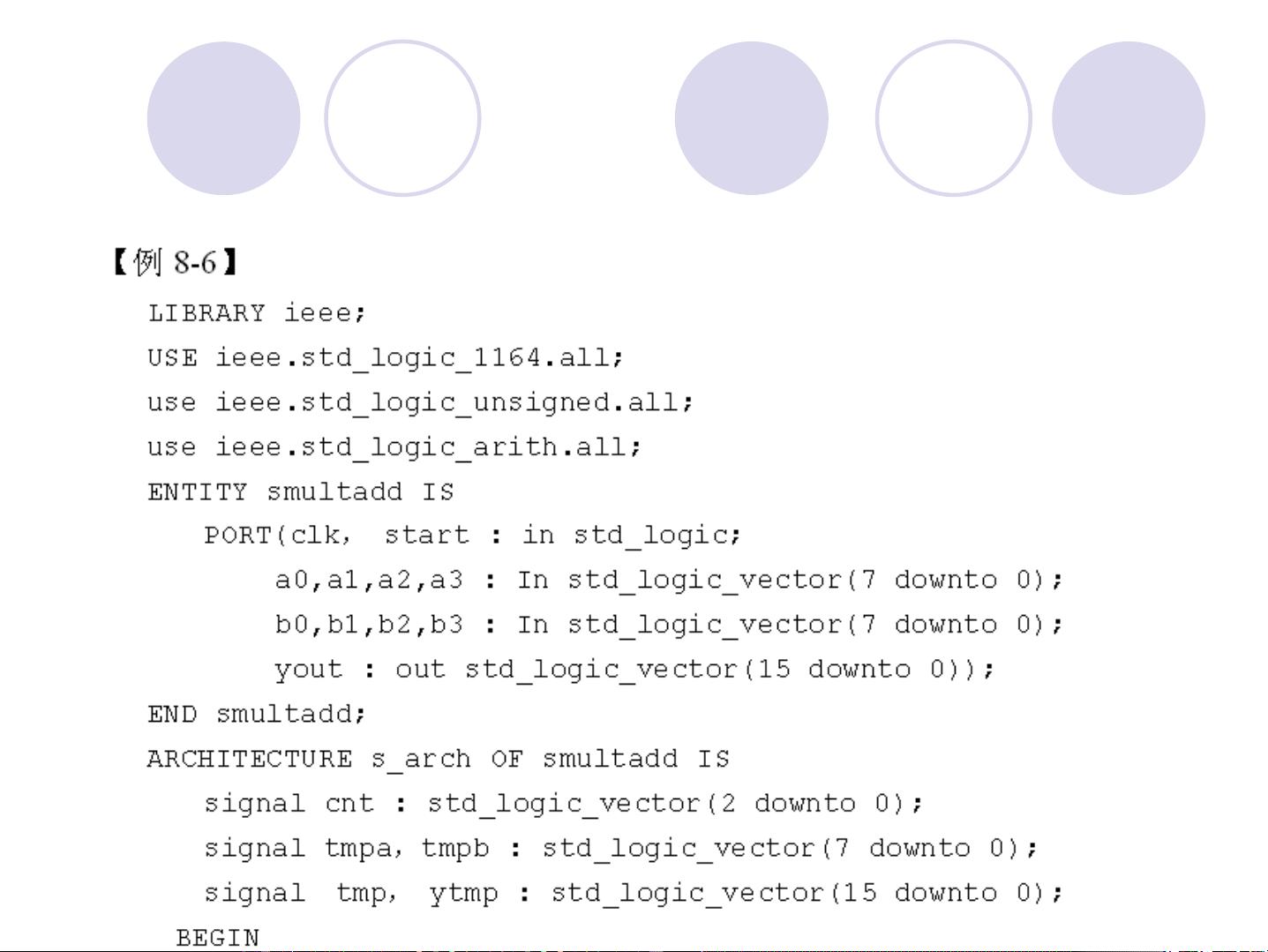

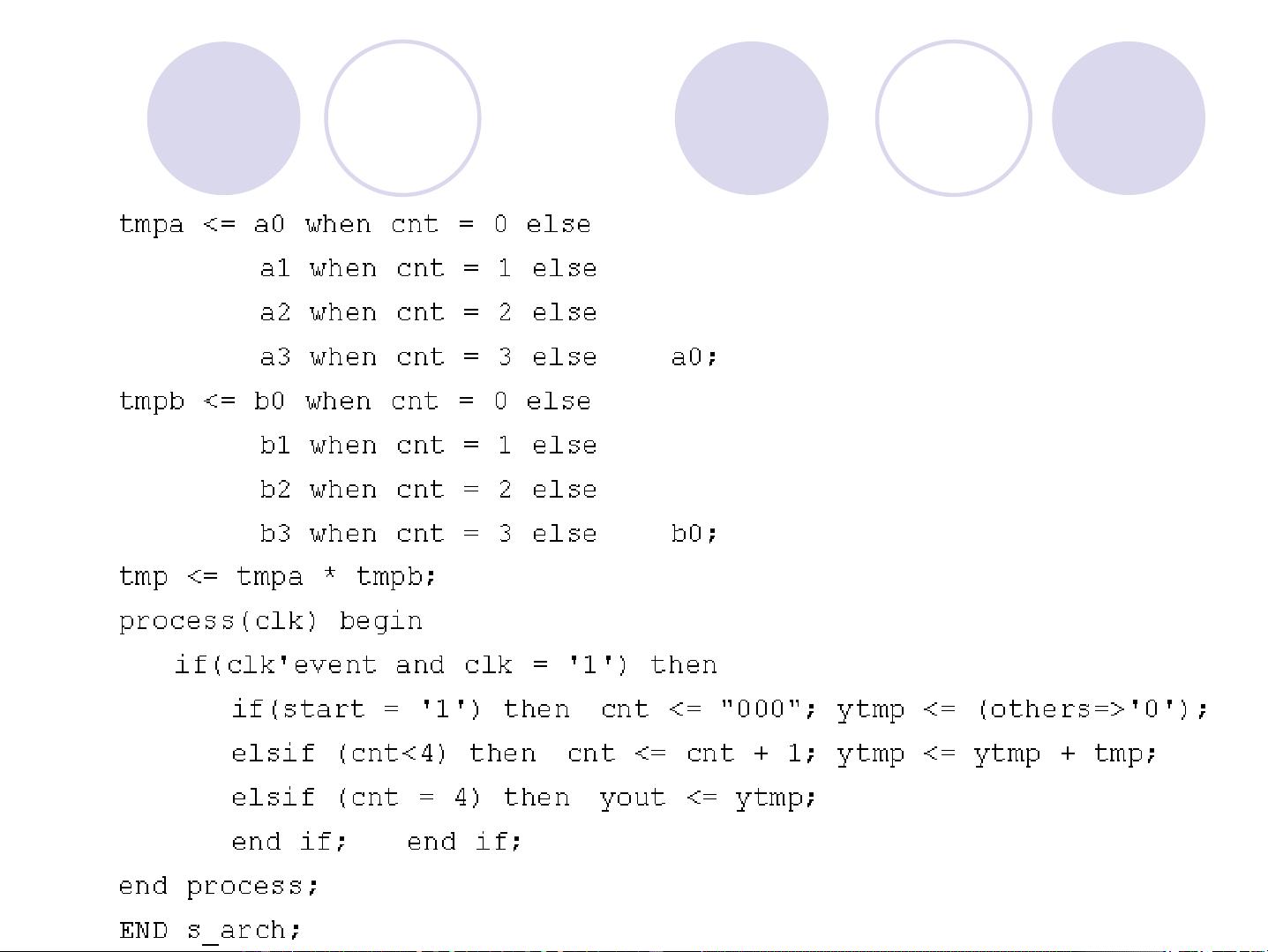

首先,章节8.1专注于资源优化,特别是资源共享。资源共享是一种有效的面积优化策略,通过复用设计中的相同或相似资源来减少硬件的需求,进而减小芯片的物理尺寸。这包括逻辑门、触发器、乘法器等电路元件的共享。此外,8.1.2节提到了逻辑优化,它涉及简化逻辑结构以减少逻辑门的数量,同时保持功能不变。逻辑优化通常包括布尔代数简化、多余门的删除以及逻辑重组等。紧接着,8.1.3节讨论了串行化,这是一种将并行操作转换为串行操作的方法,以节省硬件资源,但可能会增加处理时间。

进入8.2速度优化部分,主要关注提高设计的运行速度。8.2.1节详细讲解了流水线设计,这是通过分段处理任务,使得各个阶段可以并行进行,从而显著提高系统的吞吐率。流水线设计在嵌入式系统和处理器设计中尤为重要。8.2.2节提到了寄存器配平,这是一种平衡流水线中各阶段延迟的技术,以避免瓶颈。8.2.3节介绍了关键路径法,它是确定电路延迟限制的最直接方法,通过识别和优化设计中最长路径来提升整体速度。8.2.4节的乒乓操作法和8.2.5节的加法树法都是进一步加速计算过程的策略,加法树结构可以实现更快的加法运算,类似流水线原理。

8.3章则聚焦于优化设置与时序分析。DesignAssistant工具用于检查设计的可靠性,而增量布局布线控制设置允许设计师在不牺牲性能的情况下调整布线过程。时序设置与分析是评估设计速度性能的关键,通过这些设置可以确保设计满足特定的时序约束。查看时序分析结果可以帮助识别设计中的潜在问题。8.3.5节的适配优化设置示例给出了实际操作步骤,包括在QuartusII环境中进行工程创建、设置和逻辑锁定优化。逻辑锁定技术(LogicLock)是QuartusII的一个特性,它允许对已布局的逻辑进行修改,以提高性能或解决布线问题,适用于多种FPGA器件。

章节最后给出了几道习题,鼓励读者运用所学知识对具体的设计进行优化,如面积优化、逻辑改进和滤波器设计等。

这一章全面地探讨了系统优化和时序分析的各个方面,对于理解如何在EDA中有效地管理和提升设计性能至关重要。

2021-07-13 上传

2019-12-17 上传

2019-12-17 上传

2012-09-26 上传

2023-06-27 上传

2012-05-16 上传

2022-03-01 上传

2022-11-10 上传

2012-08-22 上传

carylu2017

- 粉丝: 0

- 资源: 12

最新资源

- 25175员工工资管理系统 2.0 build20111230

- DragonFace_V2_2_3_20150122.rar

- docker-compose-pi-hole:我的pihole docker-compose设置

- AE音频可视化43.zipae轨道音频可视化模板文件,专门用于制作二次元音乐播放视频 视频剪辑必备 压缩文件解压即可,winal

- online-Question-Answer_Django

- f793gp.zip 夜间节能上网,畅通应用工程,实际上很好用,呱呱叫

- 自动开关机系统原理图及PCB

- GC jQuery UI theme switcher:jQuery插件提供了一个jQuery UI对话框来更改UI主题CSS-开源

- ahmedabadexplorer:适用于Ahmedabad人民的完整城市指南应用程序

- javastream源码-kafka_spark_gazebo:简单的Java源代码,用于在Gazebo/ROS实现之上运行ApacheKaf

- 网奇cms网站管理系统 5.7

- marlene353.github.io

- 公司股东合作协议.zip

- PDF Logo Remover 1.0.rar

- matlab路由协议源码-wagtailcodeblock:带有实时PrismJS语法突出显示的WagtailCMS的StreamField代

- 基于python开发的贸易数据查询软件v1.0下载