CPCI总线架构下的微波接收机设计与实现

PDF格式 | 237KB |

更新于2024-09-01

| 101 浏览量 | 举报

"接口/总线/驱动中的一种CPCI总线结构微波接收机设计方案"

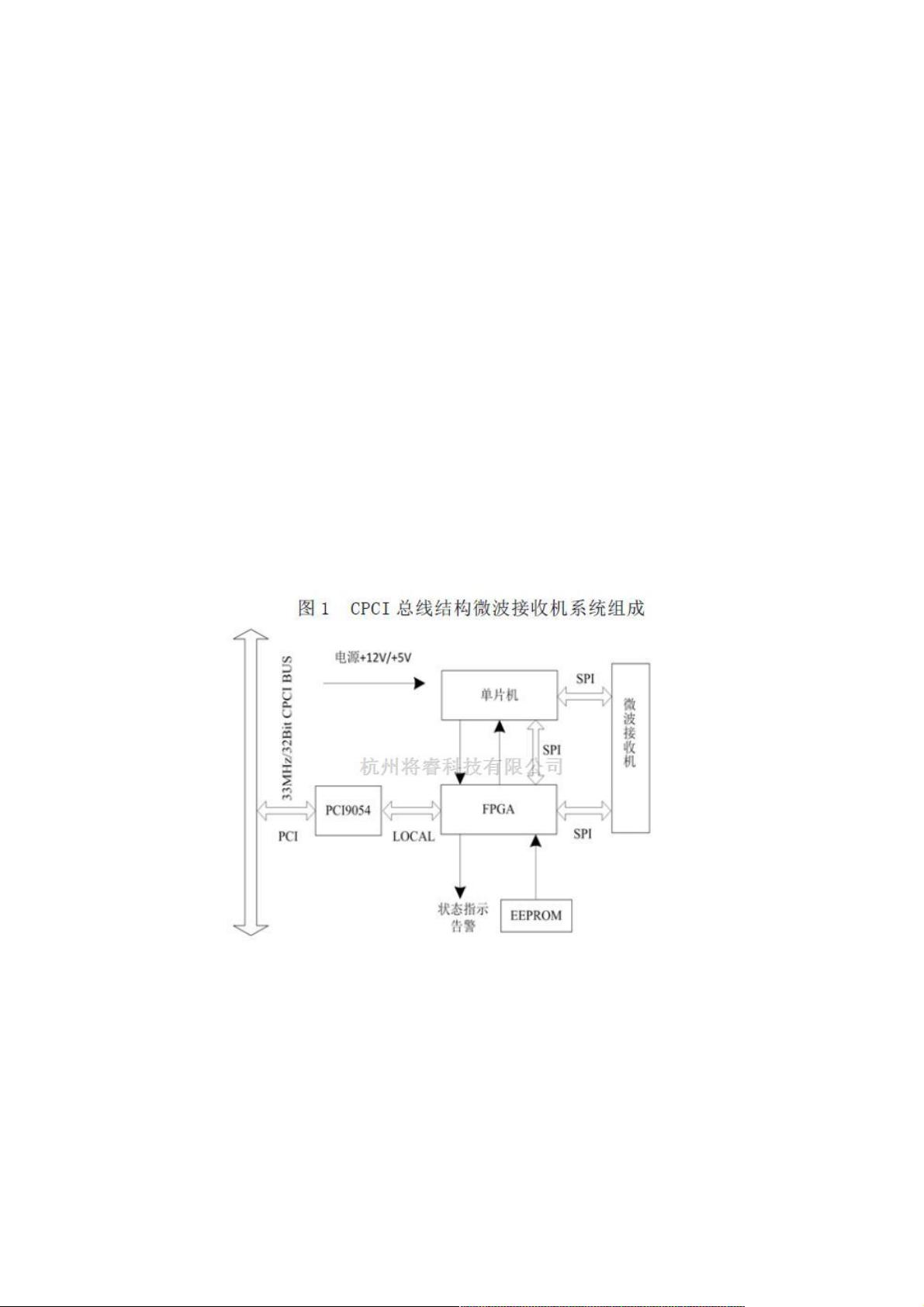

本文介绍了一种基于CPCI(Compact Peripheral Component Interconnect)总线结构的微波接收机设计方法,针对微波接收机小型化、模块化、通用化的迫切需求,提出了创新性的解决方案。CPCI总线作为一种在科研和军工领域广泛应用的工业计算机总线标准,它融合了PCI总线的电气和软件特性以及欧式卡的工业组装技术,提供了高速数据传输、即插即用的便利性,以及在严苛环境下运行的高可靠性。

设计中,采用了PCI桥芯片PCI9054来实现CPCI总线与LOCAL总线之间的接口转换。LOCAL总线允许在系统内部进行高效的数据交换,而PCI9054则扮演了关键的角色,将来自CPCI总线的高速信号转化为适合局部操作的信号。此外,设计中还结合了高速FPGA(Field-Programmable Gate Array)和具有强大控制能力的单片机,如EP1C6Q240C8 FPGA和Atmega8L单片机,共同实现对微波接收机增益和锁相环的实时精确控制。

FPGA与单片机的接口实现是设计中的关键技术之一。通过Verilog HDL语言编程,FPGA可以接收并处理来自CPCI总线的控制信号,执行数据的快速读写操作。同时,单片机负责系统的管理和协调,确保整个微波接收机系统的稳定运行。在硬件设计中,还包括了系统结构布局、电源管理以及电磁兼容性(EMC)设计,这些都是确保系统性能和稳定性的重要环节。

电源设计是另一个关键点,需要提供稳定且低噪声的电源,以满足微波信号处理的敏感性要求。电磁兼容设计则是为了降低外部电磁干扰对系统的影响,保证微波接收机在各种复杂环境中能够正常工作。

这种CPCI总线结构的微波接收机设计方案充分利用了现代数字处理技术的优势,实现了高效率、高精度的信号处理。其模块化的设计使得系统更易于维护和升级,适用于智能交通、航空航天等领域的需求。通过软硬件的协同工作,该系统能够有效地处理微波信号,满足了移动平台上的无线通信需求。

相关推荐

weixin_38723683

- 粉丝: 6

最新资源

- iBATIS 2.0开发指南:入门与高级特性的全面解析

- ESRI Shapefile技术描述详解

- MIF格式详解:GIS地图交换标准

- WEB标准解析与网站重构实践

- 深入解析JUnit设计模式

- PowerDesigner 6.1数据库建模详解与教程

- Spring框架开发者指南(中文版)

- 中文Vim教程:实践导向的手册

- Jboss EJB3.0 实例教程:从入门到精通

- Ant入门与高级应用指南

- Linux系统移植实战:从Bootloader到交叉工具链

- 数缘社区:数学与密码学资源宝库

- ADO.NET深度探索:连接、执行与数据处理

- Eclipse基础入门:集成开发环境详解

- Oracle动态性能视图详解与使用

- Java开发必备:字符串处理与日期转换技巧