静态时序分析:理解建立与保持时间约束

56 浏览量

更新于2024-07-15

收藏 3.27MB PDF 举报

"本文主要介绍了静态时序分析在数字电路设计中的重要概念,包括时钟延迟、时钟周期、时钟偏斜、建立时间、保持时间及其约束,并提供了实际案例来展示如何进行时序分析和优化。"

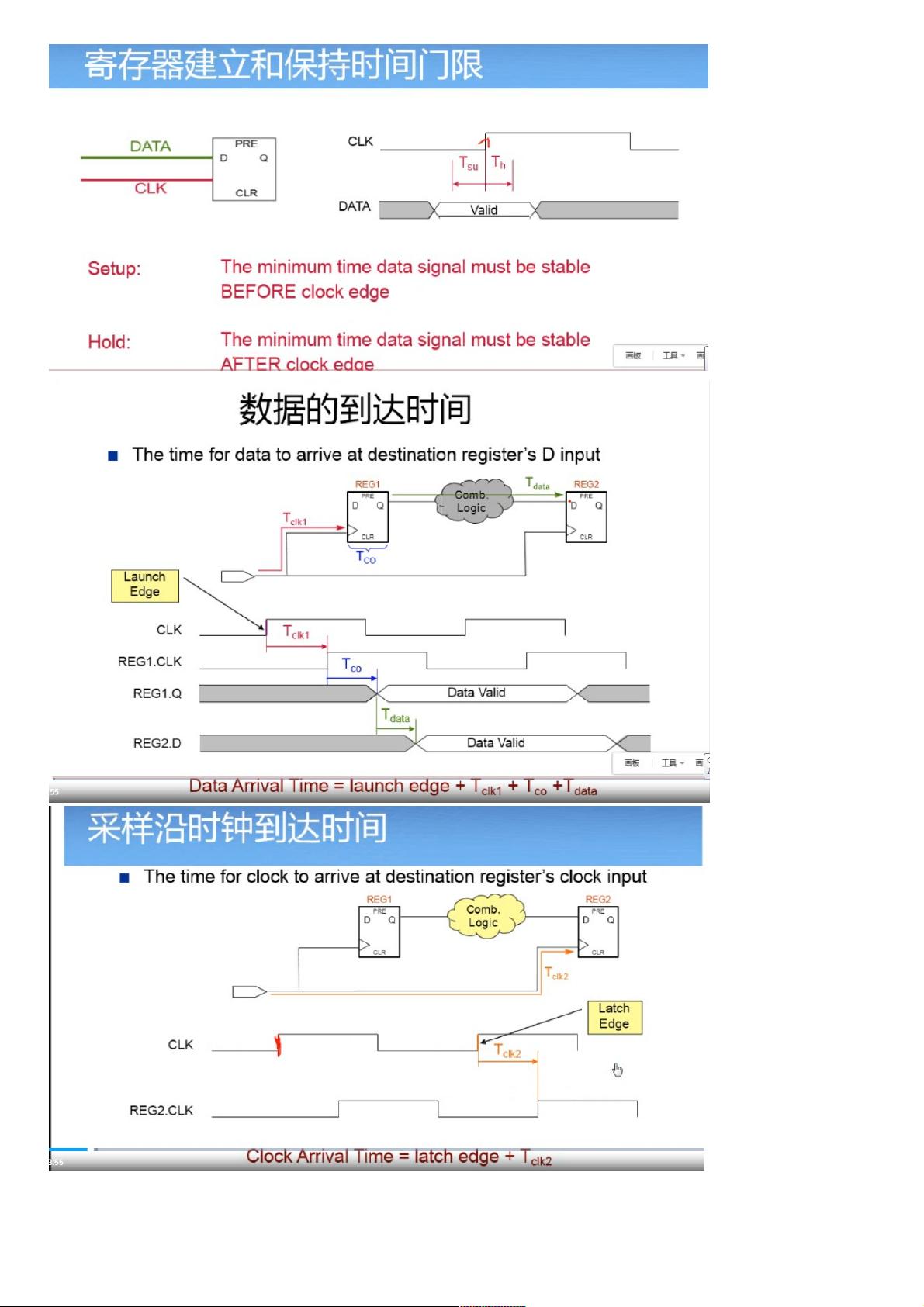

在数字集成电路设计中,静态时序分析是一种评估系统性能的关键技术,主要用于确保电路在时钟周期内的正确工作。它涉及到多个关键参数,如时钟延迟(T1)、时钟周期(T_cycle)、时钟偏斜(△T)以及建立时间(Ts)和保持时间(Th)。

时钟延迟(T1)是从时钟信号生成到传递到某个特定点的时间,而时钟周期(T_cycle)是时钟信号的一个完整周期,即从一个上升沿到下一个上升沿的时间。时钟偏斜(△T)是时钟信号在不同路径上的延迟差,这通常由布线延迟引起。建立时间(Ts)是指数据输入必须在时钟上升沿之前稳定的时间,以确保正确捕获。建立时间约束(Tsetup)是设计中设定的最小建立时间要求。建立时间余量(Tslack)是实际的建立时间与建立时间约束之间的差距,理想情况下应为正数。

保持时间(Th)则表示数据输入在时钟下降沿之后必须保持稳定的时间,以避免错误的读取。保持时间约束(Thold)是设计规定的最小保持时间。保持时间余量(Thslack)同样应该是非负值。时序分析的目标是确保所有路径的Tslack和Thslack都大于零,以保证电路的正确运行。

影响建立时间和保持时间的主要因素是时钟偏斜(△T)和时钟延迟(T1)。较大的△T可能导致保持时间不足,而较大的T1可能导致建立时间不足。每个数字器件都有其固有的建立时间和保持时间阈值,这些阈值决定了数据输入和时钟之间允许的最大延迟。

在给定的例子中,T1=3ns,T2=2.5ns,T3=1.5ns,T=2ns,Tcycle=8ns,Tsetup=0.5ns,Thold=0.5ns。通过计算,我们可以得出Tslack=3.5ns,Thslack=3.5ns。这意味着当前设计满足时序约束。

在实际的工程实践中,时序分析通常使用专门的工具,如Altera的TimeQuest。通过分析时序报告,我们可以识别关键路径和违反时序约束的地方。例如,如果时钟频率改变,slack可能会变为负值,这时就需要通过软件优化或代码修改来消除违规。优化可能包括调整设计参数、插入寄存器以减短路径,或对代码结构进行修改以减少延迟。通过这样的迭代过程,设计师可以确保电路在各种条件下都能正确、可靠地工作。

2021-09-10 上传

2021-09-29 上传

2021-10-10 上传

2021-10-10 上传

2022-09-24 上传

2022-07-14 上传

weixin_38728183

- 粉丝: 5

- 资源: 942

最新资源

- NodejsEjModulo5:JavierLurquí-Nodejs课程第5单元的练习

- Two-Activities-Challenge

- lpc4330_Xplorer_Keil.rar_微处理器开发_Others_

- Website Opener-crx插件

- 参考资料-中国历代将相书法珍品.zip

- wp.com上新P2主题的自托管版本。-JavaScript开发

- ADCH.NET-开源

- torch_cluster-1.5.9-cp37-cp37m-macosx_10_9_x86_64whl.zip

- Soul_Crawl :(我最早创建的游戏之一)《 Dungeon Crawler》增加了

- news_app_flutter:具有响应式设计的跨平台新闻应用程序。 Newsapi.org的api密钥

- PowerScriptPowerBuilder9.011673263.rar_matlab例程_PowerBuilder_

- PyPI 官网下载 | multidict-1.1.0b2-cp34-cp34m-win_amd64.whl

- XGboost-hyperparameter-tuning

- wiki.status.im:这是Wiki ...状态

- 从基础颜色标记生成可访问的UI颜色。-JavaScript开发

- java_codes:此存储库将具有使用Java编程语言编写的编码示例