"Verilog结构化设计实现ALU运算功能,并提升FPGA设计能力"

需积分: 0 107 浏览量

更新于2024-01-19

2

收藏 6.1MB DOCX 举报

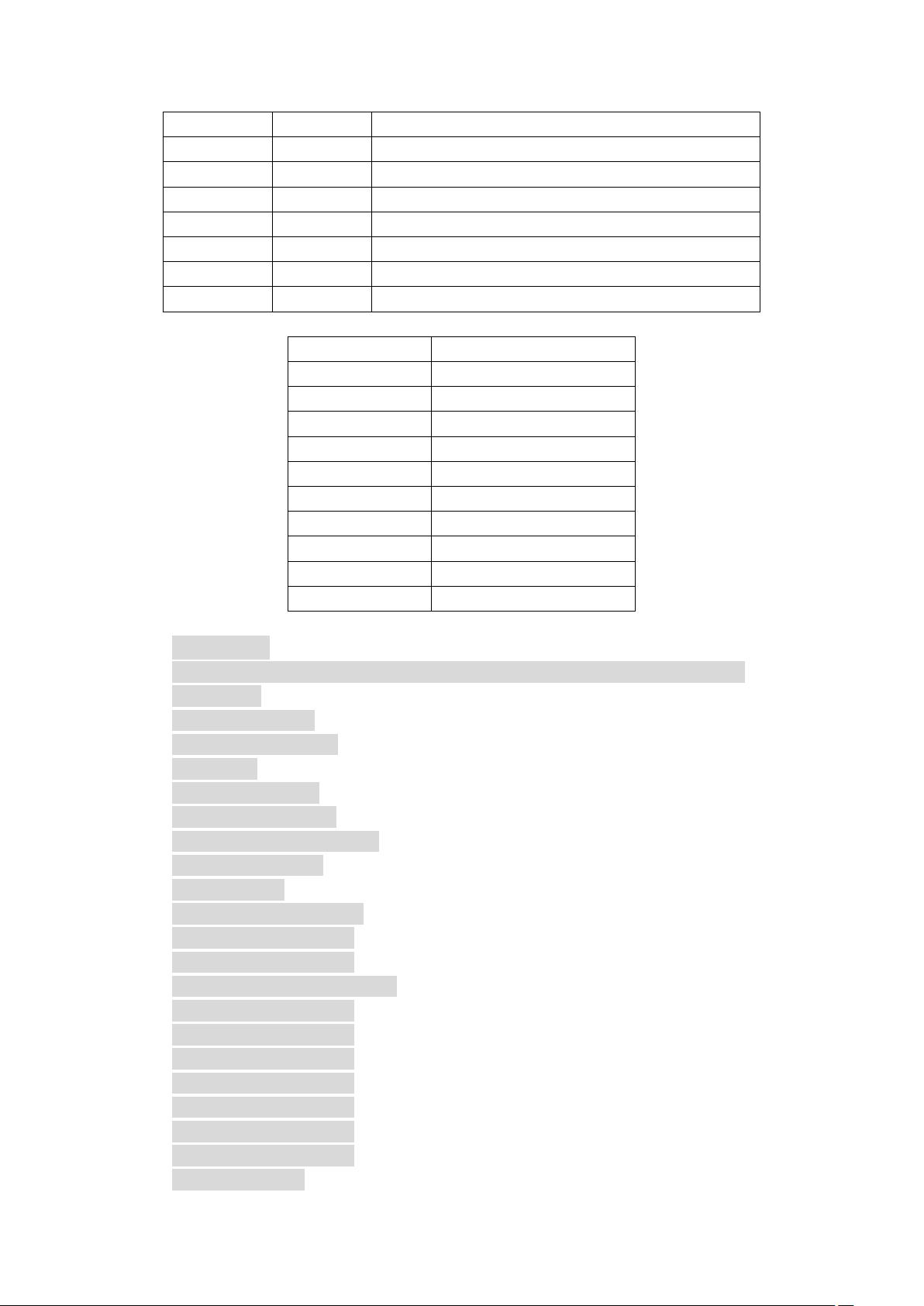

本实验通过使用Verilog HDL语言对SN74181和SN74182进行建模与验证,以及对ALU进行建模与验证。首先,通过实例化补码的定点加/减法器、定点乘法器、定点除法器以及相应的逻辑运算和移位运算器,可以将多个功能组合成综合的ALU。综合的ALU电路图如图所示,并且信号的说明表如下:

信号 功能

ALUAB ALU的A输入

ALUB ALU的B输入

Rst ALU的复位信号

clk ALU的时钟信号

ALUctrl ALU的控制信号

lshamt ALU的移位位数

Result ALU的输出结果

Result_high ALU的高位输出结果

OF ALU的溢出标志位

在本实验中,我首先熟悉了SN74181和SN74182的建模方法和验证技术。然后,通过Verilog HDL语言对这两个模块进行建模。接下来,我利用Verilog HDL语言对ALU进行建模。在建模过程中,我根据ALU的功能模块逐步设计ALU的结构,并且利用Vivado软件进行验证。

在ALU的设计中,我实现了十个运算功能,包括算术运算和逻辑运算。算术运算包括加法、减法、乘法和除法,逻辑运算包括与、或、非、异或和移位运算。通过对ALU的建模与验证,我进一步理解了计算机组成原理中算术运算器的底层运算逻辑,并且提升了FPGA结构化设计能力。

通过本次实验,我掌握了SN74181和SN74182的建模方法与验证技术,也掌握了ALU的建模与验证技术。同时,我熟悉了Xilinx Vivado 2014.2软件的使用,提升了在Windows系统PC机上进行实验的能力。

在实验的过程中,我遇到了一些困难和问题,但通过细心的调试和反复的实验,最终成功完成了ALU的设计和验证。通过这次实验,我对计算机组成原理中的ALU有了更深入的了解,对Verilog HDL语言和FPGA结构化设计有了更为扎实的掌握。

总之,通过本次实验,我不仅掌握了ALU的设计和验证技术,也提高了在计算机组成原理中应用Verilog HDL语言进行结构化设计的能力。这对我今后在计算机与信息学院的学习和研究中都具有重要的意义。同时,我也认识到了继续深入学习计算机组成原理和FPGA结构化设计的重要性,将继续努力提升自己的能力。

1343 浏览量

2754 浏览量

2117 浏览量

103 浏览量

2024-10-28 上传

2024-11-04 上传

2024-10-28 上传

2024-11-21 上传

2024-12-31 上传

荼荻-

- 粉丝: 20

最新资源

- Premiere Pro CS6视频编辑项目教程微课版教案

- SSM+Lucene+Redis搜索引擎缓存实例解析

- 全栈打字稿应用:演示项目实践与探索

- 仿Windows风格的AJAX无限级树形菜单实现教程

- 乐华2025L驱动板通用升级解决方案

- Java通过jcraft实现SFTP文件上传下载教程

- TTT素材-制造1资源包介绍与记录

- 深入C语言编程技巧与实践指南

- Oracle数据自动导出并转换为Excel工具使用教程

- Ubuntu下Deepin-Wine容器的使用与管理

- C语言网络聊天室功能详解:禁言、踢人与群聊

- AndriodSituationClick事件:详解按钮点击响应机制

- 探索Android-NetworkCue库:高效的网络监听解决方案

- 电子通信毕业设计:简易电感线圈制作方法

- 兼容性数据库Compat DB 4.2.52-5.1版本发布

- Android平台部署GNU Linux的新方案:dogeland体验