Cadence原理图后处理:从编号到网表生成

需积分: 5 70 浏览量

更新于2024-06-25

收藏 1.85MB PDF 举报

"Capture-CIS原理图设计后处理"

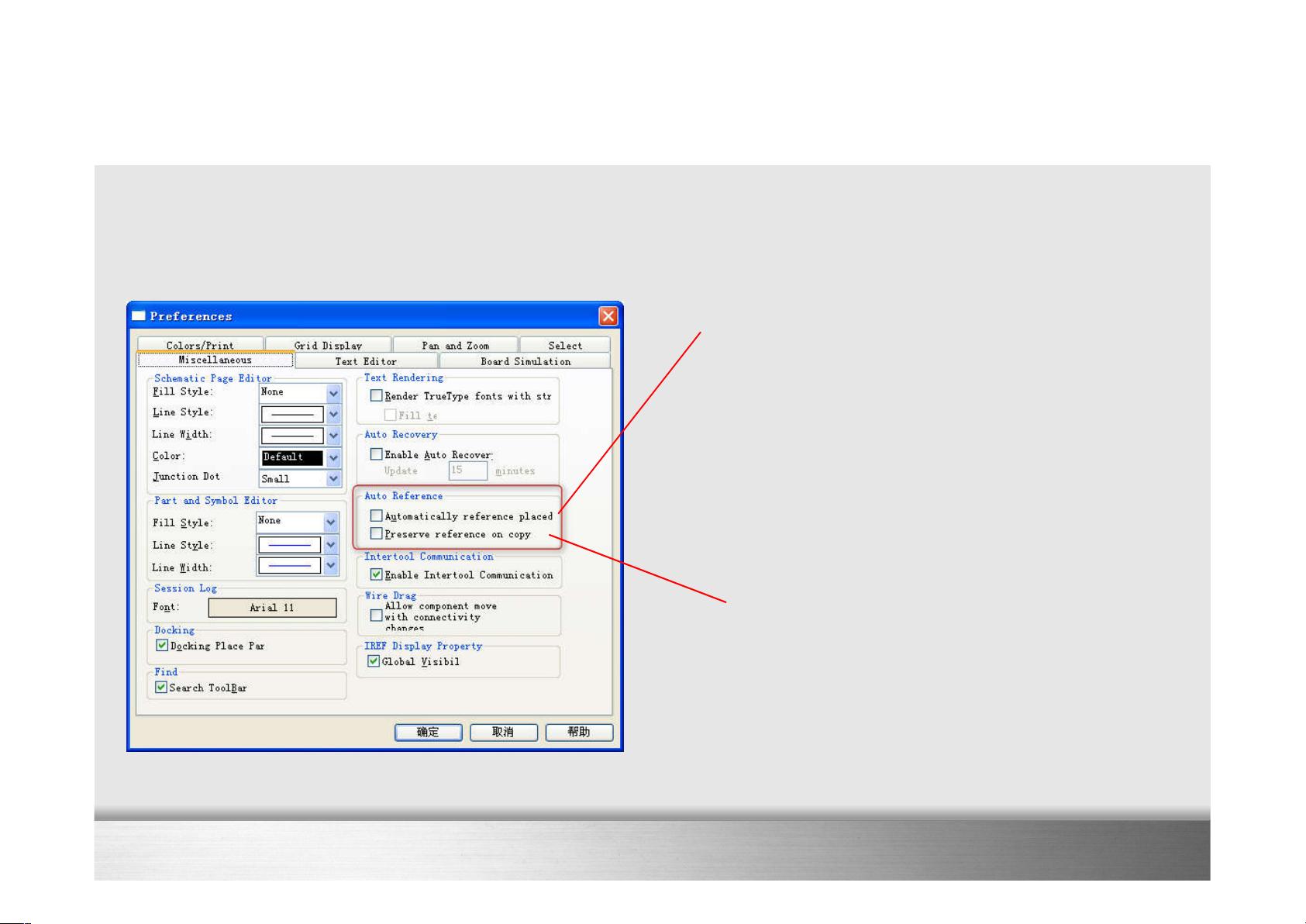

在电子设计自动化(EDA)领域,Cadence Capture CIS是一款广泛使用的原理图设计工具。原理图设计完成后,进行必要的后处理步骤至关重要,因为这确保了设计的准确性和完整性。这些步骤包括元器件编号、设计规则检查、元器件属性参数更新、生成网表以及元器件信息统计和BOM(Bill of Materials)输出。

1. **元器件编号**:元器件编号是确保每个元件在设计中具有唯一标识的关键步骤。编号原则通常是避免对已布局好的元件重新编号,以免增加PCB布局的工作量。新设计时,应为新增加的器件分配编号。编号格式通常包含元件类别和字符代号,例如B代表GaAs场效应管,N代表数字输入,C代表电容等。编号方法有两种:一是自动编号,在放置或复制元件时,系统自动按递增方式分配新的位号;二是保持复制元件的原有编号,复制的元件将保留原始的位号。

2. **设计规则检查(DRC)**:DRC用于检查原理图中的设计错误和潜在问题,如短路、开路、未连接的引脚、不匹配的电源和地等。通过执行DRC,设计者可以提前发现并解决这些问题,防止它们在PCB布局布线阶段造成困扰。

3. **元器件属性参数更新**:随着设计的进展,可能需要更新或校正元器件的参数信息,以确保与实际使用的物理器件一致。这包括电气特性、封装信息、供应商数据等,确保设计的可制造性。

4. **生成网表**:网表是连接原理图中各个元器件的逻辑关系表,它是PCB设计的基础。正确的网表能保证PCB布局布线的正确性。在Capture CIS中,完成所有检查和更新后,设计者需要生成一份无误的网表,供后续的PCB设计软件使用。

5. **元器件信息统计和BOM输出**:这部分工作涉及收集所有元器件的数量、类型、型号等信息,生成BOM,这对于采购、生产及成本估算都非常关键。BOM包含了所有需要用到的元器件列表,包括其数量、制造商信息、封装类型等,是生产流程的重要依据。

Capture CIS原理图设计后处理是一系列确保设计质量的过程,它涉及到元器件的逻辑和物理标识、设计合规性检查、信息的同步与更新,以及为PCB设计提供必要的输入。通过严谨的后处理,可以显著提高设计效率,减少错误,并为整个产品开发流程提供坚实的基础。

2017-08-27 上传

2018-04-22 上传

104 浏览量

2024-11-05 上传

2024-11-05 上传

2023-05-10 上传

2024-11-05 上传

2024-11-06 上传

2024-10-26 上传

白日做梦的老虎

- 粉丝: 136

- 资源: 80

最新资源

- Cucumber-JVM模板项目快速入门教程

- ECharts打造公司组织架构可视化展示

- DC Water Alerts 数据开放平台介绍

- 图形化编程打造智能家居控制系统

- 个人网站构建:使用CSS实现风格化布局

- 使用CANBUS控制LED灯柱颜色的Matlab代码实现

- ACTCMS管理系统安装与更新教程

- 快速查看IP地址及地理位置信息的View My IP插件

- Pandas库助力数据分析与编程效率提升

- Python实现k均值聚类音乐数据可视化分析

- formdotcom打造高效网络表单解决方案

- 仿京东套餐购买列表源码DYCPackage解析

- 开源管理工具orgParty:面向PartySur的多功能应用程序

- Flutter时间跟踪应用Time_tracker入门教程

- AngularJS实现自定义滑动项目及动作指南

- 掌握C++编译时打印:compile-time-printer的使用与原理