DE1_SoC FPGA设计入门教程

下载需积分: 9 | PDF格式 | 4.25MB |

更新于2024-07-20

| 141 浏览量 | 举报

"SoC-FPGA Design Guide(DE1_SoC).pdf" 是一份英文的SoCFPGA基础开发教程,特别适合初级开发者学习。文档详细介绍了SoCFPGA的设计和DE1_SoC开发板的使用。

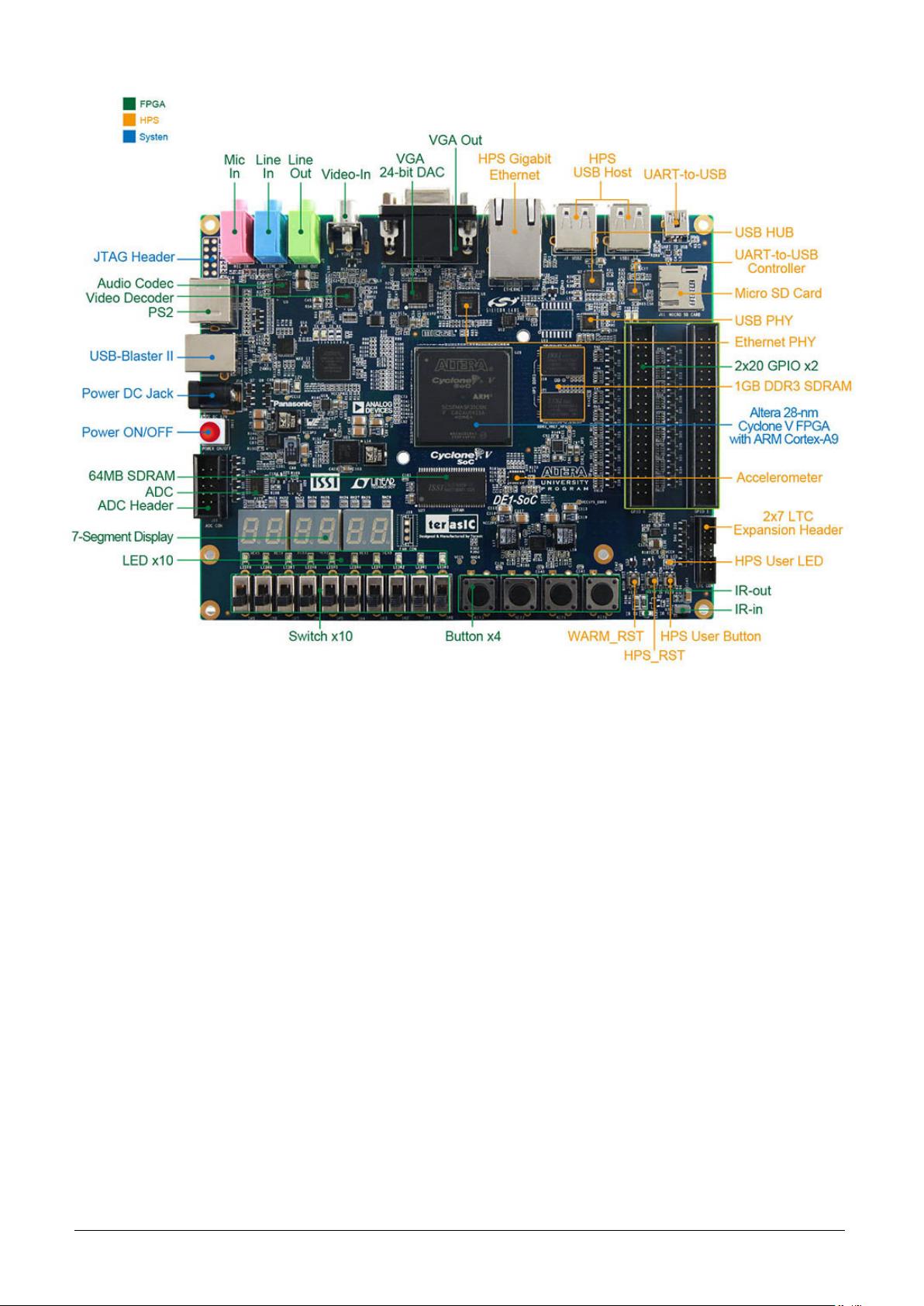

在SoCFPGA(System on Chip - Field Programmable Gate Array)设计中,整合了处理器系统和可编程逻辑,提供了高度集成的解决方案。DE1_SoC开发板是Terasic公司的一款基于Cyclone V SoC FPGA的平台,它包含了丰富的硬件资源,如FPGA器件、配置与调试模块、内存设备、通信接口、显示、音频、视频输入、模数转换器、开关、按钮、传感器以及电源等。这些硬件组件使得DE1_SoC成为了一个多功能的学习和开发平台。

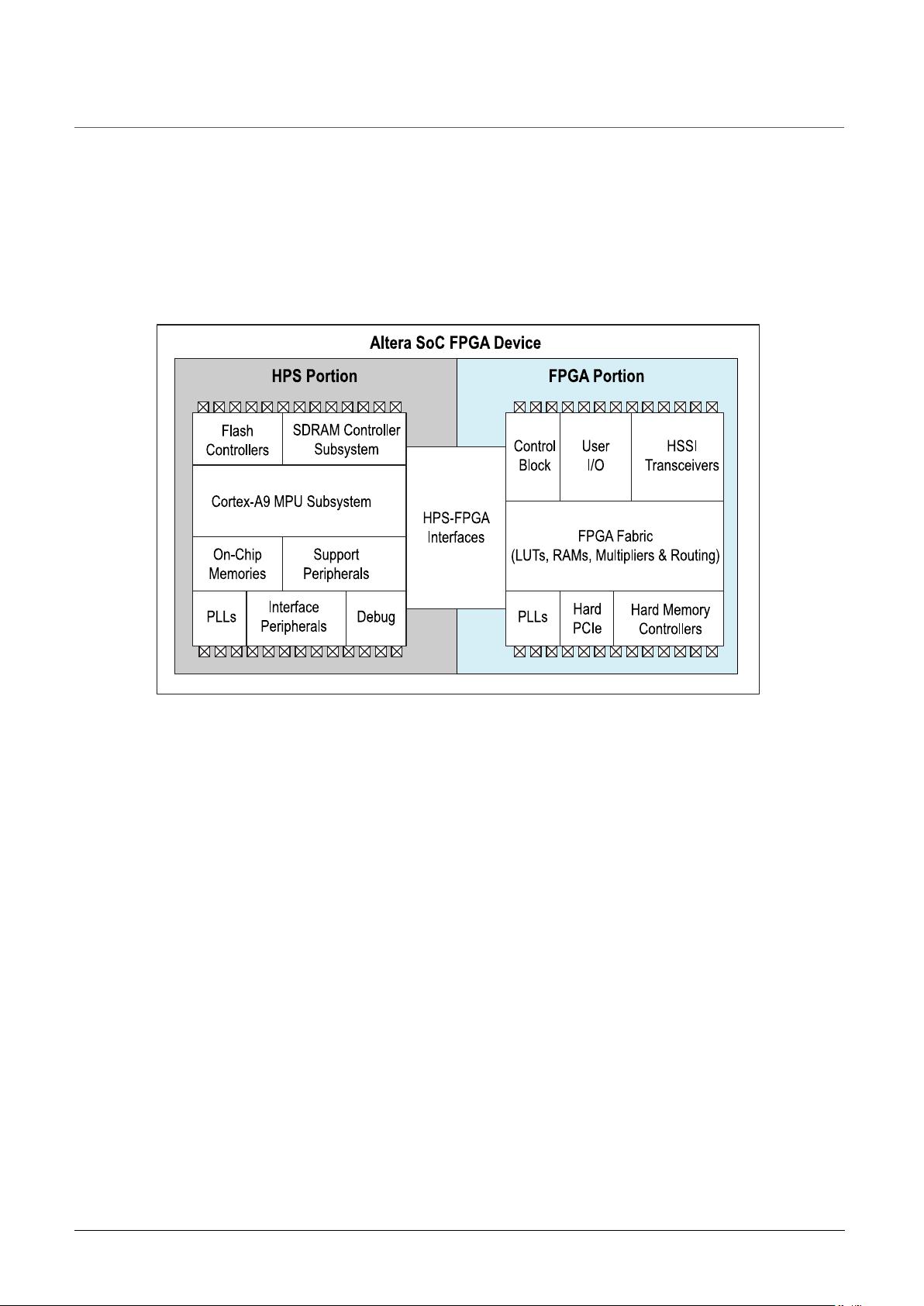

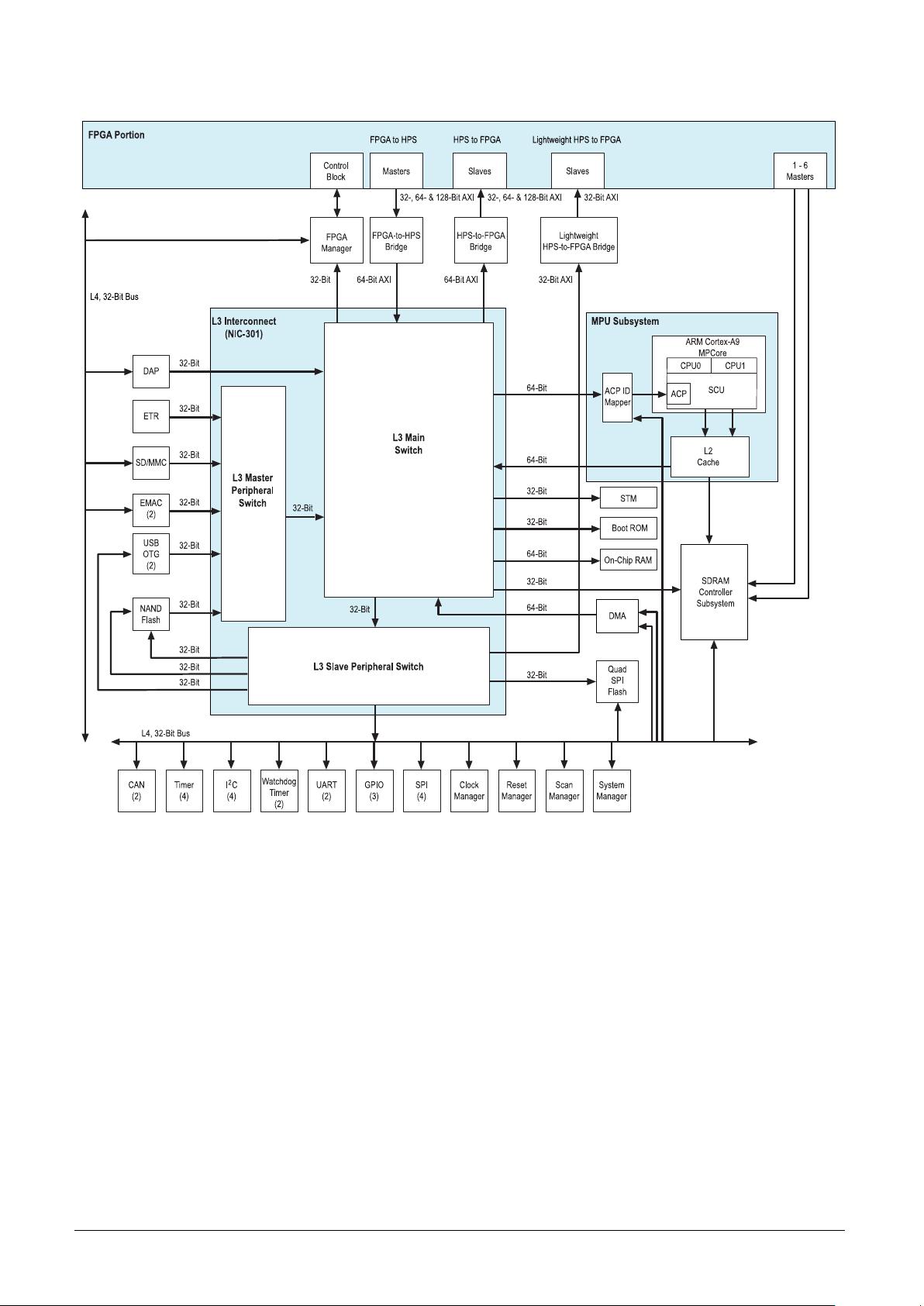

Cyclone V SoC是Altera(现Intel FPGA)推出的一种器件,它集成了一个Hard Processor System (HPS),这是一个基于ARM架构的处理器子系统,包括了高性能的MPU(Multi-Processing Unit)、SDRAM控制器以及一系列支持外围设备,如System Manager和FPGA Manager。System Manager负责管理HPS的配置和控制,而FPGA Manager则用于协调FPGA部分的编程和交互。

在软件方面,本教程可能涉及了用于开发和调试的软件版本,如Quartus Prime IDE、SDK(Software Development Kit)和其他必要的工具链。此外,还可能讨论了软件版本的选择和许可问题,这对于理解整个开发流程至关重要。

在学习SoC-FPGA设计时,开发者需要了解如何利用HPS进行嵌入式软件开发,同时也要掌握如何在FPGA部分实现自定义的硬件加速器或逻辑功能。这通常涉及到Verilog或VHDL等硬件描述语言,以及对HPS与FPGA间接口的理解,例如AXI总线协议。

本教程可能详细介绍了如何设置开发环境,包括硬件连接、软件安装、工程创建和配置,以及如何编写和编译HPS的软件代码,以及如何将这些代码与FPGA逻辑协同工作。对于初级开发者来说,这是一份非常有价值的参考资料,能够帮助他们快速入门SoCFPGA设计,理解硬件和软件的交互,并掌握DE1_SoC开发板的使用方法。

相关推荐

King-Five

- 粉丝: 145

- 资源: 4

最新资源

- E.rar_clamped inverter_e inverter_three level inverter_三电平电路_二极管

- images:图片

- apkUpdate:基于jfinal框架实现的一个APK更新系统

- .doom.d

- html5小鸟快飞游戏源码下载

- OlegMolchnovTutorial:追随

- 运行智能

- 非常实用的html5实现问答系统源码下载

- FennecBot

- 算法,算法工程师,matlab

- HibernateJPA_HerenciaSingleTable:简单表映射

- 通道打包:将纹理打包到图像RGBA通道中的软件

- eclipse中的hibernate插件

- find-home-ui

- AlphaTcl-开源

- 行业文档-设计装置-一种带通气孔的包装纸箱.zip