Interface Signal Groups

18 of 100 Denali Software DDR PHY Interface (DFI) Specification, Version 2.1

Copyright 1995-2009, 6/22/09

Denali Software, Inc.

The t

rddata_en

parameter defines the timing requirements between the read command on

the DFI interface and the assertion of the dfi_rddata_en signal at the DFI boundary for

the start of contiguous read data expected on the DFI interface. The exact value of this

parameter for a particular application is determined by the components in the entire

DRAM system. The DFI specification does not dictate a value but does require that

once this value has been determined, the dfi_rddata_en signal must be asserted based

on this timing parameter.

The t

phy_rdlat

parameter defines the maximum number of cycles allowed from the

assertion of the dfi_rddata_en signal to the assertion of the dfi_rddata_valid signal.

This parameter is specified by the system, but the exact value of this parameter is not

determined by the DFI specification.

These timing parameters (t

rddata_en

and t

phy_rdlat

) must be held constant while

commands are being executed on the DFI bus; however, if necessary, these values may

be changed when the bus is idle. These parameters work together to define a maximum

number of cycles from the assertion of a read command on the DFI control interface to

the assertion of the dfi_rddata_valid signal, indicating the first valid data of the

contiguous read data. Read data may be returned earlier by asserting the

dfi_rddata_valid signal before t

phy_rdlat

cycles have expired. When the signal

dfi_rddata_valid is asserted, the entire DFI read data word must be valid. For the

LPDDR2 DFI, the signal dfi_rddata_dnv must also be sent with the read data signal

dfi_rddata when the dfi_rddata_valid signal is asserted.

For frequency ratio systems, the read data enable signal will be replicated into phase-

specific signals with a suffix of “_pN” that defines the signal value for each phase N of

the DFI PHY clock relative to the DFI clock. The read data, read data valid and read

data not valid signals will be replaced with DFI data word-specific signals with a suffix

of “_wN” with the DFI data word N. For all signal types, the suffix for phase 0/word 0

is optional.

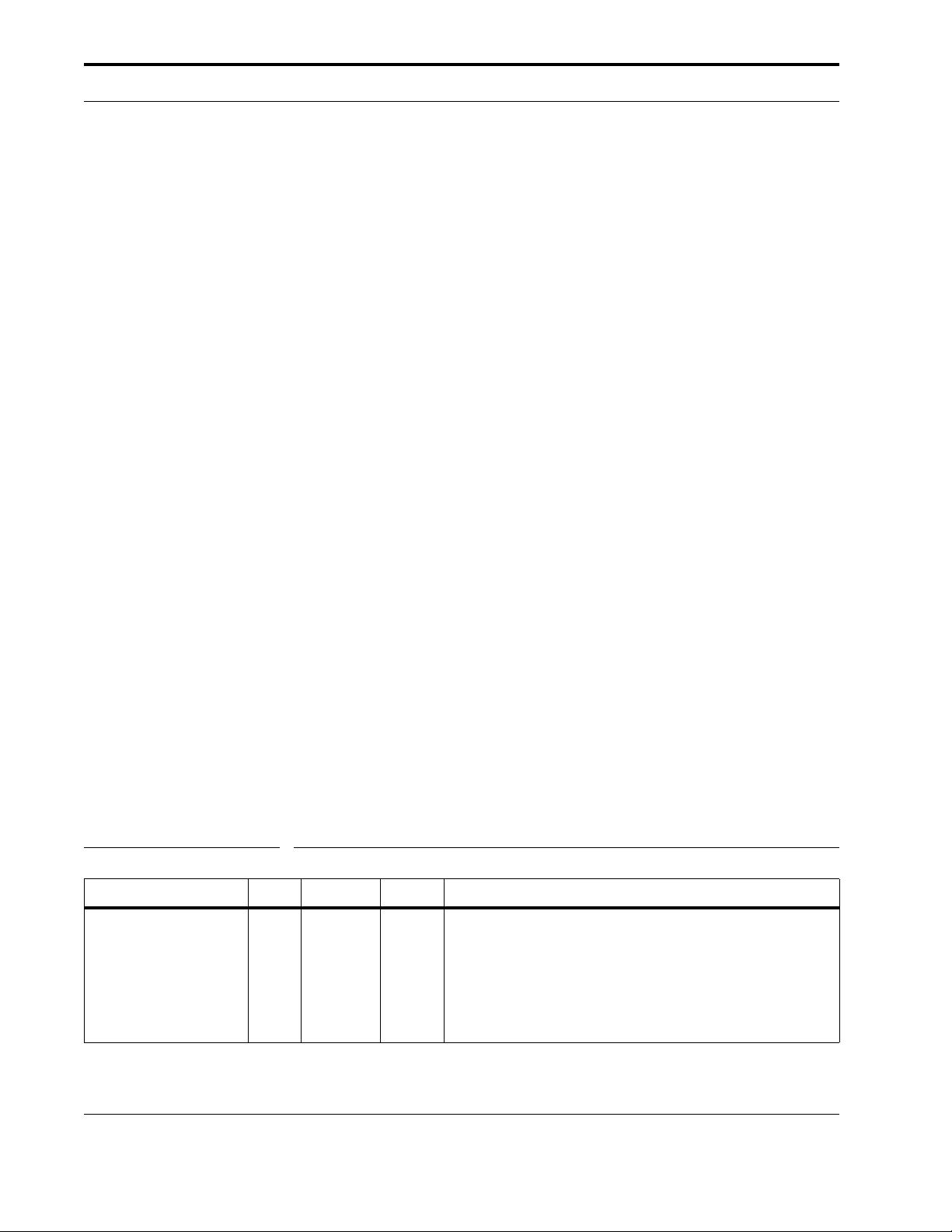

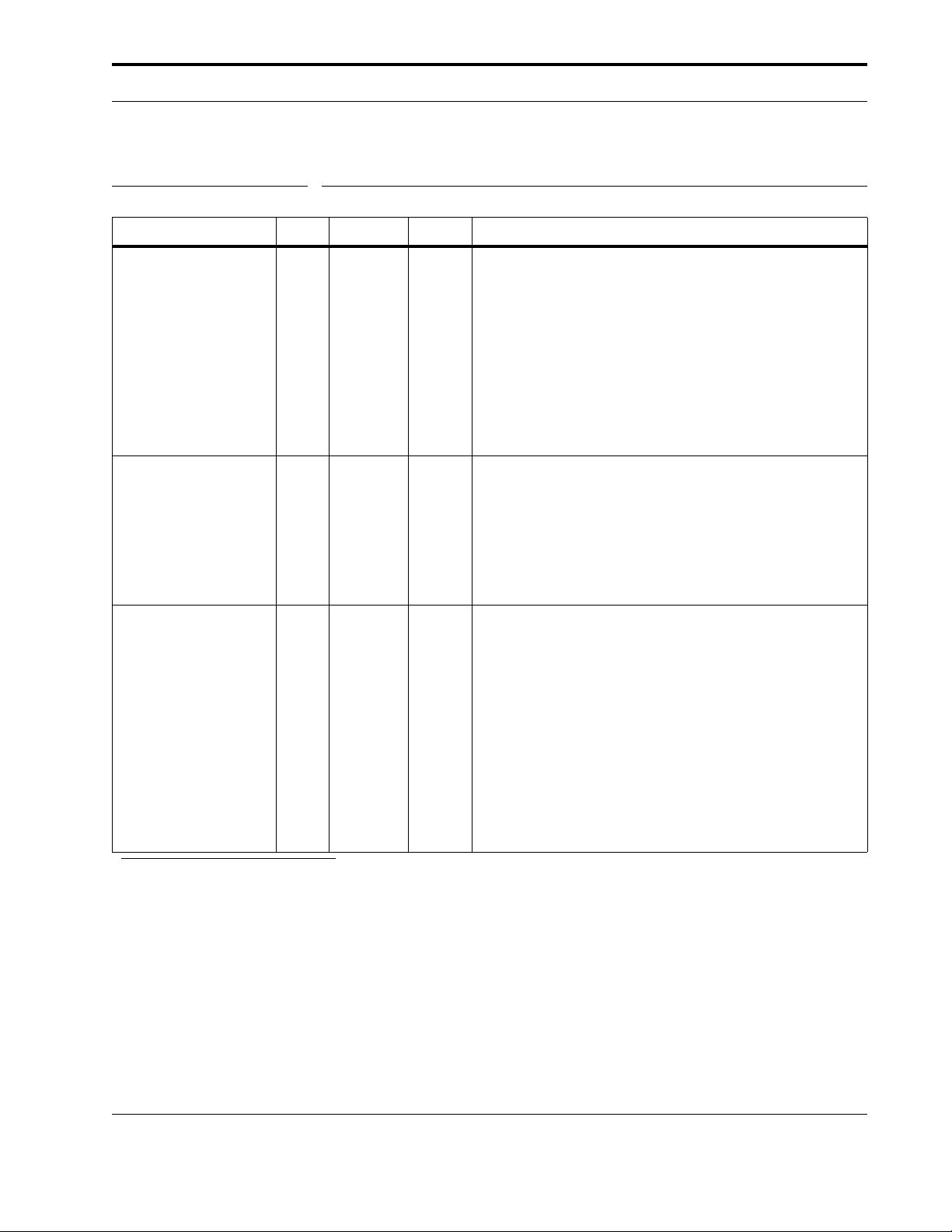

More information on the read data interface is provided in Section 4.4, “Read

Transactions”. The signals and parameters in the read data interface are listed in Table 6

and Table 7.

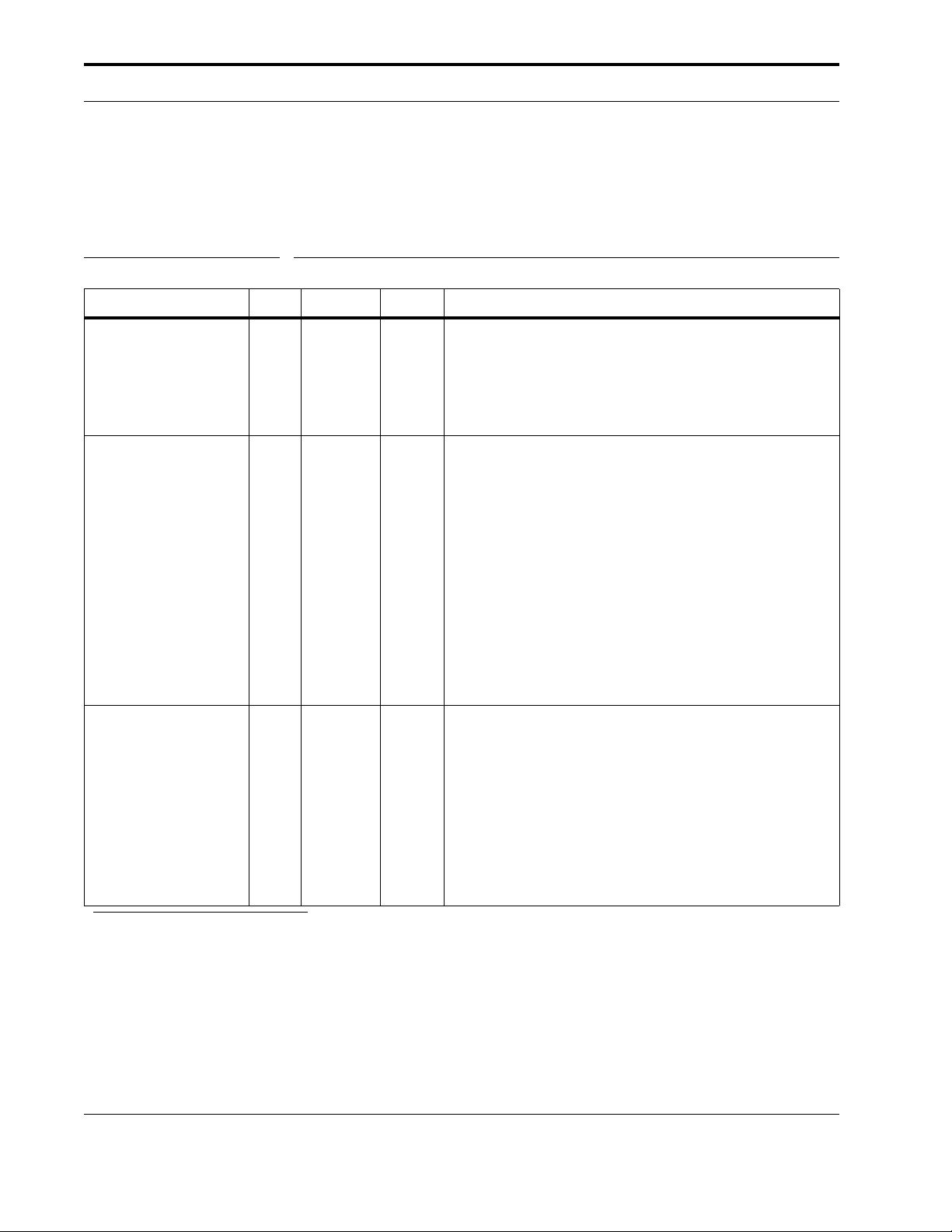

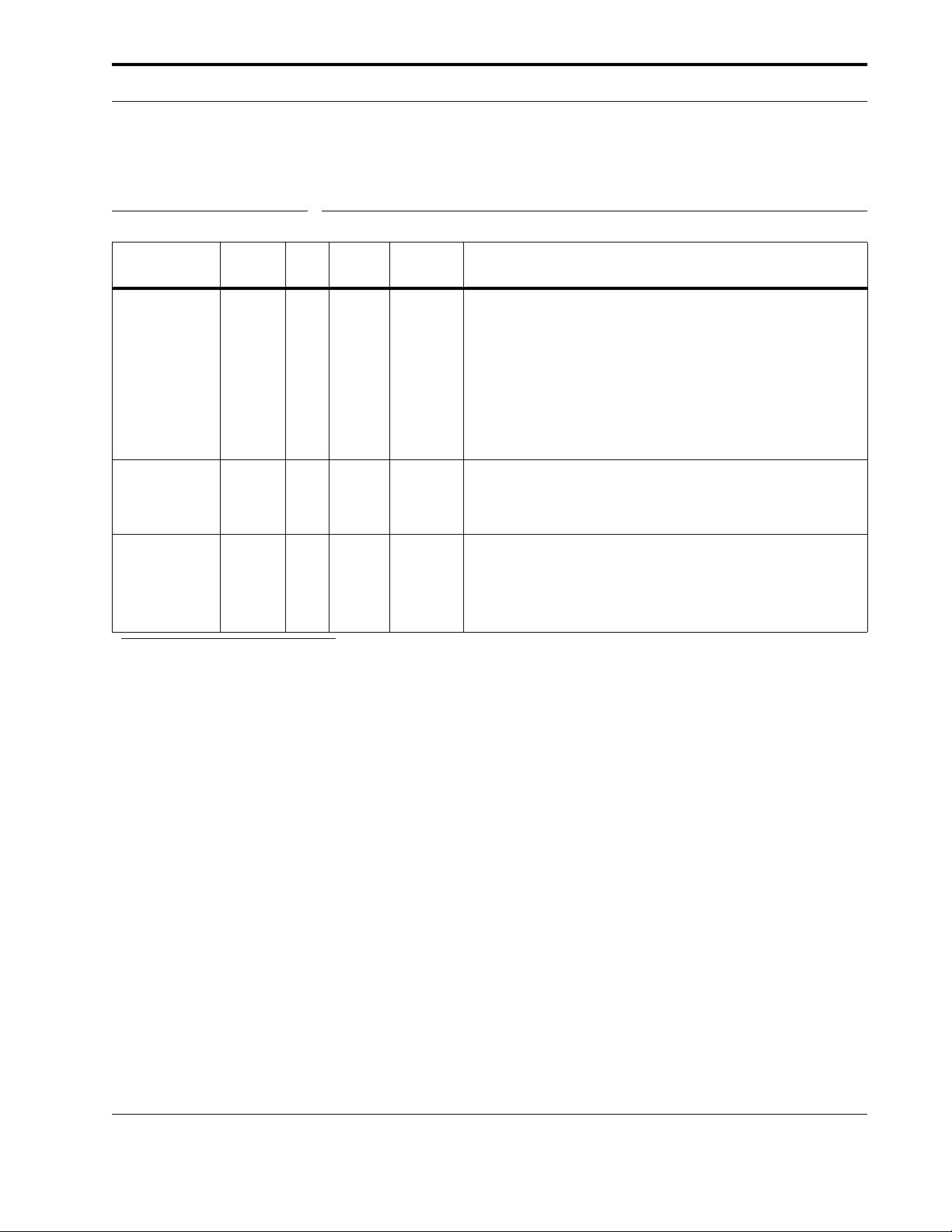

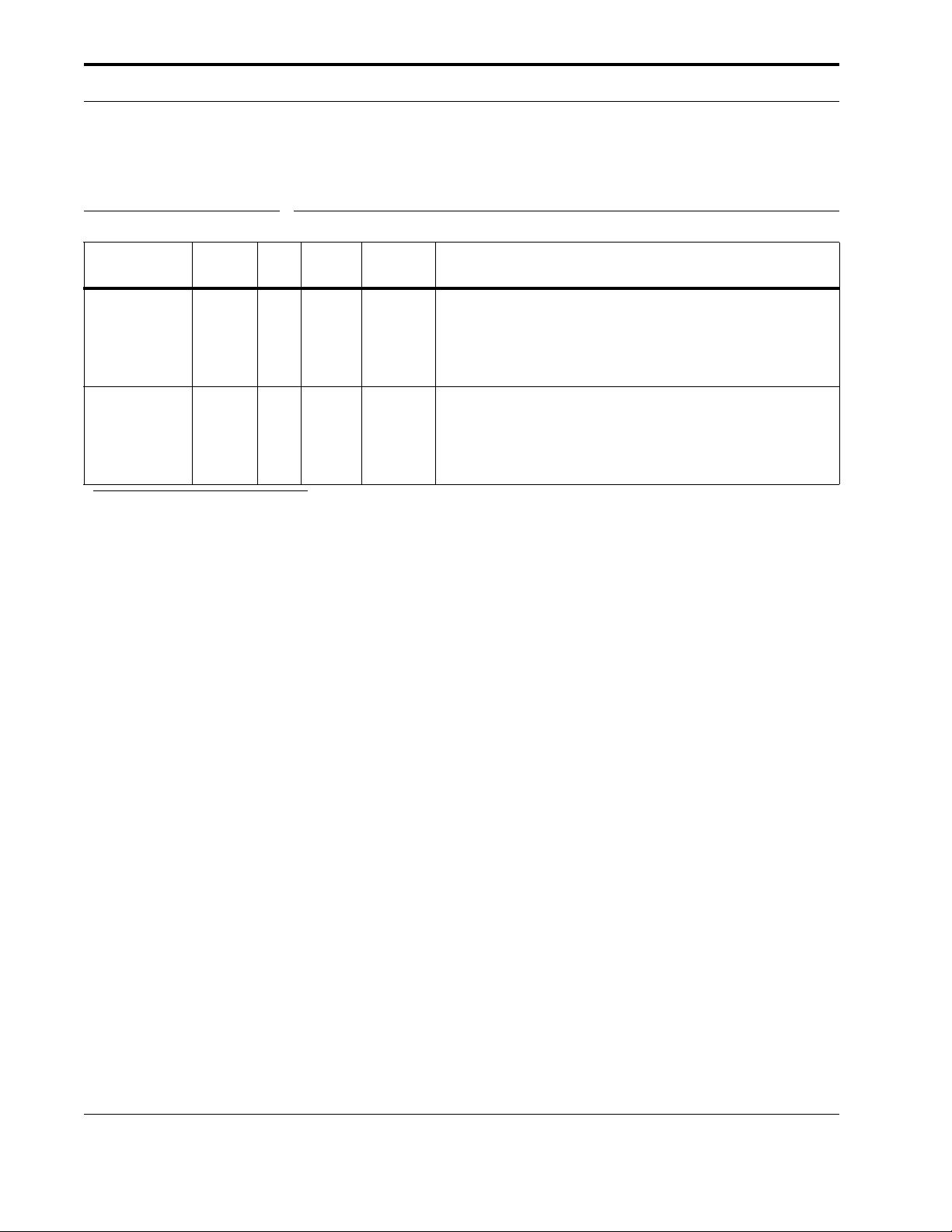

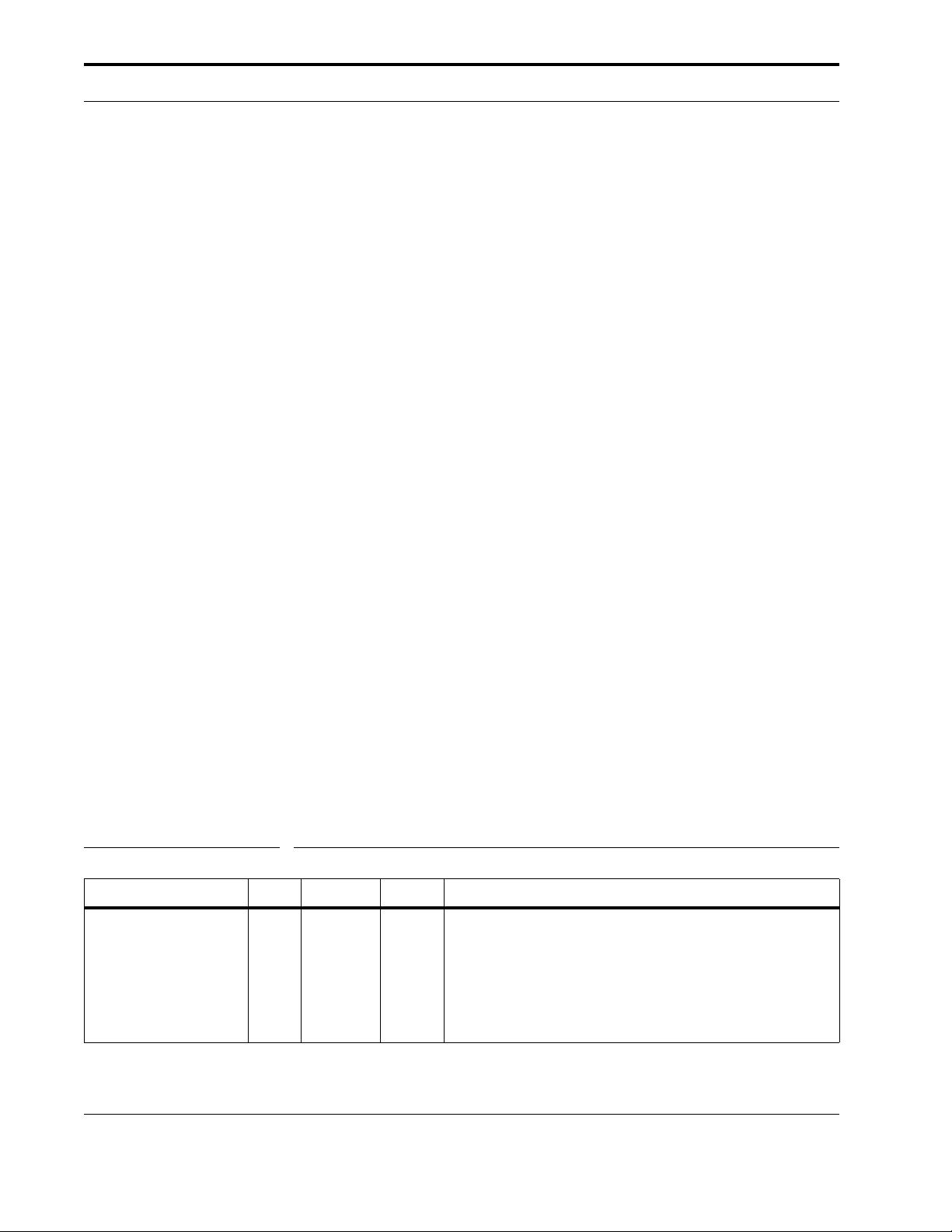

TABLE 6. Read Data Signals

Signal From Width Default Description

dfi_rddata

or dfi_rddata_wN

PHY DFI Data

Width

-

a

Read data bus. Read data is expected to be received at the MC

within t

phy_rdlat

cycles after the dfi_rddata_en signal is asserted.

For frequency ratio systems, the read data bus will be replicated

into DFI data word-specific dfi_rddata_wN buses that define the

read data for each DFI data word. For a 1:2 frequency ratio system,

there are 2 dfi_rddata_wN signals. For a 1:4 frequency ratio

system, there are 4 dfi_rddata_wN signals.