MAX9288/MAX9290 3.12Gbps GMSL Deserializers

for Coax or STP Input and MIPI CSI-2 Output

www.maximintegrated.com

Maxim Integrated

│

20

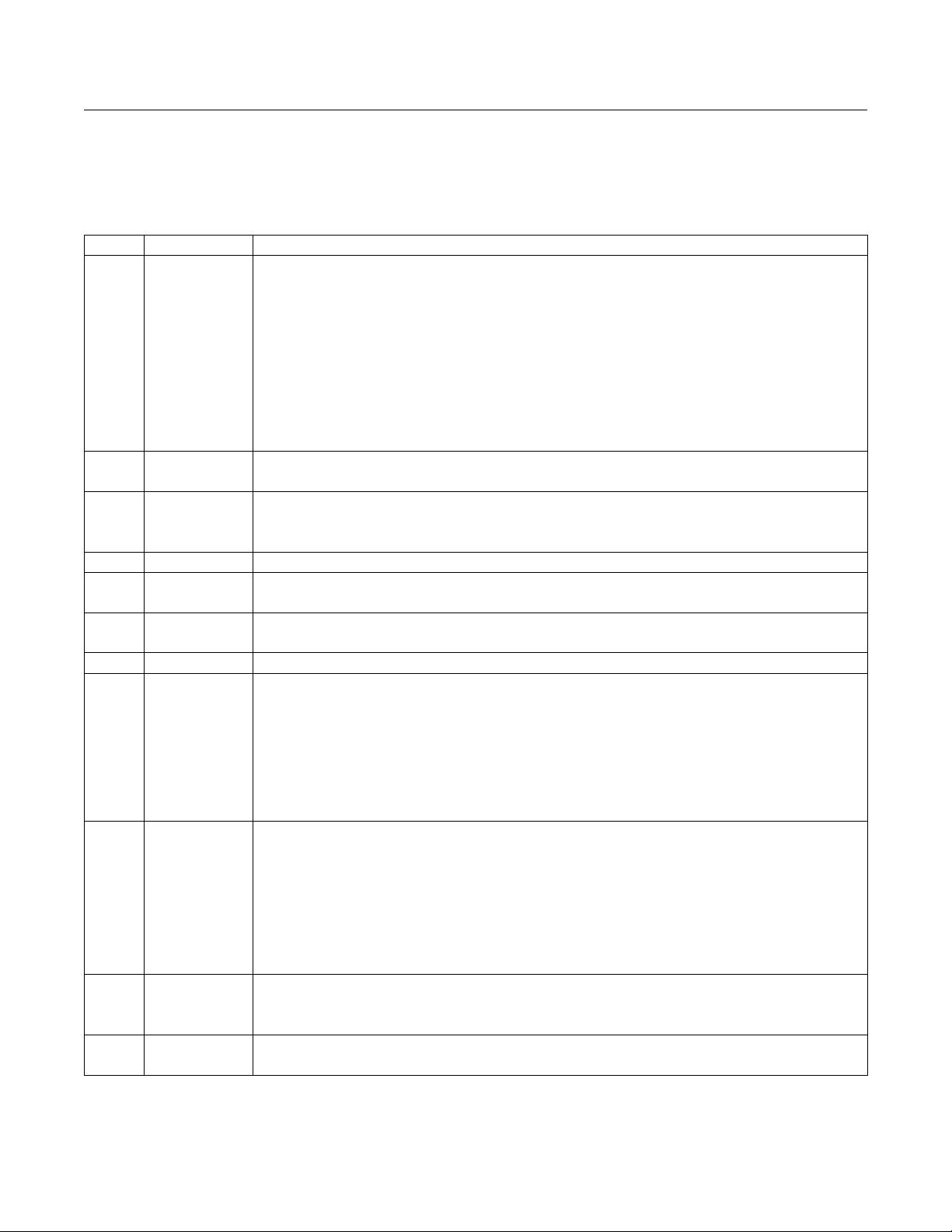

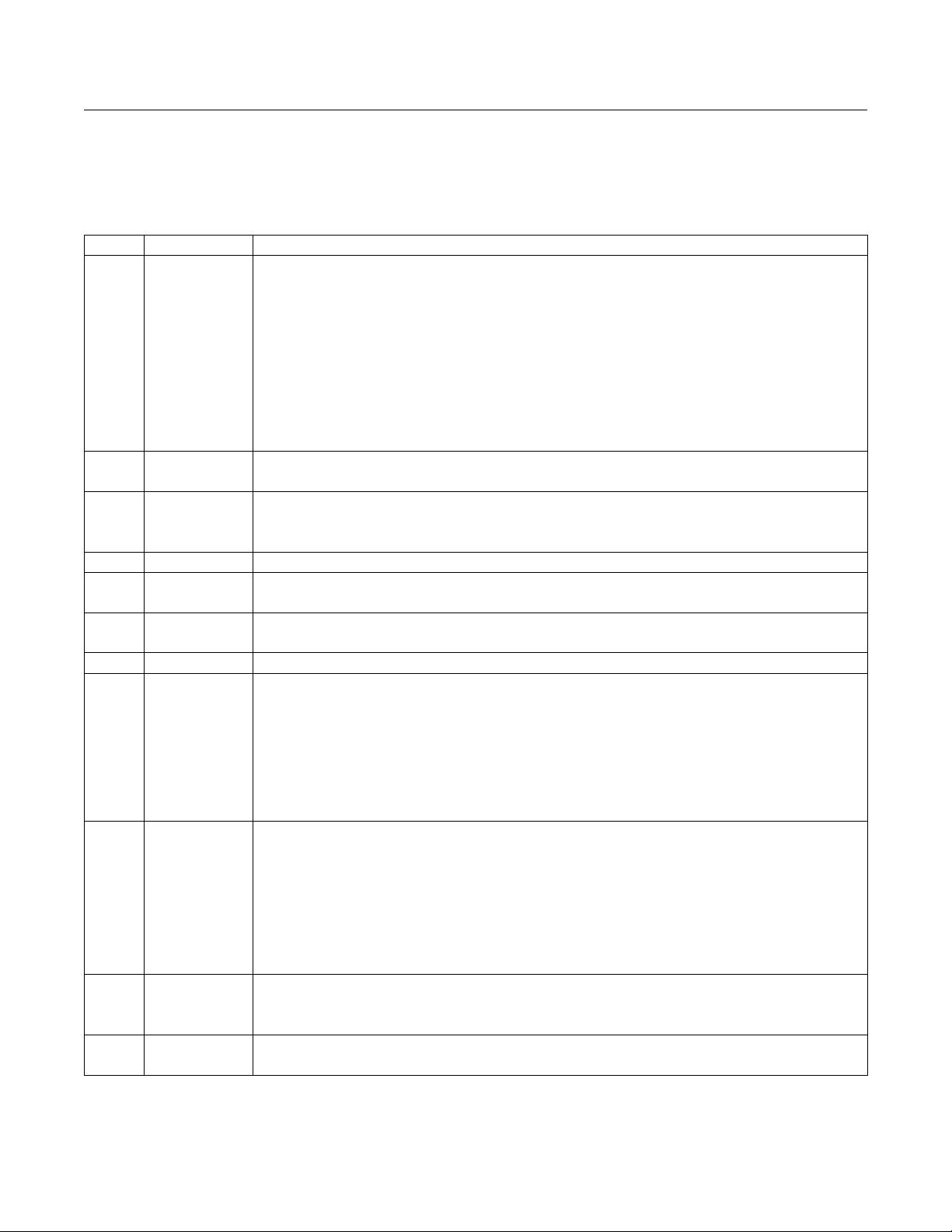

PIN NAME FUNCTION

20 HIM/CNTL1

High-Immunity Mode Input/Auxiliary Control Signal Output With Internal Pulldown to EP. Functions

as HIM input at power-up or when resuming from power-down mode (PWDN = low), and switches to

CNTL2 output automatically after power-up.

HIM: Default HIGHIMM bit value is latched at power-up or when resuming from power-down mode

(PWDN = low) and is active-high. Connect HIM/CNTL1 to IOVDD with a 30kΩ resistor to set high or

leave open to set low. HIGHIMM can be programmed to a different value after power-up. HIGHIMM in

the serializer must be set to the same value.

CNTL1: Used only in 32-bit and high-bandwidth mode (BWS = high, open). CNTL1 is mapped from the

GMSL serializer’s CNTL1, DIN27, or RES input.

21, 43 IOVDD

I/O Supply Voltage. 1.8V to 3.3V logic I/O power supply. Bypass IOVDD to EP with 0.1µF and 0.001µF

capacitors as close as possible to the device with the smallest value capacitor closest to IOVDD.

22 CDS

Control Direction Selection Input, with Internal Pulldown to EP. Control link direct selection input

with internal pulldown to EP. Set CDS = low when the control channel master µC is connected at the

serializer. Set CDS = high when the control channel master µC is connected at the deserializer.

24 RES Reserved. Leave unconnected

25, 36 AVDD18

1.8V Analog Power Supply. Bypass AVDD18 to EP with 0.1µF and 0.001µF capacitors as close as

possible to the device with the smaller capacitor closest to AVDD18.

26–29,

32–35

DOUT_+,

DOUT_-

CSI-2 Data Outputs

30, 31 CLK+, CLK- CSI-2 Clock Output

38 ADD1/CNTL3

Auxiliary Control Signal Output/Address Selection Input, with Internal Pulldown to EP. Functions as

ADD1 input at power-up or when resuming from power-down mode (PWDN = low), and switches to

CNTL3 output automatically after power-up.

ADD1: Bit value is latched at power-up or when resuming from power-down mode (PWDN = low). See

Table 1. Connect ADD1/CNTL3 to IOVDD with a 30kΩ resistor to set high or leave open to set low.

CNTL3: Used only in high-bandwidth mode (BWS = open.

39 ADD0/CNTL0

Auxiliary Control Signal Output/Address Selection Input, with Internal Pulldown to EP. Functions as

ADD0 input at power-up or when resuming from power-down mode (PWDN = low), and switches to

CNTL0 output automatically after power-up.

ADD0: Bit value is latched at power-up or when resuming from power-down mode (PWDN = low).

See Table 1. Connect ADD0/CNTL0 to IOVDD with a 30kΩ resistor to set high or leave open to set low.

CNTL0: Used only in high-bandwidth mode (BWS = open).

40 LOCK

Open-Drain Lock Output, with Internal 60kΩ Pullup to IOVDD. LOCK = high indicates that PLLs are

locked with correct serial-word-boundary alignment. LOCK = low indicates that PLLs are not locked or

an incorrect serial-word-boundary alignment. LOCK is high when PWDN = low.

41 ERR

Error Output. Open-drain data error detection and/or correction indication output with internal 60kΩ

pullup to IOVDD. ERR is high when PWDN is low.

Pin Description (continued)