Virtex-5 FPGA 实现高性能 DDR2 SDRAM 接口设计

下载需积分: 50 | PDF格式 | 1.01MB |

更新于2024-07-28

| 100 浏览量 | 举报

"这篇应用笔记(XAPP858 v2.1)主要介绍了在Virtex®-5设备中实现的高性能DDR2 SDRAM接口。它利用Xilinx的内存接口生成器(MIG)工具可以定制此参考设计。"

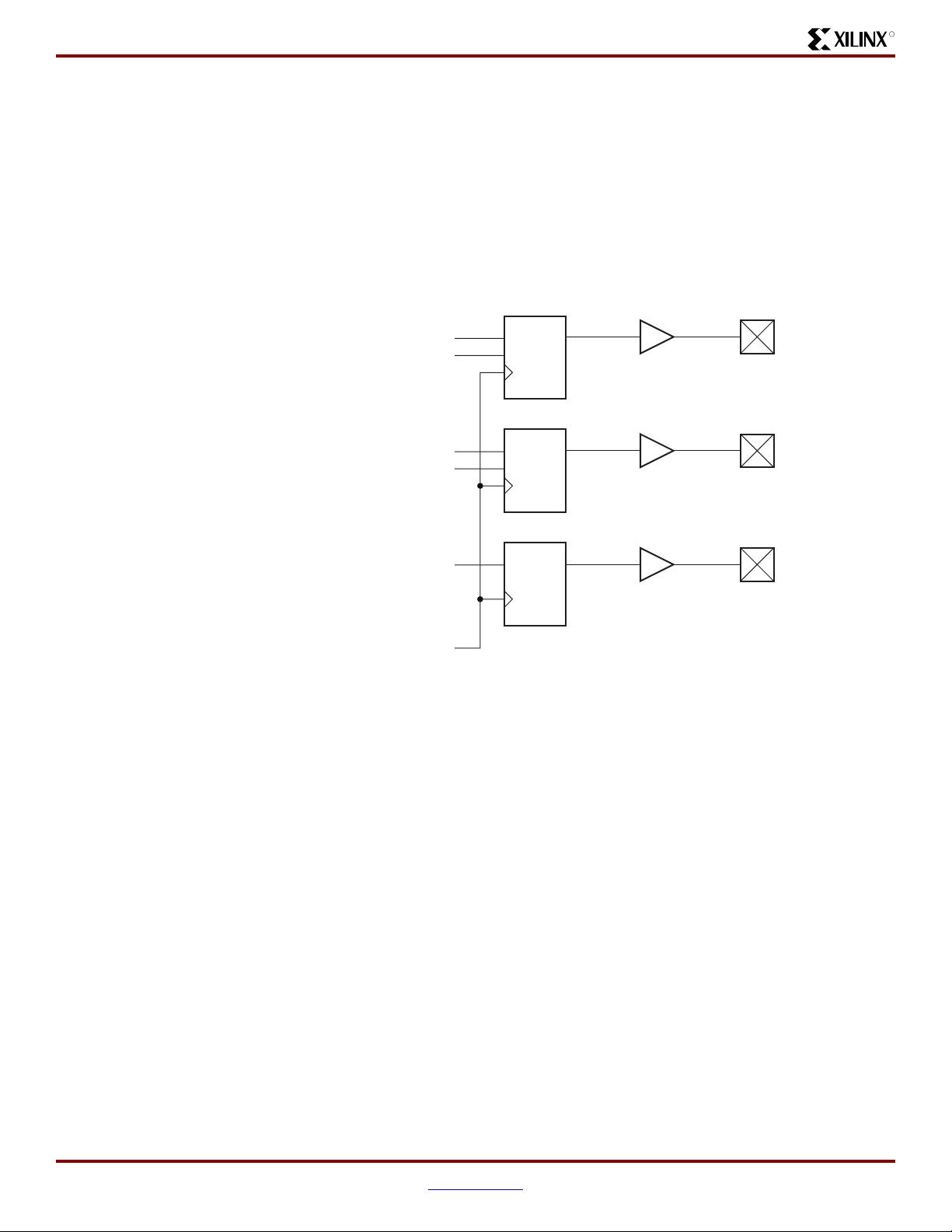

DDR2 SDRAM 接口在高速数据传输中的关键作用在于其源同步的特性。在读取操作中,数据和时钟信号( strobe)以边缘对齐的方式同时传输。为了在Virtex-5 FPGA中捕捉这些传输的数据,设计中采用了两种策略:一种是延迟 strobe 信号来捕获读取数据,另一种是在FPGA的时钟域中通过输入双数据速率(IDDR)和可配置逻辑块(CLB)的 flip-flops 再次捕获数据。

DDR2 SDRAM 技术概述

DDR2 SDRAM 是DDR SDRAM系列的下一代产品,采用SSTL1.8V I/O标准。其特点包括:

1. **双倍数据速率**:与传统的DDR内存相比,DDR2内存能在一个时钟周期内传输两次数据,即上升沿和下降沿都传输数据,显著提高了内存带宽。

2. **更低的电压**:DDR2 SDRAM 使用1.8V的工作电压,相比于DDR SDRAM的2.5V,降低了功耗,同时保持了高性能。

3. **更严格的时序**:DDR2 SDRAM有更精密的时序要求,这需要更复杂的接口设计来确保数据正确传输。

4. **预充电时间优化**:DDR2内存增加了4个bank,每个bank都可以独立地预充电,提高了并发操作的能力,从而提高了整体系统性能。

5. **ODT(On-Die Termination)**:内部集成的终端电阻,可以减少信号反射,提高信号完整性,尤其在长数据总线中更为重要。

6. **ZQ校准**:DDR2 SDRAM引入了ZQ引脚,用于系统内校准终端电阻,确保数据传输的准确性和稳定性。

设计实现

在Virtex-5 FPGA中实现DDR2 SDRAM接口,需要考虑以下关键点:

- **内存接口生成器(MIG)**:Xilinx的MIG工具提供了一种自动化的流程,帮助用户快速生成针对特定DDR2 SDRAM设备的接口IP核,简化了设计流程。

- **IDDR模块**:输入双数据速率模块用于在FPGA内部处理时钟和数据的同步,将边缘对齐的数据转换为内部时钟域中的数据。

- **CLB Flip-flops**:配置逻辑块中的触发器用于存储和重新采样从DDR2 SDRAM读取的数据,确保数据在FPGA内部的稳定传输。

- **时钟管理**:由于DDR2 SDRAM的时钟和数据是源同步的,因此需要精确的时钟管理和相位调整来确保数据的正确捕获。

- **错误检测与纠正**:可能需要添加额外的错误检测和纠正机制,如奇偶校验或ECC(错误校验码),以提高系统可靠性。

Virtex-5 FPGA中的DDR2 SDRAM接口设计涉及到多个复杂的技术层面,包括接口同步、数据转换、时钟管理以及错误处理。通过利用Xilinx的MIG工具,设计师能够高效地创建出满足高性能需求的DDR2 SDRAM系统。

js2luyao

- 粉丝: 0

最新资源

- 全面详实的大学生电工实习报告汇总

- 利用极光推送实现App间的消息传递

- 基于JavaScript的节点天气网站开发教程

- 三星贴片机1+1SMT制程方案详细介绍

- PCA与SVM结合的机器学习分类方法

- 钱能版C++课后习题完整答案解析

- 拼音检索ListView:实现快速拼音排序功能

- 手机mp3音量提升神器:mp3Trim使用指南

- 《自动控制原理第二版》习题答案解析

- 广西移动数据库脚本文件详解

- 谭浩强C语言与C++教材PDF版下载

- 汽车电器及电子技术实验操作手册下载

- 2008通信定额概预算教程:快速入门指南

- 流行的表情打分评论特效:实现QQ风格互动

- 使用Winform实现GDI+图像处理与鼠标交互

- Python环境配置教程:安装Tkinter和TTk