FPGA实现的可配置SPI主控接口设计与测试

114 浏览量

更新于2024-08-30

1

收藏 274KB PDF 举报

"该文介绍了一种基于FPGA的可配置SPI Master接口设计,旨在满足不同测试场景的需求,包括正常操作、异常情况以及强度测试。设计采用Verilog语言实现,确保了SPI接口的高度灵活性和可配置性。文章还强调了在FPGA广泛应用于各个领域背景下,其可靠性和可测试性的关键性,以及由此带来的测试挑战。FPGA的测试分为面向制造的测试过程(MTP)和面向应用的测试过程(ATP),本文重点探讨了在ATP中的SPI Master模型建立。"

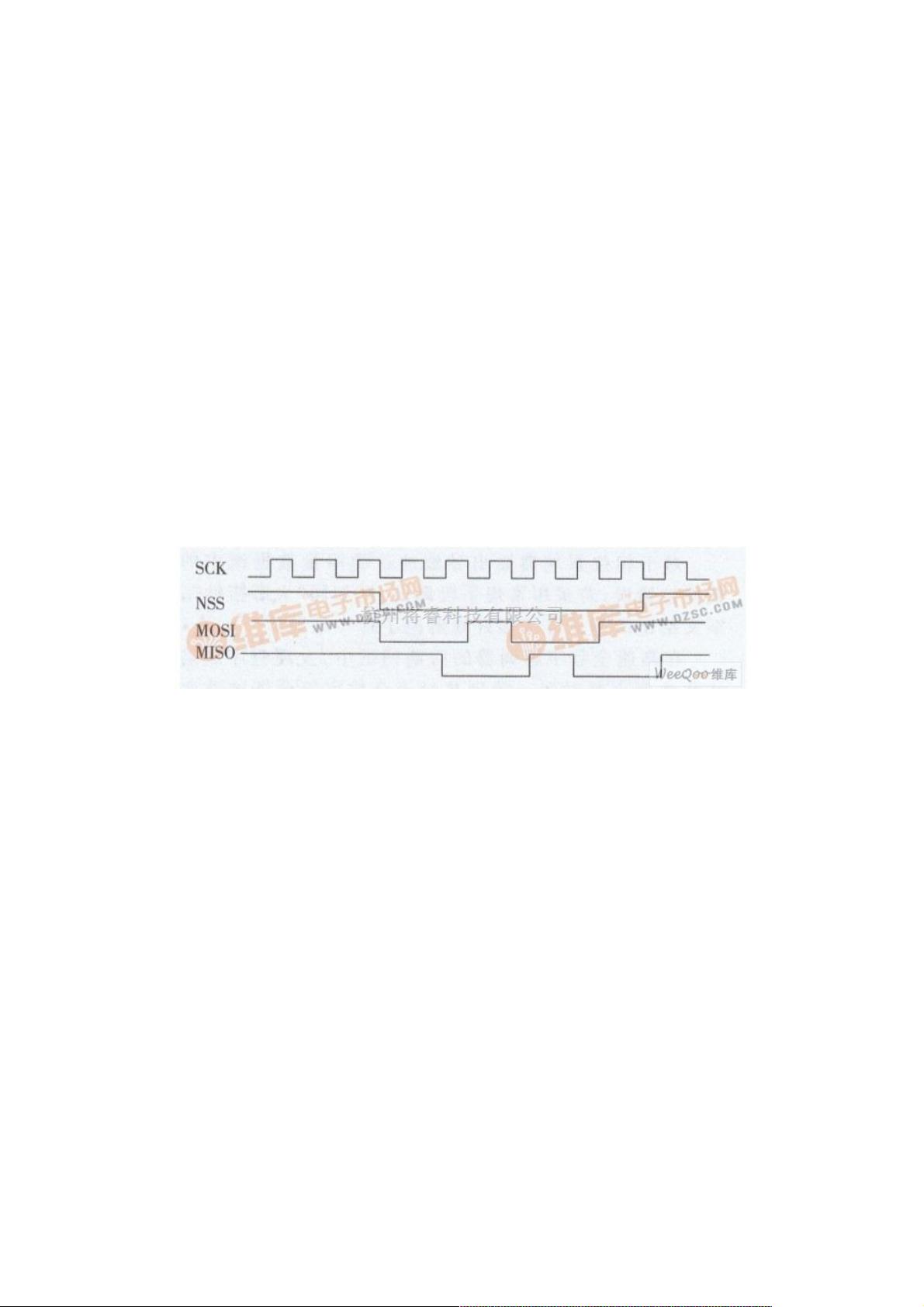

SPI(Serial Peripheral Interface)是一种广泛应用的同步串行通信协议,它支持全双工通信,通常由四个信号线组成:主设备输入/从设备输出(MISO)、主设备输出/从设备输入(MOSI)、串行时钟(SCLK)和从设备选择(SS)。SPI的工作模式为主-从架构,一个主设备可以控制多个从设备,通信效率高,且只需少量的物理连接,这使得SPI在嵌入式系统和微控制器应用中非常受欢迎。

在设计SPI Master模块时,需要考虑以下几个关键点:

1. 时钟控制:SPI通信依赖于主设备提供的时钟信号SCLK,时钟极性和时钟相位(CPOL和CPHA)的选择决定了数据在时钟边沿的上升还是下降时刻被采样。这种灵活性允许适应不同的从设备。

2. 从设备选择:通过SS线,主设备可以选择与哪个从设备进行通信,通常是低电平有效,意味着当SS线被拉低时,对应的从设备开始接收或发送数据。

3. 数据传输:MOSI和MISO线用于数据传输,主设备通过MOSI线发送数据,从设备通过MISO线回传数据。在全双工模式下,数据可以同时发送和接收。

4. 数据格式:SPI支持8位到16位的数据传输宽度,数据传输的顺序(MSB First或LSB First)可以根据需要配置。

5. 配置灵活性:文中提到的SPI Master设计允许配置不同的参数,如传输速率、数据宽度、通信模式等,以适应各种应用场景和测试条件。

在FPGA测试中,SPI Master接口扮演着重要角色。它能够模拟不同的通信条件,对设计电路进行实时性能验证,检查其在不同工作状态下的稳定性。对于面向应用的测试(ATP),SPI Master接口可以配置为特定的测试模式,更有效地找出潜在的硬件或逻辑错误。

利用Verilog这样的硬件描述语言实现SPI Master,设计师可以精确地控制通信过程,编写测试向量,对FPGA内部逻辑进行深入的测试。这种方法对于发现设计中的隐藏缺陷,提升FPGA设计的可靠性和测试覆盖率至关重要。

该设计实现了基于FPGA的可配置SPI Master接口,不仅提高了测试的灵活性,还降低了测试成本,为FPGA的可靠性和可测试性提供了有效的解决方案。在实际应用中,这样的接口设计有助于确保FPGA在商业、军事、航空航天等领域中运行的稳定性和高效性。

2021-07-13 上传

2022-05-23 上传

2021-07-13 上传

2021-07-13 上传

2021-08-15 上传

2023-12-23 上传

2021-09-30 上传

2021-11-20 上传

2012-01-12 上传

weixin_38690089

- 粉丝: 5

- 资源: 924

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍