数字IC设计中的DFT基础与测试重要性

需积分: 50 72 浏览量

更新于2024-07-22

4

收藏 582KB PDF 举报

"本文介绍了数字集成电路设计中的DFT(Design for Testability)技术,重点讨论了测试在半导体产品实现过程中的重要性以及测试的基本定义。"

在数字集成电路设计中,DFT是一个关键的概念,旨在使设计易于测试,从而提高产品质量和降低制造成本。DFT策略贯穿于整个设计流程,确保在产品开发的不同阶段可以有效地检测和识别潜在的问题。

1. 设计过程中的DFT:

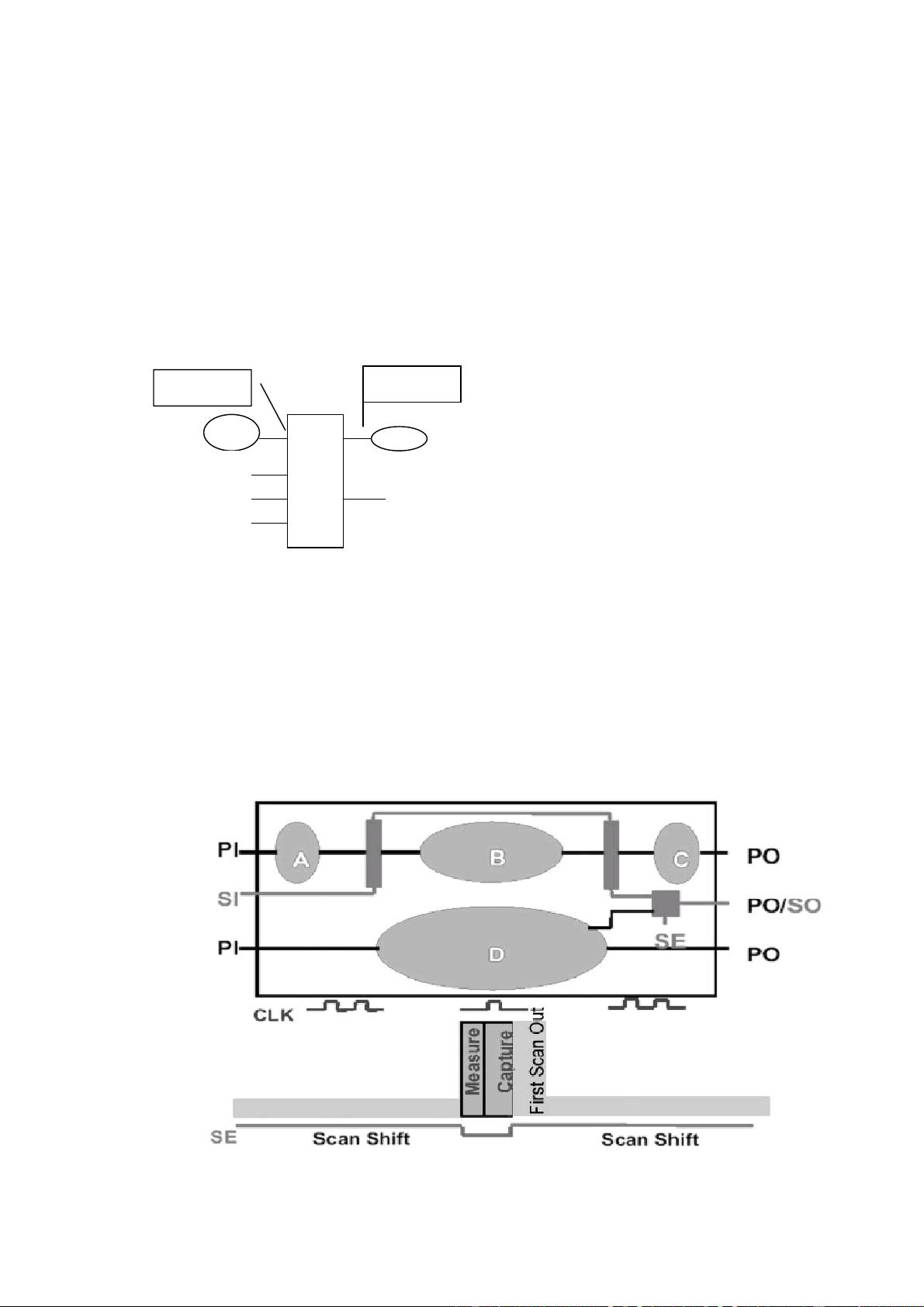

设计阶段通常从编写硬件描述语言(HDL,如Verilog或VHDL)代码开始,可以是寄存器传输级(RTL)或门级描述。在RTL级,通过逻辑综合和验证将设计转化为门级网表,随后进行布局布线生成版图。DFT在此阶段涉及添加测试结构,如扫描链,边界扫描等,这些结构使得在制造后能够对电路进行有效的功能测试和故障诊断。

2. 制造和测试:

制造过程中,设计的版图数据被转化为掩模,用于生产晶圆。晶圆经过制造过程后,会包含多个裸片。晶圆测试是确保只有合格的裸片进入下一步封装的关键步骤。未通过测试的裸片会被淘汰,而通过测试的裸片则会被封装成芯片。

3. 芯片测试与半导体产品测试:

封装后的芯片需要进一步的测试以确认其无故障。测试包括应用特定的激励信号(测试向量)到输入端,观察并比较输出端的实际响应与期望响应,以此来确定电路是否正常工作。测试模式不仅包含激励信号,还包含期望的响应,用于验证电路性能和时序。

4. 测试模式与测试向量:

测试向量仅包含激励信号,而测试模式包含激励和期望响应。测试设备生成测试向量,控制被测电路并检测响应。如果检测到的实际响应与期望响应不符,就表明可能存在故障。测试模式的生成和验证是测试设计的关键部分,确保测试的有效性和完整性。

DFT是数字集成电路设计中不可或缺的一部分,它通过在设计早期集成测试结构,简化了后期测试流程,提高了故障检测效率,降低了生产成本,并确保了最终产品的质量和可靠性。

546 浏览量

2582 浏览量

224 浏览量

687 浏览量

164 浏览量

2022-09-23 上传

430 浏览量

qsfighting

- 粉丝: 1

最新资源

- 仿京东商城的Asp网购系统代码实现

- 新版人生重开模拟器:微信小程序源码探究

- 四选一视音频切换器技术改造详解

- Android动态壁纸演示与实例分析

- 使用LINQ实现的简易.NET留言板教程

- 《C++ Primer中文版第五版》:高清学习资源

- STM32通过RS485接口读取MODBUS传感器数据教程

- HolaMundoDeColores与MonoGame入门教程

- OpenCV编译必备:FFmpeg合集下载与安装指南

- TI TMS320F28335定时器中断源代码解读与优化

- PyTorch-Kaldi 项目源码核心注释解析

- 打造基于Arduino与树莓派的语音控制机器人手臂

- C#与WPF打造矩阵风格数字雨效果

- STM32标准库函数V3.5.0:掌握最新官方库

- 设计大功率D类音频放大器的关键技术

- MySQL 8.0官方文档的详细阅读指南