P

P

r

r

e

e

l

l

i

i

m

m

i

i

n

n

a

a

r

r

y

SPFD5408B

© ORISE Technology Co., Ltd.

Proprietary & Confidential

15

OCT. 29, 2007

Preliminary Version: 0.1

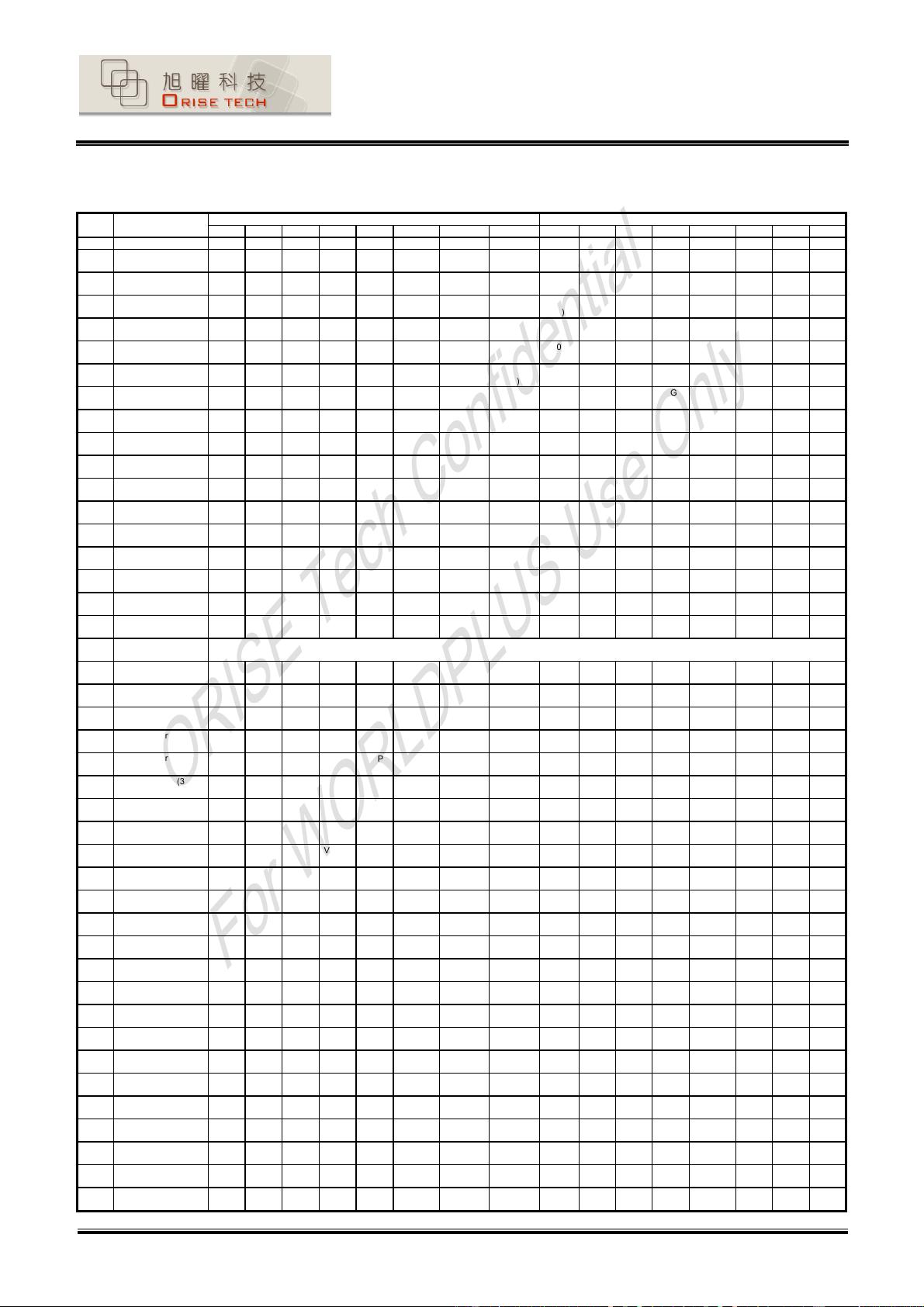

61h Driver Output Control 0 0 0 0 0 0 0 0 0 0 0 0 0 NDL

(0)

VLE

(0)

REV

(0)

6Ah Vertical Scroll Control 0 0 0 0 0 0 0 VL8

(0)

VL7

(0)

VL6

(0)

VL5

(0)

VL4

(0)

VL3

(0)

VL2

(0)

VL1

(0)

VL0

(0)

80h Display Position -

Partial Display 1

0 0 0 0 0 0 0 PTDP08

(0)

PTDP07

(0)

PTDP06

(0)

PTDP05

(0)

PTDP04

(0)

PTDP03

(0)

PTDP02

(0)

PTDP01

(0)

PTDP00

(0)

81h RAM Address Start -

Partial Display 1

0 0 0 0 0 0 0 PTSA08

(0)

PTSA07

(0)

PTSA06

(0)

PTSA05

(0)

PTSA04

(0)

PTSA03

(0)

PTSA02

(0)

PTSA01

(0)

PTSA00

(0)

82h RAM Address End -

Partial Display 1

0 0 0 0 0 0 0 PTEA08

(0)

PTEA07

(0)

PTEA06

(0)

PTEA05

(0)

PTEA04

(0)

PTEA03

(0)

PTEA02

(0)

PTEA01

(0)

PTEA00

(0)

83h Display Position -

Partial Display 2

0 0 0 0 0 0 0 PTDP18

(0)

PTDP17

(0)

PTDP16

(0)

PTDP15

(0)

PTDP14

(0)

PTDP13

(0)

PTDP12

(0)

PTDP11

(0)

PTDP10

(0)

84h RAM Address Start -

Partial Display 2

0 0 0 0 0 0 0 PTSA18

(0)

PTSA17

(0)

PTSA16

(0)

PTSA15

(0)

PTSA14

(0)

PTSA13

(0)

PTSA12

(0)

PTSA11

(0)

PTSA10

(0)

85h RAM Address End -

Partial Display 2

0 0 0 0 0 0 0 PTEA18

(0)

PTEA17

(0)

PTEA16

(0)

PTEA15

(0)

PTEA14

(0)

PTEA13

(0)

PTEA12

(0)

PTEA11

(0)

PTEA10

(0)

90h Panel interface Control

1

0 0 0 0 0 0 DIVI1

(0)

DIVI0

(0)

0 0 0 RTNI4

(1)

RTNI3

(0)

RTNI2

(0)

RTNI1

(0)

RTNI0

(0)

92h Panel Interface Control

2

0 0 0 0 0 NOWI2

(0)

NOWI1

(0)

NOWI0

(0)

0 0 0 0 0 0 0 0

93h Panel Interface Control

3

0 0 0 0 0 0 VEQW11

(0)

VEQW10

(0)

0 0 0 0 0 MCPI2

(0)

MCPI1

(0)

MCPI0

(0)

95h Panel Interface Control

4

0 0 0 0 0 0 DIVE1

(0)

DIVE0

(0)

0 0 RTNE5

(0)

RTNE4

(1)

RTNE3

(1)

RTNE2

(1)

RTNE1

(1)

RTNE0

(0)

97h Panel Interface Control

5

0 0 0 0 NOWE3

(0)

NOWE2

(0)

NOWE1

(0)

NOWE0

(0)

0 0 0 0 0 0 0 0

98h Panel Interface Control

6

0 0 0 0 0 0 0 0 0 0 0 0 0 MCPE2

(0)

MCPE1

(0)

MCPE0

(0)

A4h Calibration control 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 CALB

(0)

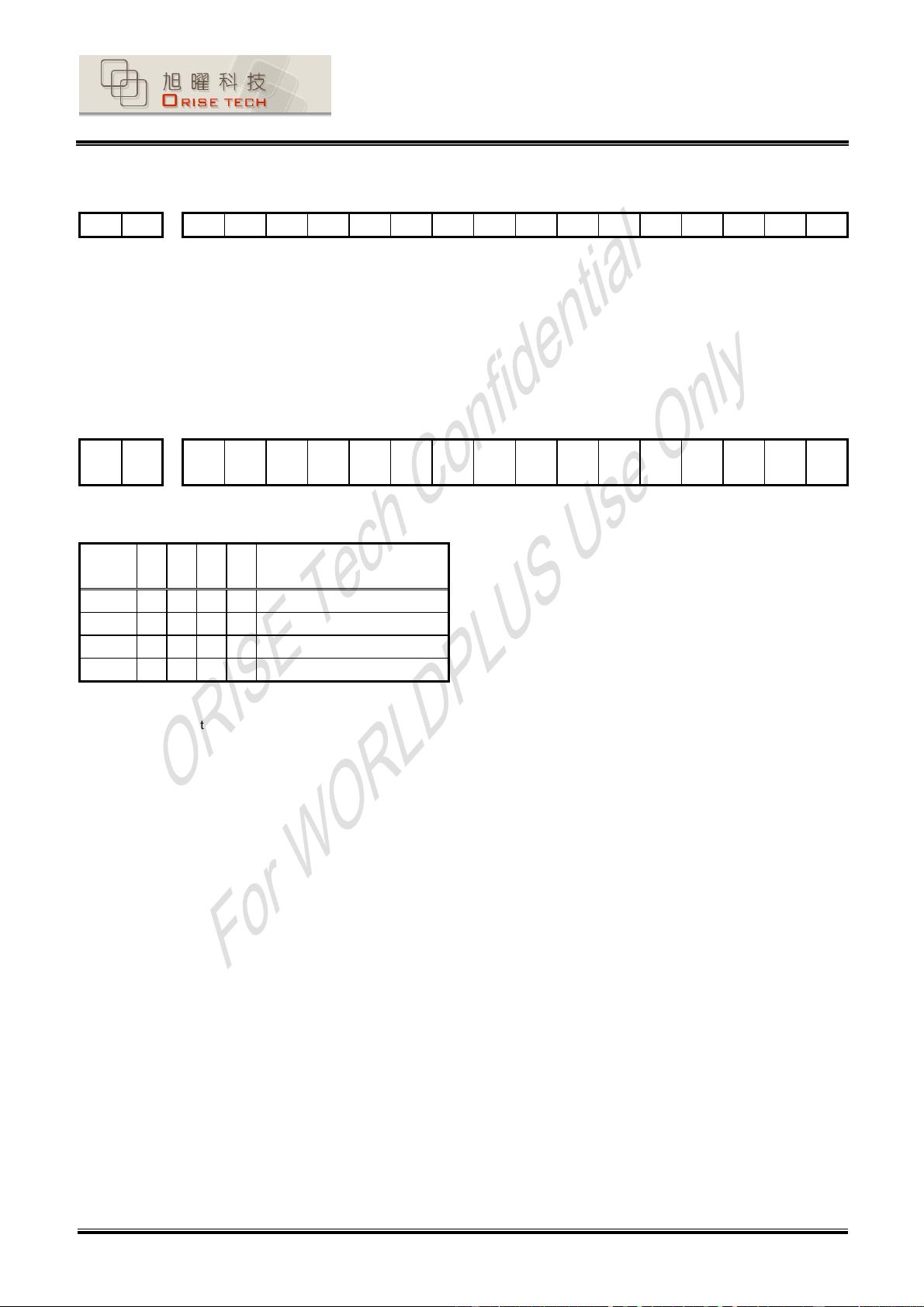

The following are detailed explanations of instructions with illustrations of instruction bits (CB15-0) assigned to each interface.

6.2.1. Index Register (IR)

R/W RS CB15 CCB1

CB13 CB12 CB11 CB10 CB9 CB8 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0

W 0

∗

∗

∗

∗

∗

∗ ∗ ∗

ID7 ID6 ID5 ID4 ID3 ID2 ID1 ID0

The index register specifies the index (R00h ~ RFFh) of a control register. The index range is from “000_0000” to “111_1111” in binary

format.

6.2.2. ID Read Register (SR)

R/W RS CB15 CB14 CB13 CB12 CB11 CB10 CB9 CB8 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0

R 0 0 1 0 1 0 1 0 0 0 0 0 0 1 0 0 0

The IC code of SPFD5408B can be accessed by read operation. ‘5408H can be read out when read ID operation is executed.

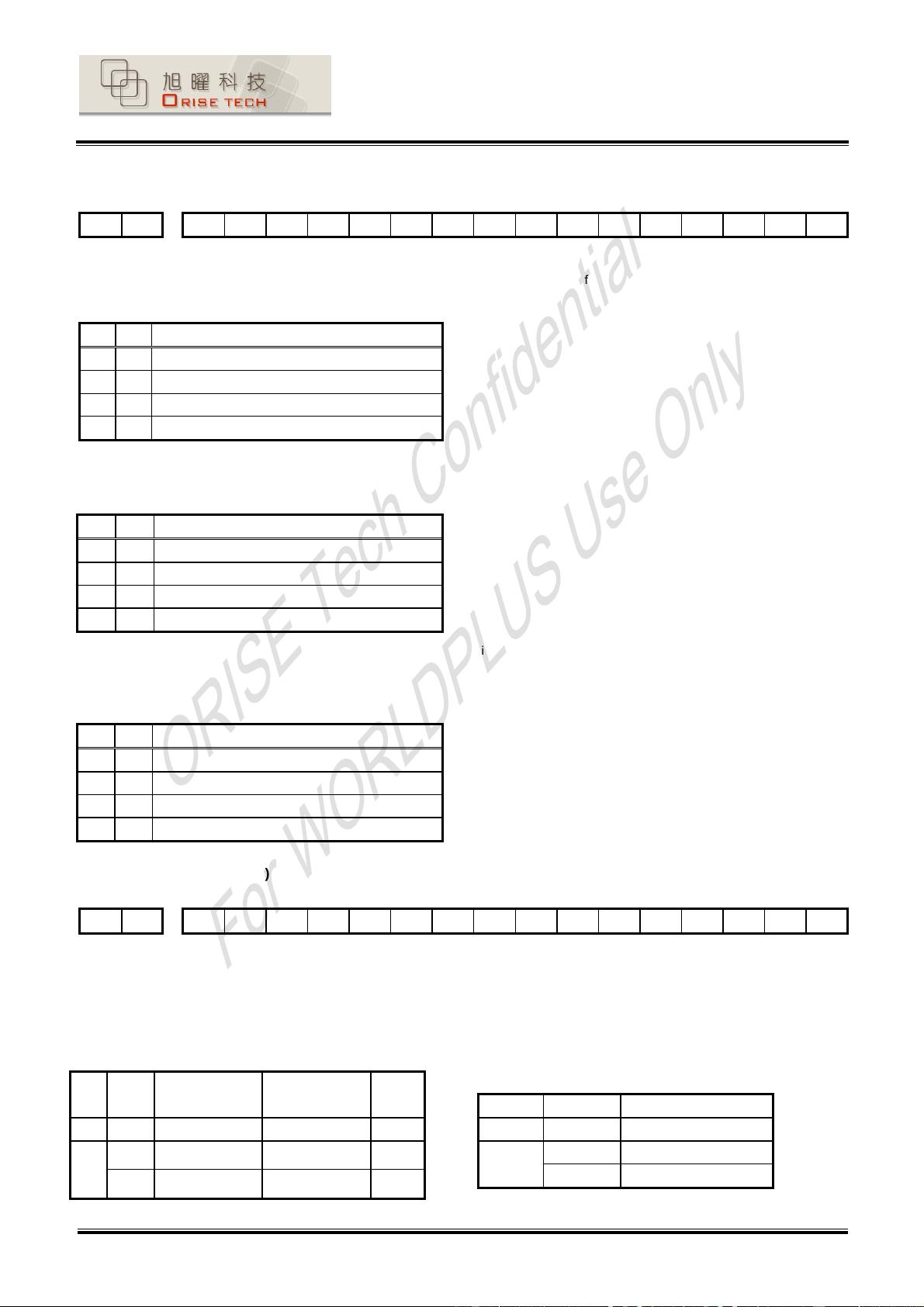

6.2.3. Driver Output Control Register (R01h)

R/W RS CB15 CB14 CB13 CB12 CB11 CB10 CB9 CB8 CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0

W 1 0 0 0 0 0 SM 0 SS 0 0 0 0 0 0 0 0

SS: Shift direction of the source driver output selection.

When SS = “0”, source driver shift from S1 to S720. When

SS = “1”, source driver shift from S720 to S1. Moreover, SS

can cooperate with BGR for different color filter

configuration of LCD panel. The combination of SS and

BGR bit are summarized at Table 6-2.

Table 6-2

SS=0;BGR=0;

S1 S2 S3 S718 S719 S720

SS=0;BGR=1; S1 S2 S3 S718 S719 S720

SS=1,BGR=0; S1 S2 S3 S718 S719 S720

SS=1,BGR=1; S1 S2 S3 S718 S719 S720

SM: Set the scan mode of the gate driver output. Moreover, SM

can cooperate with GS for different LCD panel gate line

layout. The combination of GS and SM bit are summarized at

Table 6-3.

Table 6-3

SM GS Shift Direction (begin,…..,end)

0 0 G1, G2, G3, G4…………G317, G318, G319, G320

0 1 G320, G319, G318, G317…………G4, G3, G2, G1

1 0 G1, G3, G5, …G317, G319, …G2, G4,... G318, G320

1 1 G320, G318, G316,..G4, G2, ..G319, G317,...G3, G1