8051单片机IP核设计:Synopsys工具优化实现

版权申诉

PDF格式 | 34.41MB |

更新于2024-06-15

| 47 浏览量 | 举报

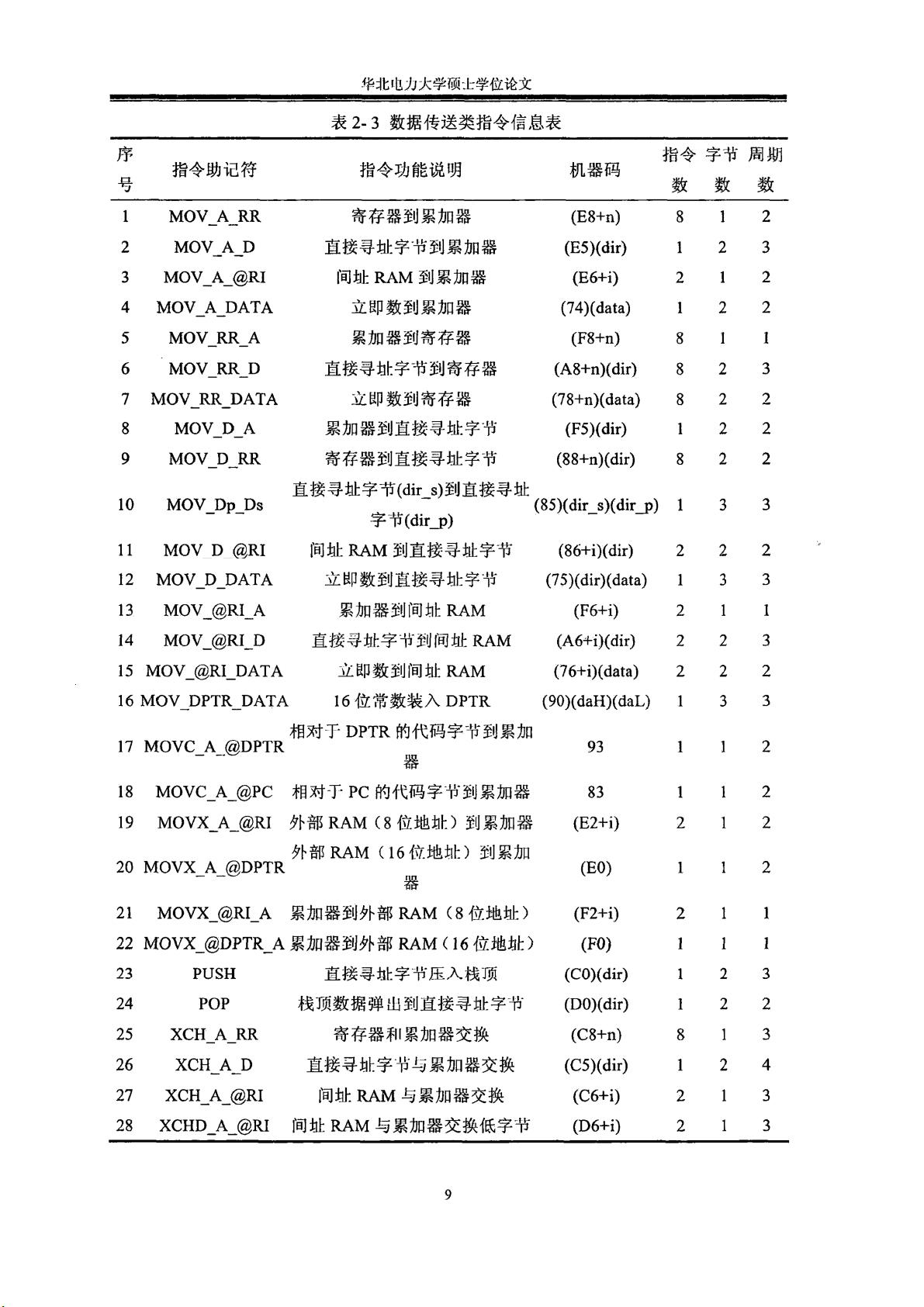

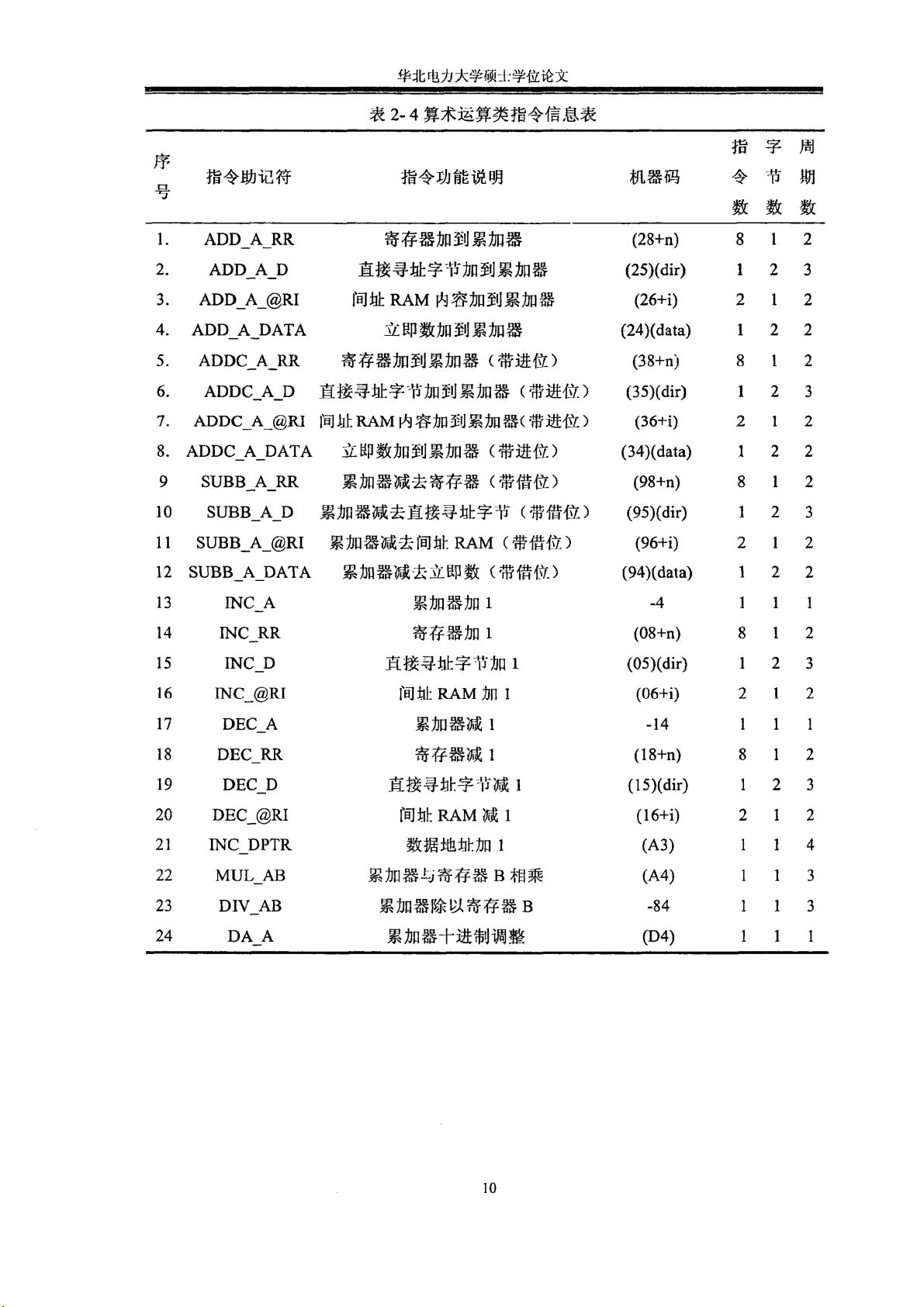

"本文详细探讨了基于Synopsys的8051单片机IP核的设计过程,旨在通过优化和复用技术,解决传统8051单片机在功能、速度和功耗上的局限性,以适应现代电子设计的需求。作者首先深入分析了经典8051单片机的特性,包括其功能、结构和指令系统,从而明确IP核的设计目标。设计的核心是优化8051指令系统,并规划出IP核的整体架构,其中包括算术逻辑运算单元、控制模块、片内数据存储器、定时器/计数器、串行端口和中断处理等关键组件。

设计过程中,作者采用了VHDL语言进行模块化和整体设计描述,确保了IP核的灵活性和可扩展性。在验证阶段,利用ModelSim测试平台进行软件仿真,对IP核的各个层面进行了详尽的测试。之后,将设计导入到Quartus II环境中,结合FPGA进行硬件测试,以验证其实现效果。最后,通过Synopsys的Design Compiler工具进行综合优化,以满足严格的时序和面积约束,提高IP核的性能和效率。

经过一系列测试,设计出的8051单片机IP核不仅与标准MCS-51系列保持指令兼容,而且在功能、存储容量和性能上都有显著提升,特别是提高了最高时钟频率和指令执行效率。因此,该设计具有很高的实用价值,为8位微控制器的低端应用提供了新的解决方案。

关键词:51单片机,IP核,ModelSim,FPGA,Synopsys,综合优化"

本文研究的重点在于如何利用现代设计方法和工具,如VHDL、ModelSim、Quartus II和Synopsys Design Compiler,来优化和实现8051单片机的IP核。这种基于IP复用的设计策略降低了开发成本,缩短了设计周期,同时也提升了设计的性能。通过在FPGA上进行硬件验证,可以快速迭代和调试,确保了IP核的正确性和可靠性。此外,Synopsys的Design Compiler工具在综合优化方面发挥了关键作用,确保了设计在满足功能要求的同时,达到最佳的性能和面积效率。这为8位微控制器在各种应用场景中的持续使用提供了新的可能,尤其是在对成本敏感和性能要求不断提升的市场中。

相关推荐

电气_空空

- 粉丝: 5341

最新资源

- Ruby语言集成Mandrill API的gem开发

- 开源嵌入式qt软键盘SYSZUXpinyin可移植源代码

- Kinect2.0实现高清面部特征精确对齐技术

- React与GitHub Jobs API整合的就业搜索应用

- MATLAB傅里叶变换函数应用实例分析

- 探索鼠标悬停特效的实现与应用

- 工行捷德U盾64位驱动程序安装指南

- Apache与Tomcat整合集群配置教程

- 成为JavaScript英雄:掌握be-the-hero-master技巧

- 深入实践Java编程珠玑:第13章源代码解析

- Proficy Maintenance Gateway软件:实时维护策略助力业务变革

- HTML5图片上传与编辑控件的实现

- RTDS环境下电网STATCOM模型的应用与分析

- 掌握Matlab下偏微分方程的有限元方法解析

- Aop原理与示例程序解读

- projete大语言项目登陆页面设计与实现