优化优化FPGA的功耗:的功耗:ISE设计工具设计工具

Xilinx(赛灵思)是全球领先的可编程逻辑完整解决方案的供应商。Xilinx研发、制造并销售范围广泛的高级集成

电路、软件设计工具以及作为预定义系统级功能的IP(Intellectual Property)核。客户使用Xilinx及其合作伙伴

的自动化软件工具和IP核对器件进行编程,从而完成特定的逻辑操作。Xilinx公司成立于 1984年,Xilinx首创了

现场可编程逻辑阵列(FPGA)这一创新性的技术,并于1985年首次推出商业化产品。目前Xilinx满足了全世界

对FPGA产品一半以上的需求。 自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积

效率,缩小了FP

Xilinx(赛灵思)是全球领先的可编程逻辑完整解决方案的供应商。Xilinx研发、制造并销售范围广泛的高级集成电路、软

件设计工具以及作为预定义系统级功能的IP(Intellectual Property)核。客户使用Xilinx及其合作伙伴的自动化软件工具和IP

核对器件进行编程,从而完成特定的逻辑操作。Xilinx公司成立于 1984年,Xilinx首创了现场可编程逻辑阵列(FPGA)这一创

新性的技术,并于1985年首次推出商业化产品。目前Xilinx满足了全世界对FPGA产品一半以上的需求。

自从Xilinx推出FPGA二十多年来,研发工作大大提高了FPGA的速度和面积效率,缩小了FPGA与ASIC(Application

Specific Integrated Circuit的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路)之间的差距,使FPGA成

为实现数字电路的优选平台。现如今FPGA在各种电路设计中广泛应用,如何对FPGA系统进行低功耗优化成为一个重要的现

实问题。从最早的FPGA功耗模型的建,到较完善的FPGA功耗估算模型,再到现在功耗估算工具的出现,FPGA设计时对功

耗的预估已经越来越准确,节约功耗的方法也越来越多样降低 FPGA 功耗是缩减封装和散热成本、提高器件可靠性以及打开

移动电子设备等新兴市场之门的关键。Xilinx在提供低功耗 FPGA 解决方案方面一马当先。本文说明如何应用计算机辅助设计

(CAD,CAD-Computer Aided Design)利用计算机及其图形设备帮助设计人员进行设计工作) 技术,如 Xilinx? ISE? 9.2i 软

件中采纳的技术,来有效降低功耗。

ISE是使用XILINX的FPGA的必备的设计工具,它可以完成FPGA开发的全部流程,包括设计输入、仿真、综合、布局布

线、生成BIT文件、配置以及在线调试等,功能非常强大。ISE除了我们功能完整,使用方便外,它的设计性能也非常好,拿

ISE 9.x来说,其设计性能比其他解决方案平均快30%,它集成的时序收敛流程整合了增强性物理综合优化,提供最佳的时钟

布局、更好的封装和时序收敛映射,从而获得更高的设计性能。先进的综合和实现算法将动态功耗降低了10%。

CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体,电压控制的一种放大器件。是组成

CMOS数字集成电路的基本单元) 电路中的功耗由静态(漏电)功耗和动态功耗两部分组成。静态功耗主要由晶体管的泄漏

电流和FPGA偏置电流引起,它与工艺技术、晶体管特性、晶体管个数、采用的绝缘介质等因素有关,这些是由FPGA本身决

定的,与电路活动无关。晶体管的泄漏电流主要由三部分组成:亚阈值漏电流、栅极漏电流和源漏极反偏漏电流动态功耗是指

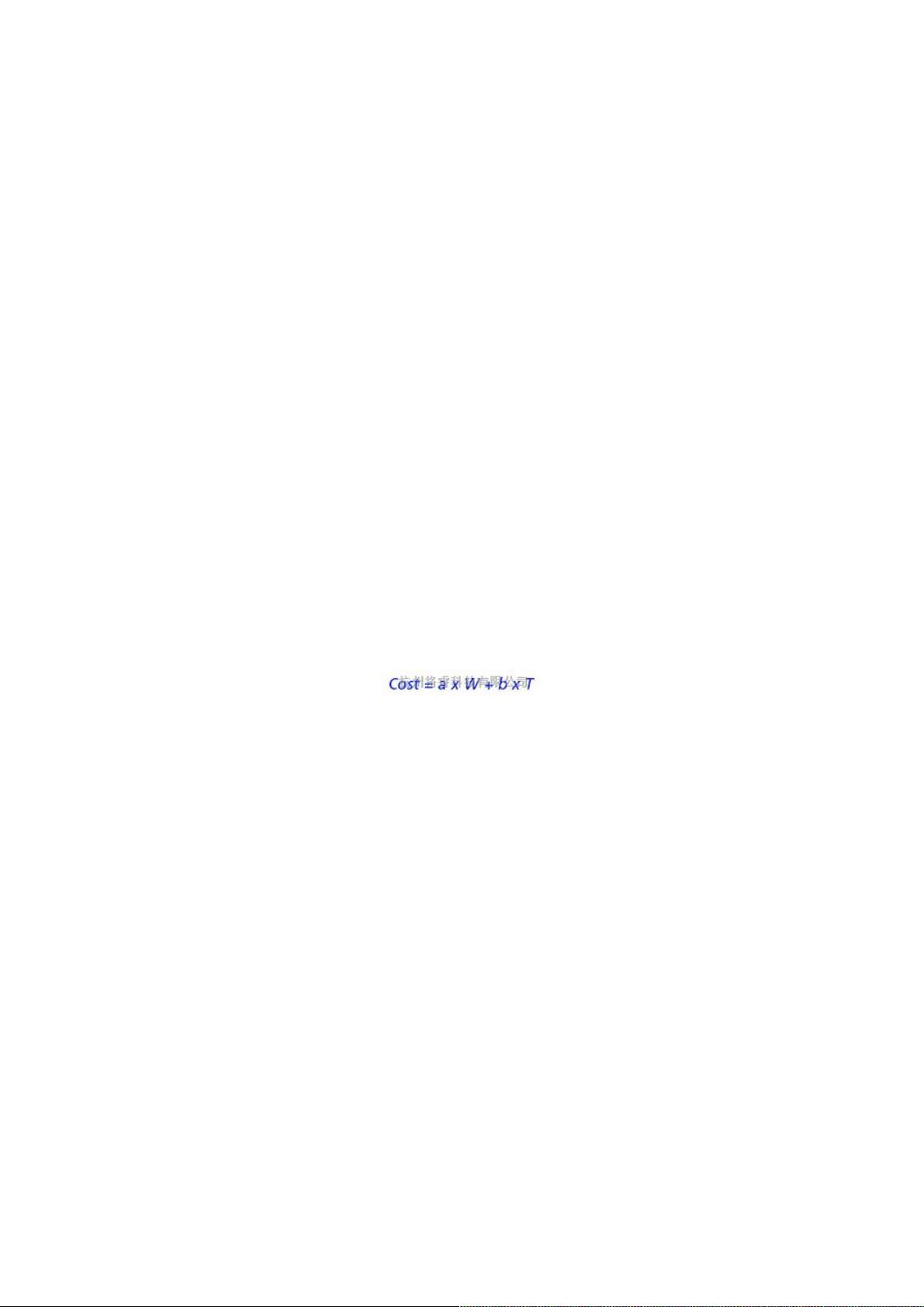

电容充放电功耗和短路功耗,是由电路的翻转造成的,符合以下公式:

其中,Ci 表示信号 i 的电容;fi 称为“开关活动率”,表示信号 i 上的跃迁速率;V 是电源电压。

静态功耗是指漏电流功耗,是电路状态稳定时的功耗,其数量级很小,主要是亚阈值漏电流和栅极氧化层漏电流。截止

MOS 晶体管属不完全绝缘体,允许其漏极与源极之间有亚阀值漏电流。栅极氧化层漏电流是由通过晶体管栅极流向其管体、

漏极和源极的隧道电流所致。

工艺尺寸缩小(如近期采纳 65 纳米工艺的趋势)意味着更低的电源电压和更小的晶体管尺寸,致使导线长度缩短、电容

量减小以及总体动态功耗降低。较小的工艺几何尺寸还意味着较短的晶体管沟道和较薄的栅极氧化层,致使静态功耗随着工艺

尺寸缩小而增加。

FPGA工作原理工作原理

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic

Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可

编程器件。与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构,FPGA利用小型查找表

(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构

成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模

块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以

及个模块之间或模块与I/O间的连接方式,并最终决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最

终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

FPGA中的功耗中的功耗

对于实现给定的逻辑电路而言,FPGA的可编程性和灵活性使其功耗效率比定制ASIC要低。目前,在集成电路界ASIC被

认为是一种为专门目的而设计的集成电路。是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。ASIC的特

点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密

性增强、成本降低等优点。FPGA的配置电路和配置存储器占用硅片面积,致使导线延长和互连电容增加。在FPGA中,预制

金属导线段上附加的可编程布线开关产生互连,从而加重了信号产生的电容性负载。

虽然静态电流与动态电流相比可以忽略不计,然而对电池供电的手持设备就显得十分重要,在设备通电而不工作时更是如

此。静态电流的因素众多,包括处于没有完全关断或接通的状态下的I/O以及内部晶体管的工作电流、内部连线的电阻、输入

与三态电驱动器的上拉或下拉电阻。在易失性技术中,保持编程信息也需一定的静态功率。抗熔断是一种非易失性技术,因此