掌握MSI组合电路:第3章 加法器、编码器与数值比较器详解

版权申诉

9 浏览量

更新于2024-07-03

收藏 1.42MB PPT 举报

本课件主要围绕第3章的内容,探讨了数字电路中的常用组合逻辑电路及其在中规模集成电路(MSI)应用中的实践。章节的核心知识点包括加法器、编码器、译码器、数据选择器和数据分配器等基本逻辑电路的逻辑功能、工作原理和设计方法。

加法器是计算两个或多个输入数值之和的逻辑电路,它们根据不同的设计,可以执行二进制、十进制或其他进制的加法。这部分内容会介绍不同进制加法器的实现,如全加器、半加器以及多位加法器的结构和逻辑表达式。

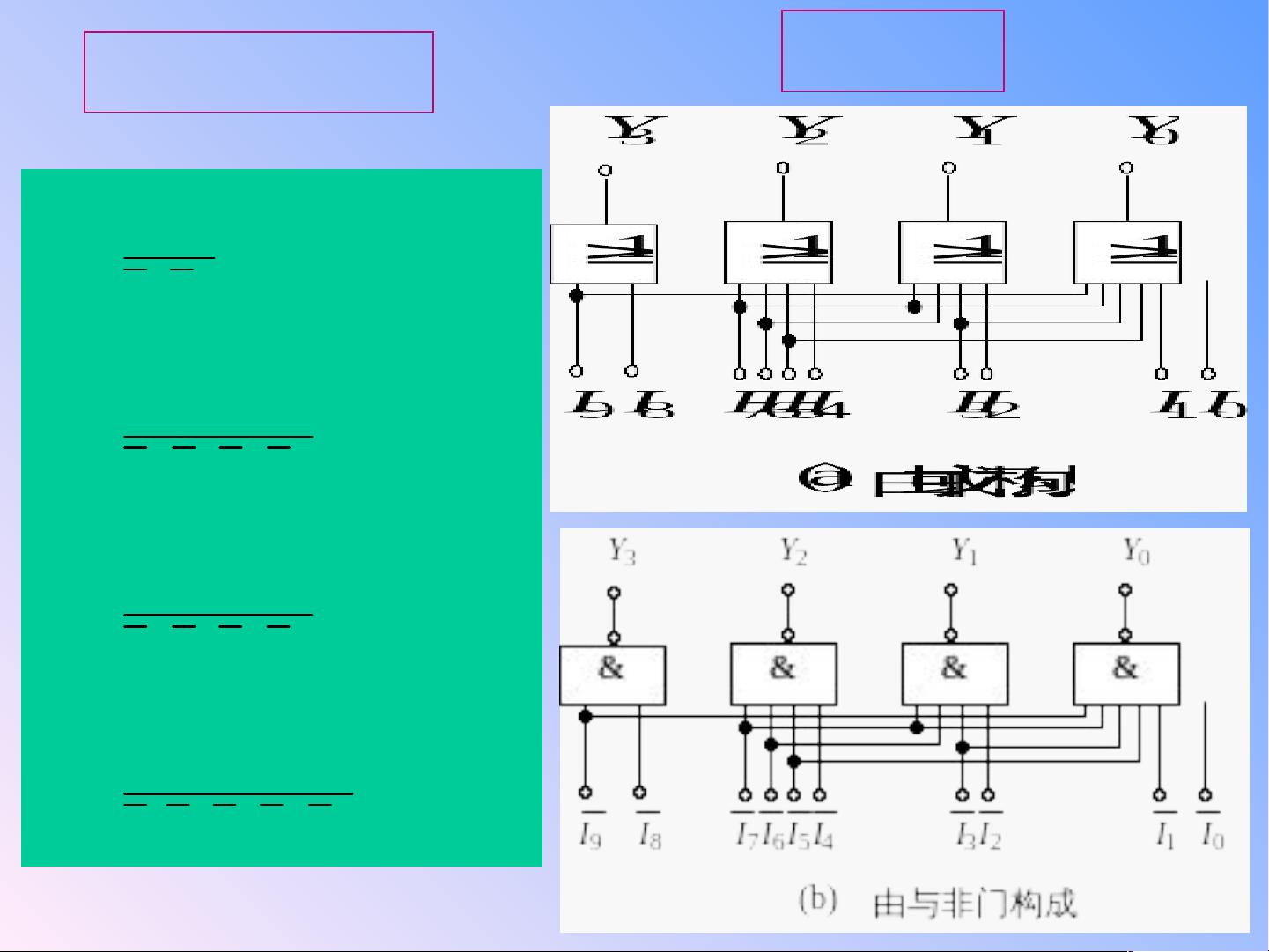

编码器是一种将原始信号转换成固定长度的二进制或十进制代码的电路。3位二进制编码器示例中,通过或门或与非门构建,可以将8个互斥输入映射到3位二进制输出,展示了一种基本的编码过程。此外,还有3位二进制优先编码器,它强调信号之间的优先级关系,高优先级信号可以排斥低优先级信号。

编码器有多种类型,例如二进制编码器用于将单个输入信号转换成二进制代码,而十进制编码器则处理十进制数字的编码。这些编码器不仅涉及基本逻辑电路的设计,还可能涉及到编码规则和优先级策略。

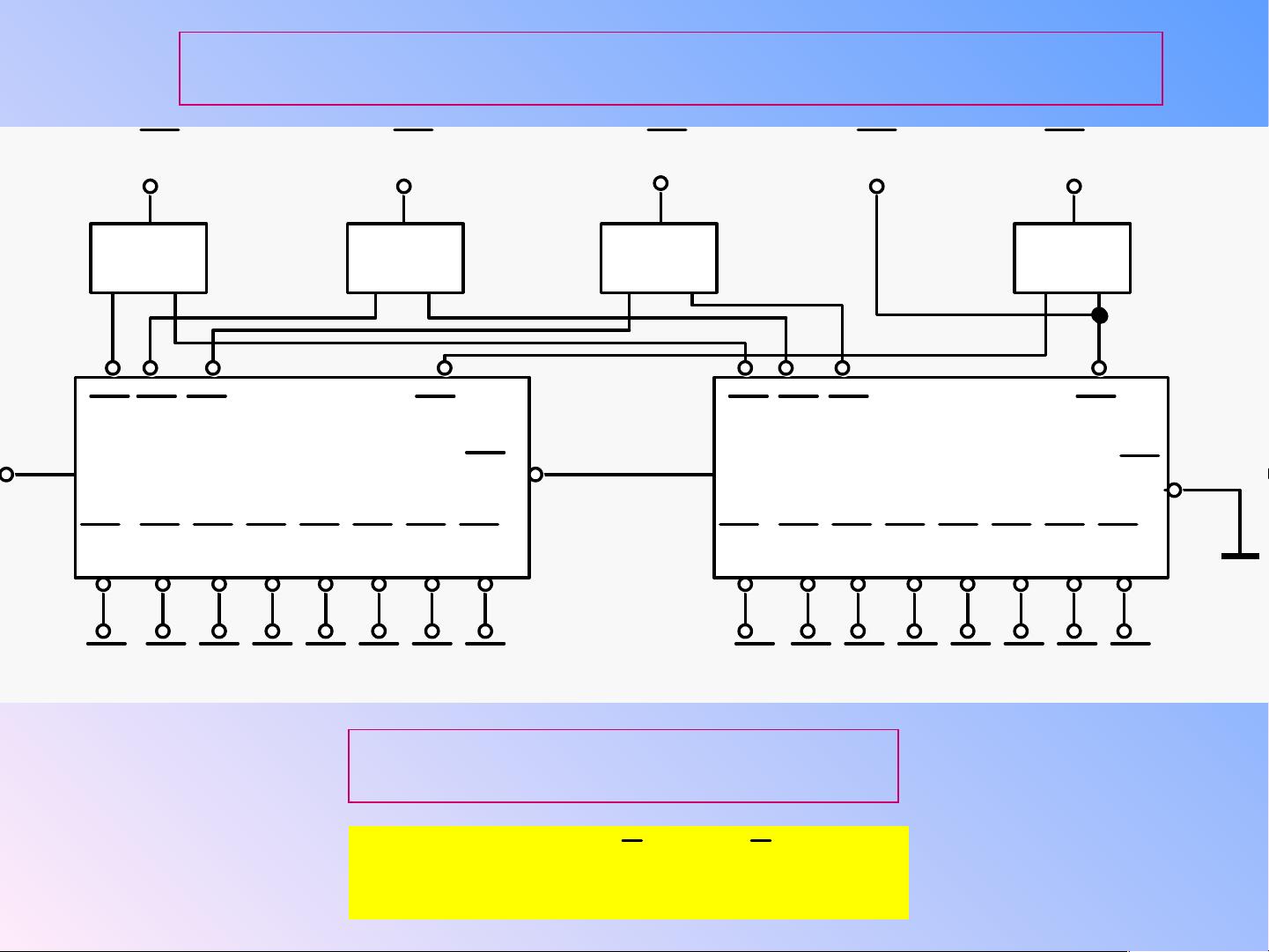

译码器则是将编码后的信号解码回原始形式,常用于数据通信和存储器系统。数据选择器则可以根据输入的选择信号,从多个输入中选择一个输出,数据分配器则负责将数据分配到多个输出端。这些电路都是组合逻辑设计的重要组成部分,它们在计算机硬件和数字系统中发挥着关键作用。

在课程中,学生们将学习如何利用MSI(中规模集成电路)来设计和构建这些组合逻辑电路,理解其在实际应用中的效率和局限性。通过理论学习和实践操作,学生可以掌握组合逻辑电路设计的基本技能,并能够将其应用到实际项目中。

本课件的学习目标旨在提升学生的数字逻辑设计能力,让他们理解并掌握组合逻辑电路的核心原理,从而在电子工程、计算机科学和其他相关领域中有坚实的基础。通过深入研究这些电路,学生能够构建和优化复杂的数据处理系统,推动技术进步。

153 浏览量

155 浏览量

2021-09-21 上传

点击了解资源详情

点击了解资源详情

2025-01-05 上传

2025-01-05 上传

2025-01-05 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- lingo基础教程 快速入门

- asp.net xml教程

- keil uvision3与PROTEUS7软件连接的完美教程

- MCS-51单片机温度控制系统

- Qt Designer And Kdevelop-3.0 For Beginners.pdf

- C语言嵌入式系统编程修炼之道.pdf

- JAVA2核心技术第1卷:基础知识7th.pdf

- 电路第五版,邱关源,第五版课件

- 3G基础知识讲座,3G知识入门讲座

- javascript常用100语句

- 08年程序员考试下午试题

- maple的基础教程

- 更新至08年的程序员试题

- SCO5.0.7安装说明

- Win2003下iis+php+mysql+zend架设

- 关于开发工具Ant, JBuilder, Eclipse, workshop等使用的FAQ以及资源