10 bit 200 MS/s 分段电流舵DAC设计与优化

35 浏览量

更新于2024-09-01

2

收藏 377KB PDF 举报

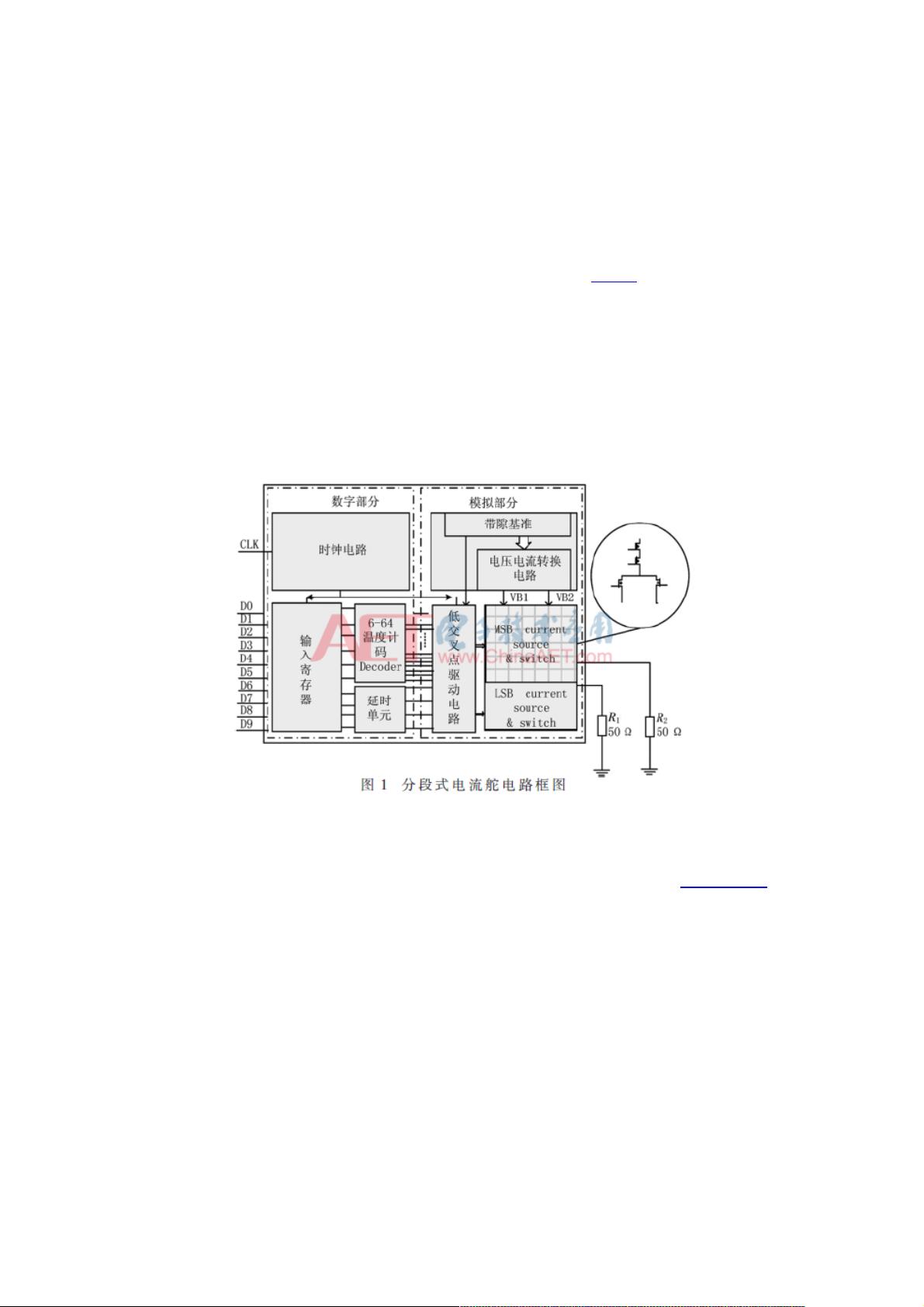

"该文介绍了一种10 bit 200 MS/s的分段式电流舵DAC设计,采用TSMC 0.18 μm CMOS工艺,旨在优化高速数字模拟转换器的性能。设计中,电流舵结构与分段技术结合,6位采用温度计编码,4位采用二进制编码。电流源开关单元利用cascode结构和差分输出以提升性能。低交叉点开关驱动电路进一步增强动态特性。在1.8 V电源下,DAC的DNL和INL最大误差分别为0.05 LSB和0.2 LSB,SFDR达到81.53 dB。这种DAC适用于高速通信系统的应用,如LTE通信。"

本文探讨的关键知识点包括:

1. **电流舵数模转换器(DAC)**:电流舵DAC是一种高速、宽带、对寄生参数不敏感的转换器类型,适合于高频率通信应用。其工作原理是通过控制电流源的开关状态来实现数字信号到模拟信号的转换。

2. **分段式结构**:这种结构结合了二进制码和温度计码的优点,高分辨率和紧凑的电路布局。在设计中,10位DAC分为6位温度计编码和4位二进制编码,以平衡精度和电路复杂度。

3. **TSMC 0.18 μm CMOS工艺**:这是一种广泛应用的半导体制造工艺,提供高集成度和低功耗,适合于高性能、小型化的集成电路设计。

4. **Cascode结构**:在电流源开关单元中采用,能够提高输出阻抗和电源抑制比,降低电源波动对电路性能的影响。

5. **差分输出**:这种结构可以减小共模干扰,提高信号质量,增加信噪比。

6. **低交叉点开关驱动电路**:用于提升DAC的动态性能,减少转换过程中的失真和噪声。

7. **微分非线性误差(DNL)**和**积分非线性误差(INL)**:衡量DAC线性度的重要指标,较小的DNL和INL意味着更好的转换精度。在本设计中,DNL和INL的最大误差分别小于0.05 LSB和0.2 LSB。

8. **无杂动态范围(SFDR)**:衡量DAC输出信号的信噪比,高SFDR表示在指定频率下的输出信号纯净度高。文中提到的81.53 dB SFDR表明在0.976 MHz输出频率时,DAC具有良好的动态性能。

9. **带隙基准电路**:为确保电流源的精度,设计中包含此电路,它提供一个与温度相关的较小的电压参考,从而稳定电流输出。

10. **应用领域**:设计的10 bit 200 MS/s DAC适用于数字视频处理、音频信号处理和现代通信系统,特别是LTE通信系统,满足高速率和高精度的需求。

该设计通过优化电路结构和采用先进的工艺技术,实现了高采样率和高精度的电流舵DAC,为高速通信系统提供了有效的解决方案。

103 浏览量

150 浏览量

192 浏览量

265 浏览量

179 浏览量

149 浏览量

2021-02-21 上传

136 浏览量

194 浏览量

weixin_38611877

- 粉丝: 5

- 资源: 925

最新资源

- 3-en-raya-1era-parte-:连续3项任务San Pablo

- matlab代码sqrt-coa:用C++编写的布谷鸟优化算法(COA)

- zitiwenjian.rar

- 飞行员:我在硕士论文中创建了一个简单的项目。 它旨在显示用于移动应用程序开发的最流行的跨平台框架的异同。 还包括本机解决方案

- 兰大2018届计算机组成课程PPT

- Dollar:可在heroku中使用的单独的类似FB的应用程序,因为它已在烧瓶上完全堆满并起React

- junfai,matlab中rand的源码,matlab源码之家

- 食品饮料制造业解决方案.rar

- ElectricWow.9o51twf5ei.gahQfEe

- androidtest:android pritace

- react-native-toolbox:一组脚本来简化React Native开发

- 现代hy308手写板驱动 v9.8 官方版

- tns-template-vue:具有TypeScript,PostCSS,Tailwind,Vuex,Vue Router,Webpack等的NativeScript Vue模板

- 算折射率-计算算折射率的一款实用软件包括NK值

- 光线追踪:Projet d'imagerienumérique

- patrick-fulghum.github.io