UVM入门指南:快速掌握与实践

需积分: 46 105 浏览量

更新于2024-07-18

1

收藏 1.03MB PDF 举报

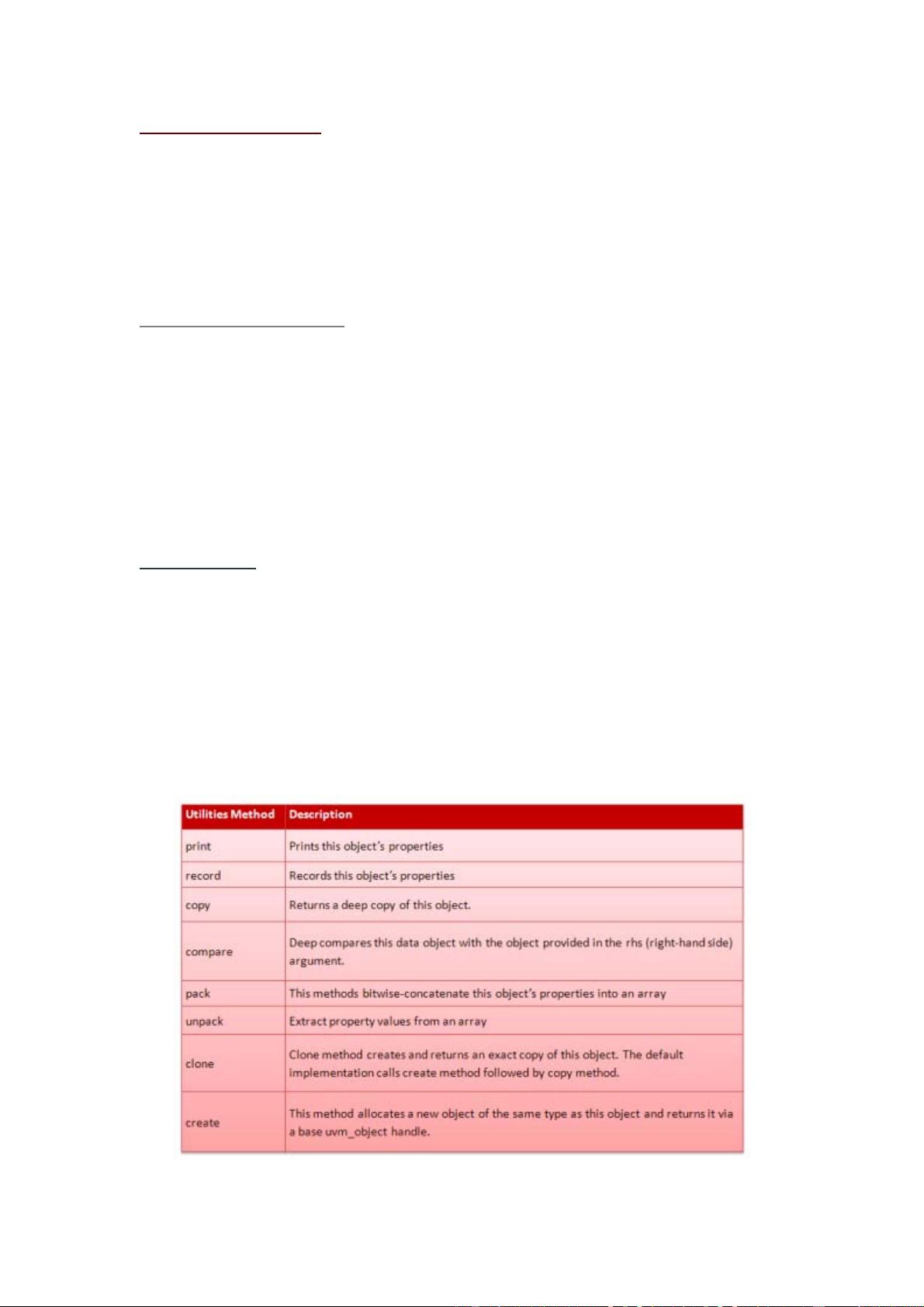

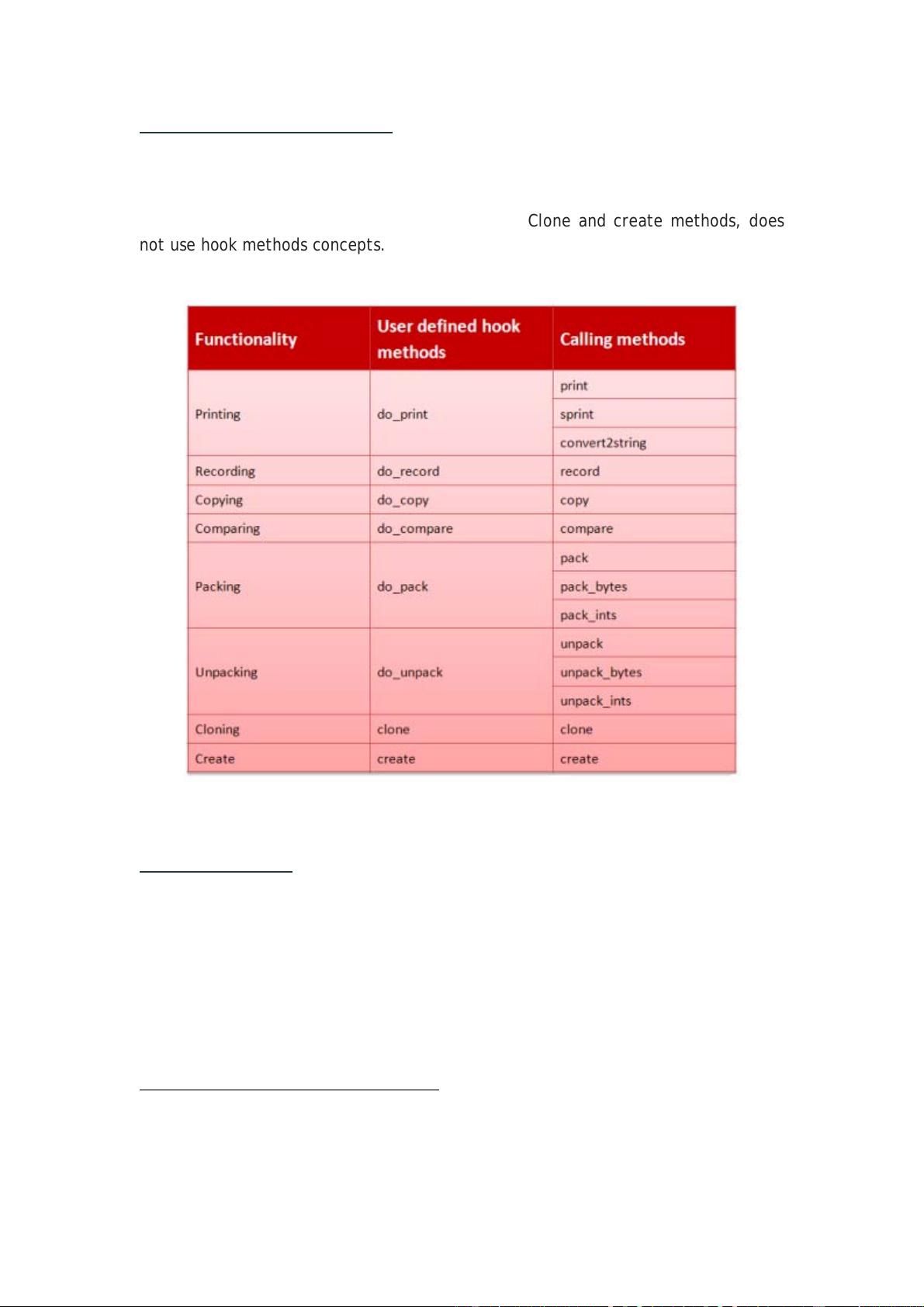

本教程是针对UVM(Universal Verification Methodology)的快速入门指南,适合那些希望了解和掌握这个广泛应用于电子设计验证的工具的新手。UVM是一种高级测试方法论,旨在提高测试效率和一致性,特别是在SoC (System-on-Chip) 设计中的验证流程。

1. **安装UVM库**:首先,你需要了解如何安装UVM库,这通常涉及到在设计环境中集成UVM框架,如在Vivado或Synopsys等EDA工具中设置适当的路径和依赖。

2. **UVM测试环境(Uvm_env)**:UVM测试环境是所有测试活动的基础,它定义了测试运行的上下文。Uvm_env提供了初始化、清理和配置测试环境的基本功能。

3. **验证组件(VerificationComponents)**:UVM将组件划分为三种类型 - UVM component、sequencer和driver,它们分别是被测模块、事件顺序控制器和数据驱动器,各自负责不同的验证职责。

4. **Uvm_componentClass**:这是一种基础类,所有的自定义组件都应继承于此。它定义了组件的生命周期方法,如`build`、`connect_phase`和`end_of_elaboration`。

5. **Uvm_test**:这是测试集的核心,它包含一组测试案例,每个案例由一个或多个测试项组成。测试项可以是简单的函数调用,也可以是更复杂的sequence执行。

6. **TopModule**:作为设计中的顶层模块,它负责配置和启动测试,同时管理测试环境和各个验证组件之间的交互。

7. **UVM报告与配置**:UVM提供了丰富的报告机制,包括`set_report`、`get_report`等方法,以及`set_config`和`get_config`用于设置和获取配置参数。自动配置和手动配置是配置过程的两种方式。

8. **UVM序列(UVMSEQUENCE)**:这部分详细介绍了如何编写和使用UVM序列,包括基础概念、通信机制(例如sequence和driver的交互)、不同类型的序列(简单例程、分段的do-do-do宏等),以及优先级设置、同步和互斥访问控制。

9. **TLM(Transaction-Level Modeling)**:UVM TLM专注于基于端口的数据交换,通过`put`和`get`操作实现模型间的通信。这包括数据传输模式如port-based和memory-mapped接口的处理。

10. **工厂(UVMFactory)**:UVMFactory负责组件实例化和注册,确保组件在整个系统中的正确构造和管理。你可以学习如何覆盖工厂默认行为,以及如何使用工厂进行动态配置。

总结来说,本教程提供了一个全面的UVM学习路径,从安装到高级用法,包括组件类、测试结构、报告、序列和数据传输模型,帮助读者建立起对UVM的理解,并能在实际项目中有效地应用。无论是初学者还是有一定经验的工程师,都能从中找到有价值的内容。

2019-08-25 上传

2012-07-10 上传

2022-01-18 上传

2021-08-10 上传

2020-07-13 上传

155 浏览量

2022-09-20 上传

weixin_43621691

- 粉丝: 0

- 资源: 2

最新资源

- Oracle Form觸發器、系統變量精解2

- Oracle Form屬性、內置子程序、觸發器、系統變量精解

- SMSCOM开发手册

- PIC C语言编程实例

- ubuntu命令参考卡片

- How to Write Program in Visual C++

- SVN权限控制全面解析

- apache+svn+MySQL+PHP+svnmanager+bugfree完全安装手册

- Thinking In Java 第三版目录版中文版PDF

- SNMP-简单网络管理协议(PDF)

- 10720路由器信息

- Apache+SVN+Trac配置详解

- 硬盘数据恢复教程 PDF格式

- 软件工程详细设计说明书

- JSON教程.pdf

- wince中文版(部分章节)