Local

CLOCK

I1

--.)

I1

--.)

I2

-

-D

01

I2

+

02

I1

-

I2-

-h

I1

+’

I2

.--)

-

I1

-

II

k

I

+

+

w

I

r

s2

17

PhaSe-1

Phase-27

Dynamic

static

Latches

Latches

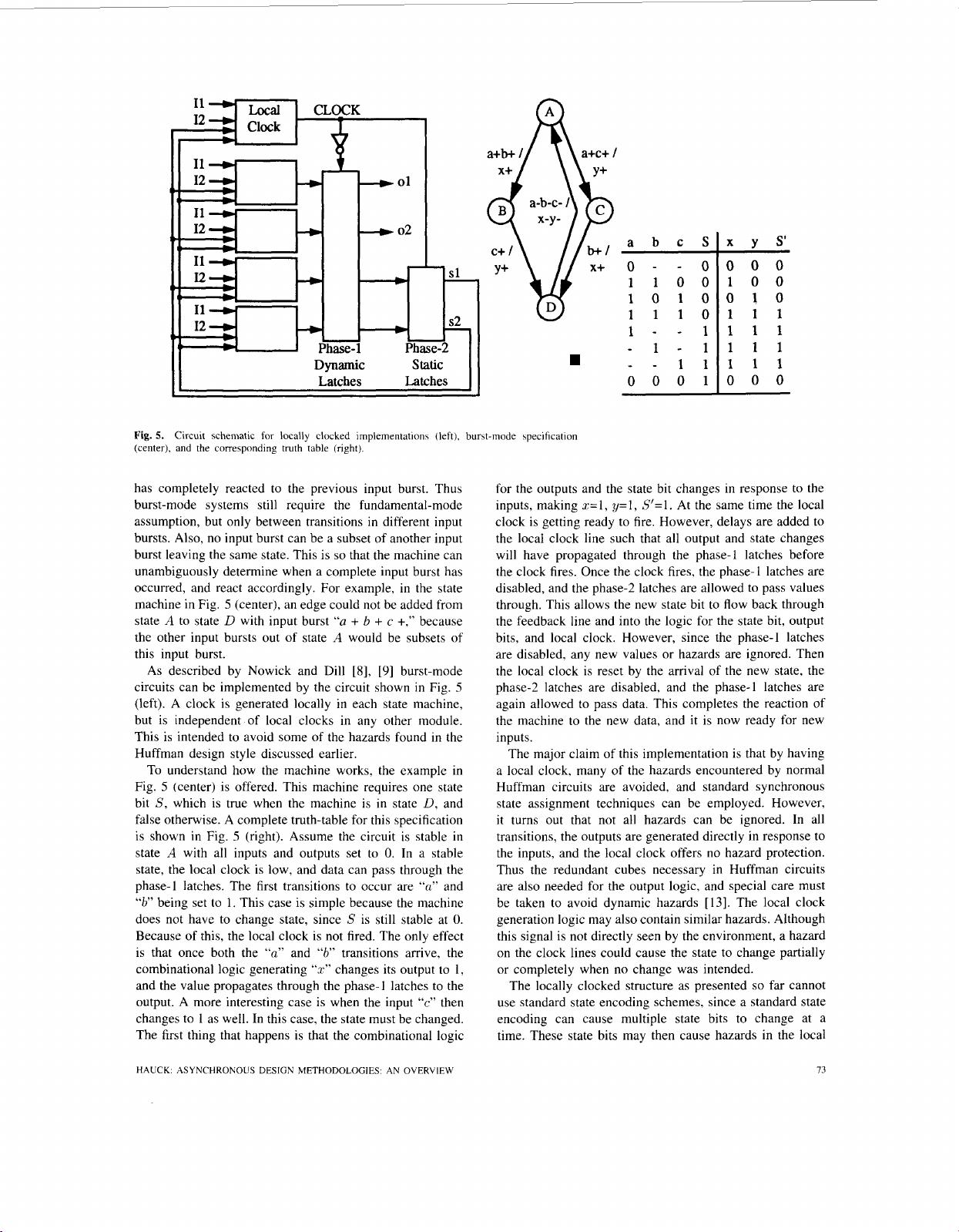

Fig.

5.

Circuit schematic

for

locally

clocked implementations (left), burst-mode specification

(center),

and

the corresponding truth table (right).

has completely reacted to the previous input burst. Thus

burst-mode systems still require the fundamental-mode

assumption, but only between transitions in different input

bursts. Also, no input burst can be

a

subset of another input

burst leaving the same state. This is

so

that the machine can

unambiguously determine when

a

complete input burst has

occurred, and react accordingly. For example, in the state

machine in Fig.

5

(center), an edge could not be added from

state

A

to state

D

with input burst

“a

+

b

+

c

+,”

because

the other input bursts out of state

A

would be subsets of

this input burst.

As described by Nowick and Dill

[8],

[9]

burst-mode

circuits can be implemented by the circuit shown in Fig.

5

(left).

A

clock is generated locally in each state machine,

but is independent of local clocks in any other module.

This is intended to avoid some of the hazards found in the

Huffman design style discussed earlier.

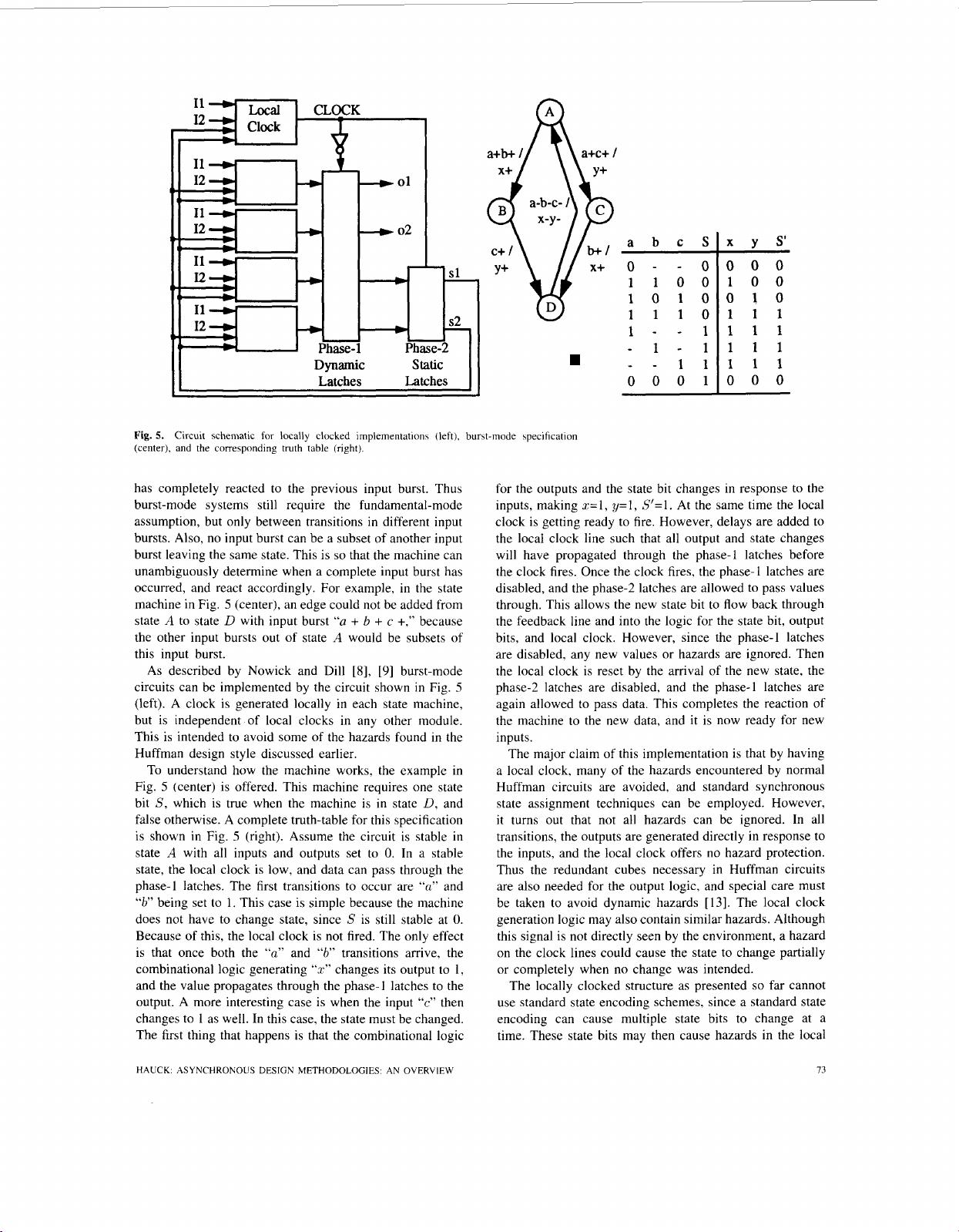

To understand how the machine works, the example in

Fig.

5

(center) is offered. This machine requires one state

bit

S,

which is true when the machine is in state

D,

and

false otherwise. A complete truth-table for this specification

is shown

in

Fig.

5

(right). Assume the circuit is stable in

state

A

with all inputs and outputs set to

0.

In a stable

state, the local clock is low, and data can pass through the

phase-1 latches. The first transitions to occur are

“a”

and

“b”

being set to

1.

This case is simple because the machine

does not have to change state, since

S

is still stable at

0.

Because of this, the local clock is not fired. The only effect

is that once both the

“a”

and

“b”

transitions arrive, the

combinational logic generating

“z”

changes its output to

1,

and the value propagates through the phase-1 latches to the

output.

A

more interesting case is when the input

“c”

then

changes to

1

as

well. In this case, the state must be changed.

The first thing that happens is that the combinational logic

abcS

~ ~~

0--0

1100

1010

1110

1--1

-1-1

--

11

0001

for the outputs and the state bit changes in response to the

inputs, making

x=

1,

y=l

,

S’=l

.

At the same time the local

clock is getting ready to fire. However, delays are added to

the local clock line such that

all

output and state changes

will have propagated through the phase-

1

latches before

the clock fires. Once the clock fires, the phase-

1

latches are

disabled, and the phase-2 latches are allowed to pass values

through. This allows the new state bit to flow back through

the feedback line and into the logic for the state bit, output

bits, and local clock. However, since the phase-1 latches

are disabled, any new values or hazards are ignored. Then

the local clock is reset by the arrival of the new state, the

phase-2 latches are disabled, and the phase-I latches are

again allowed to pass data. This completes the reaction of

the machine to the new data, and it is now ready for new

inputs.

The major claim of this implementation is that by having

a

local clock, many of the hazards encountered by normal

Huffman circuits are avoided, and standard synchronous

state assignment techniques can be employed. However,

it

turns out that not

all

hazards can be ignored. In all

transitions, the outputs are generated directly in response to

the inputs, and the local clock offers no hazard protection.

Thus the redundant cubes necessary in Huffman circuits

are also needed for the output logic, and special care must

be taken to avoid dynamic hazards

[

131. The local clock

generation logic may also contain similar hazards. Although

this signal is not directly seen by the environment,

a

hazard

on the clock lines could cause the state to change partially

or completely when no change was intended.

The locally clocked structure

as

presented

so

far cannot

use standard state encoding schemes, since

a

standard state

encoding can cause multiple state bits to change at

a

time. These state bits may then cause hazards in the local

HAUCK: ASYNCHRONOUS DESIGN METHODOLOGIES: AN OVERVIEW

I3

Authorized licensed use limited to: XILINX. Downloaded on October 8, 2009 at 03:39 from IEEE Xplore. Restrictions apply.