使用EDA技术实现的HDB3编码器设计

93 浏览量

更新于2024-08-29

收藏 391KB PDF 举报

"基于EDA技术的HDB3编码器的设计与实现"

在数字通信系统中,HDB3编码是一种关键的技术,用于基带传输,具有显著的优势。HDB3码(High Density Bipolar Code with three consecutive zeros,三阶高密度双极性码)被国际电信联盟(ITU)推荐,因为它没有直流分量,这可以防止信号在长距离传输时衰减。此外,HDB3码还具备强大的检错能力,能够通过检测码字中的极性交替变化来发现并可能纠正错误,这对于保持数据完整性至关重要。与非归零码(NRZ)相比,HDB3码还具有时钟恢复性能,这对于同步数据传输非常有利。

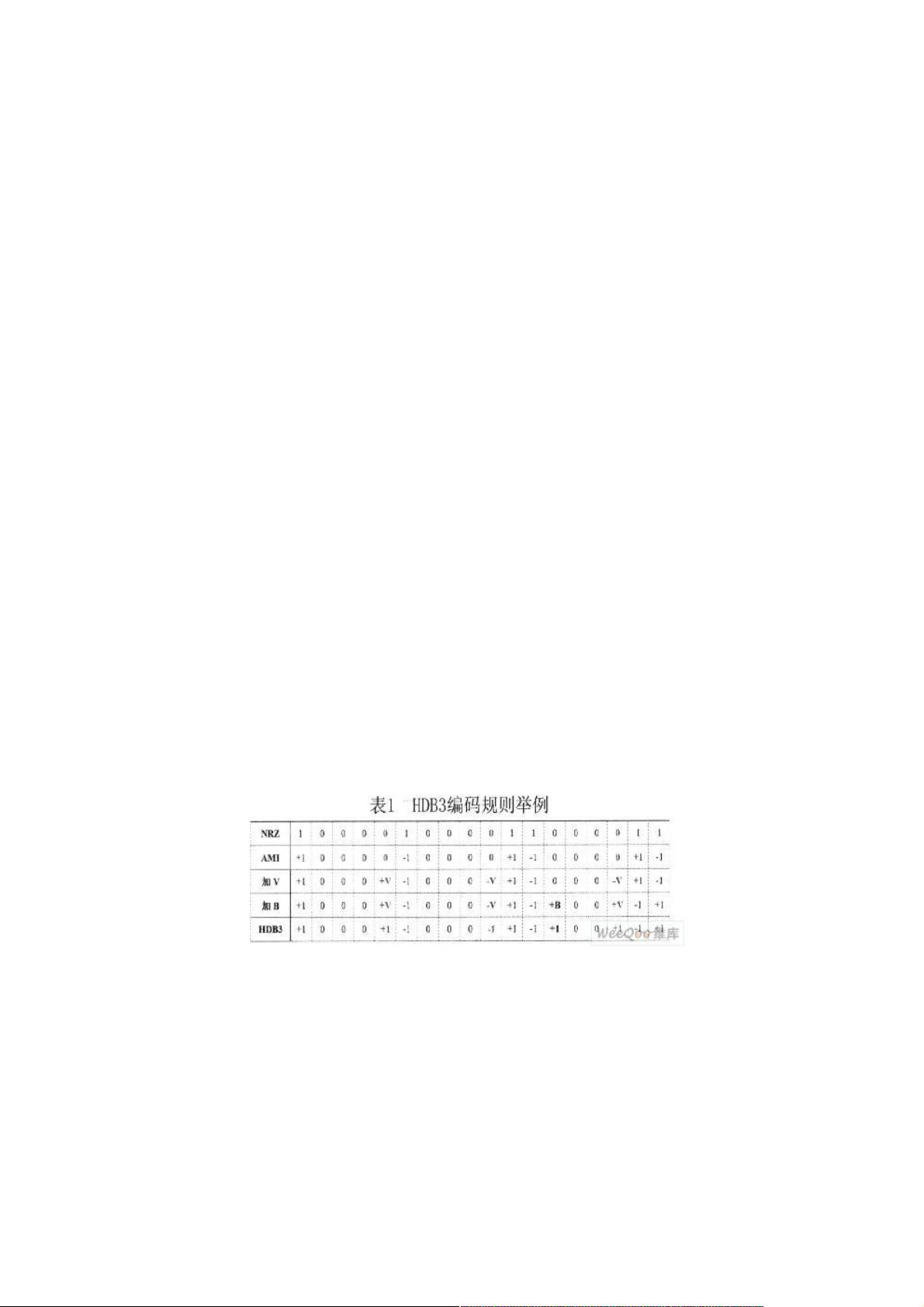

HDB3编码的基本原理是确保码流中最多连续出现三个零,通过插入补充码元来实现。当连续的零超过两个时,编码器会插入一个相反极性的码元,以保持码流的双极性特征。编码规则如下:

(1) 如果连续出现三个零,则插入一个正或负的补充码元,通常选择与前一个码元极性相反的码元,以维持交替的极性模式。

(2) 如果在插入补充码元后,又出现了连续的三个零,那么再次插入一个补充码元,但这次的极性与前一个补充码元相反,以此类推。

为了实现HDB3编码,本设计提出了采用EDA(电子设计自动化)技术的HDB3编码器。EDA技术使得硬件设计更加灵活、高效,允许快速开发和低成本实施。在这种设计中,使用了ACEX系列的FPGA(现场可编程门阵列)EPlK10作为硬件平台,Quartus II作为软件开发工具,而VHDL则作为设计语言,这些工具和平台使得编码器的电路结构简化,执行速度快,并且易于升级和维护。

设计流程包括以下几个步骤:

1. 分析HDB3编码的逻辑规则,将其转化为VHDL代码,描述编码器的逻辑功能。

2. 使用Quartus II进行逻辑综合,将VHDL代码转化为硬件逻辑门级表示。

3. 通过仿真验证编码器的正确性,确保在各种输入条件下都能按照HDB3编码规则正确输出。

4. 将综合后的设计下载到FPGA中,进行实际硬件测试,验证其在实际环境下的性能。

这种基于EDA技术的HDB3编码器不仅简化了硬件设计,降低了成本,还缩短了开发周期,而且由于FPGA的可编程性,使得设计可以针对不同的应用场景进行快速调整和优化。因此,这种方法对于需要高效、灵活且可靠的HDB3编码解决方案的通信系统来说,具有很高的实用价值。

2021-11-26 上传

2023-06-20 上传

2020-11-12 上传

点击了解资源详情

2020-10-18 上传

2020-12-04 上传

2021-01-19 上传

2020-12-03 上传

2021-07-13 上传

weixin_38732454

- 粉丝: 6

- 资源: 952