FPGA与ADC高速接口:LVDS应用策略详解

在现代电子系统设计中,FPGA(现场可编程门阵列)与ADC(模数转换器)之间的数字数据输出接口是一个关键环节,因为它们各自在信号处理和数据采集中扮演着核心角色。本文将深入探讨几种常见的接口协议和标准,特别是LVDS(低压差分信号)的应用。

首先,接口方式和标准的选择至关重要。对于低速数据传输,如200MHz以下,通常使用SDR(单倍数据速率)CMOS技术,其中发送和接收数据在不同时钟周期进行,确保数据稳定传输。然而,随着速度需求提升,DDR(双倍数据速率)CMOS成为选项,数据传输速度翻倍,但时序控制变得更加复杂。

LVDS作为一种高速接口标准,特别适合于高速数据转换器,如可达DDR1.6Gbps或800MHz的性能。它利用差分信号传输,P线和N线形成一对,提供了更好的噪声抑制能力和信号完整性。尽管LVDS的功耗较低,但其布线需求较多,特别是在“源同步”时钟系统中,时钟信号与数据同步发送,简化了接收器的捕获过程。

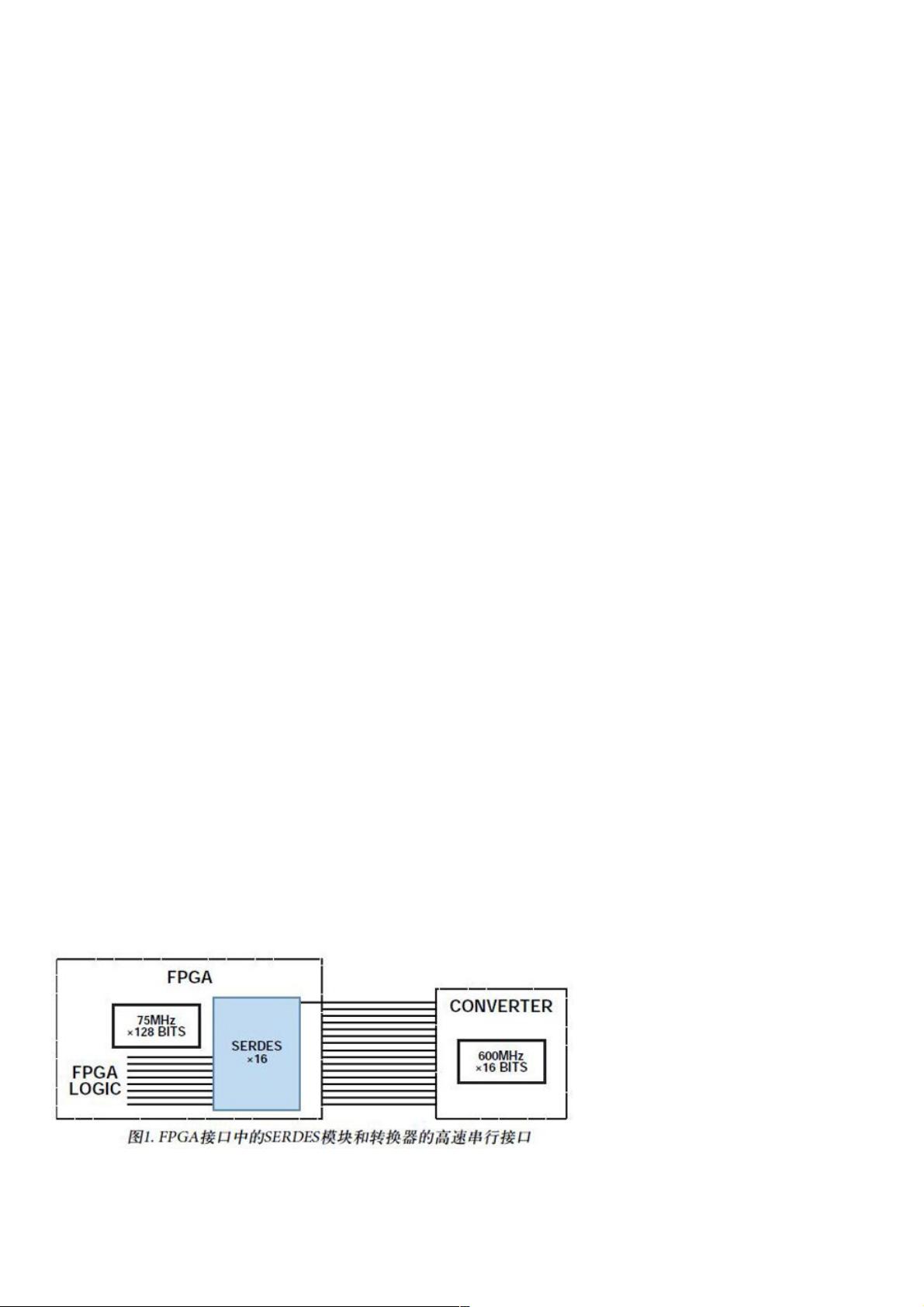

然而,由于FPGA的逻辑速度往往跟不上高速转换器的总线速度,所以许多FPGA内置了SERDES(串行器/解串器)模块。这个模块负责将高速、窄带的串行数据转换成FPGA能处理的慢速、宽带并行数据。通过降低数据输出速率,如1/2、1/4或1/8的时钟周期,有效地实现了数据解串。

在串行LVDS的应用中,数据速率时钟和帧时钟通常是必备的,尤其是在引脚数量有限但对速度要求高的情况下。串行LVDS的接口同样要考虑所有与并行LVDS相同的因素,如噪声抗干扰能力、电源管理等。

FPGA与ADC的接口设计不仅涉及到协议选择,还包括了如何优化LVDS信号传输,以适应不同速度和功耗需求,以及如何通过串行化来匹配FPGA内部的处理能力。理解这些细节对于确保系统性能、稳定性和成本效益至关重要。

215 浏览量

点击了解资源详情

点击了解资源详情

2024-11-02 上传

2024-11-02 上传

362 浏览量

2177 浏览量

471 浏览量

2260 浏览量

weixin_38667581

- 粉丝: 8

- 资源: 955

最新资源

- onthedollar-api:税额计算器

- IT385

- Software-Testing

- OpenCvSharp从入门到实践-(01)认识OpenCvSharp&开发环境搭建 Demo

- 更好的恐慌-受Python的回溯启发而产生的非常恐慌的回溯-Rust开发

- 行业文档-设计装置-高中英语教学用划线器.zip

- 文件上传必备jar包fileupload与io.rar

- Python图像处理PCA算法完整源码

- bewitchedlogin.github.io:bla bla bla bla bla

- sample

- 智睿学校网上评课系统 v8.4.0

- printf_on_BIOS

- 世界之窗浏览器(TheWorld) v5.0 Beta

- GIS-Portfolio

- 项目管理案例研究:项目:“诺尔特制造工厂的工厂分析集成”-IST 645管理信息系统项目

- Angkor_website:网页设计与开发班的学校项目