"FPGA编程指南-Vivado软件操作及Minisys实验报告"

需积分: 0 201 浏览量

更新于2024-01-18

收藏 6.72MB PDF 举报

FPGA 简介

FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,它是一种在可编程元件(如LUT、触发器等)的基础上实现逻辑功能和互连的专用集成电路。FPGA通过在硬件描述语言(HDL)中编写的程序,完成对逻辑块和互连资源的编程,从而实现特定的逻辑功能。FPGA的主要优势在于其灵活性和可重构性,可以根据不同的应用需求进行重新编程,而无需进行硬件改造。

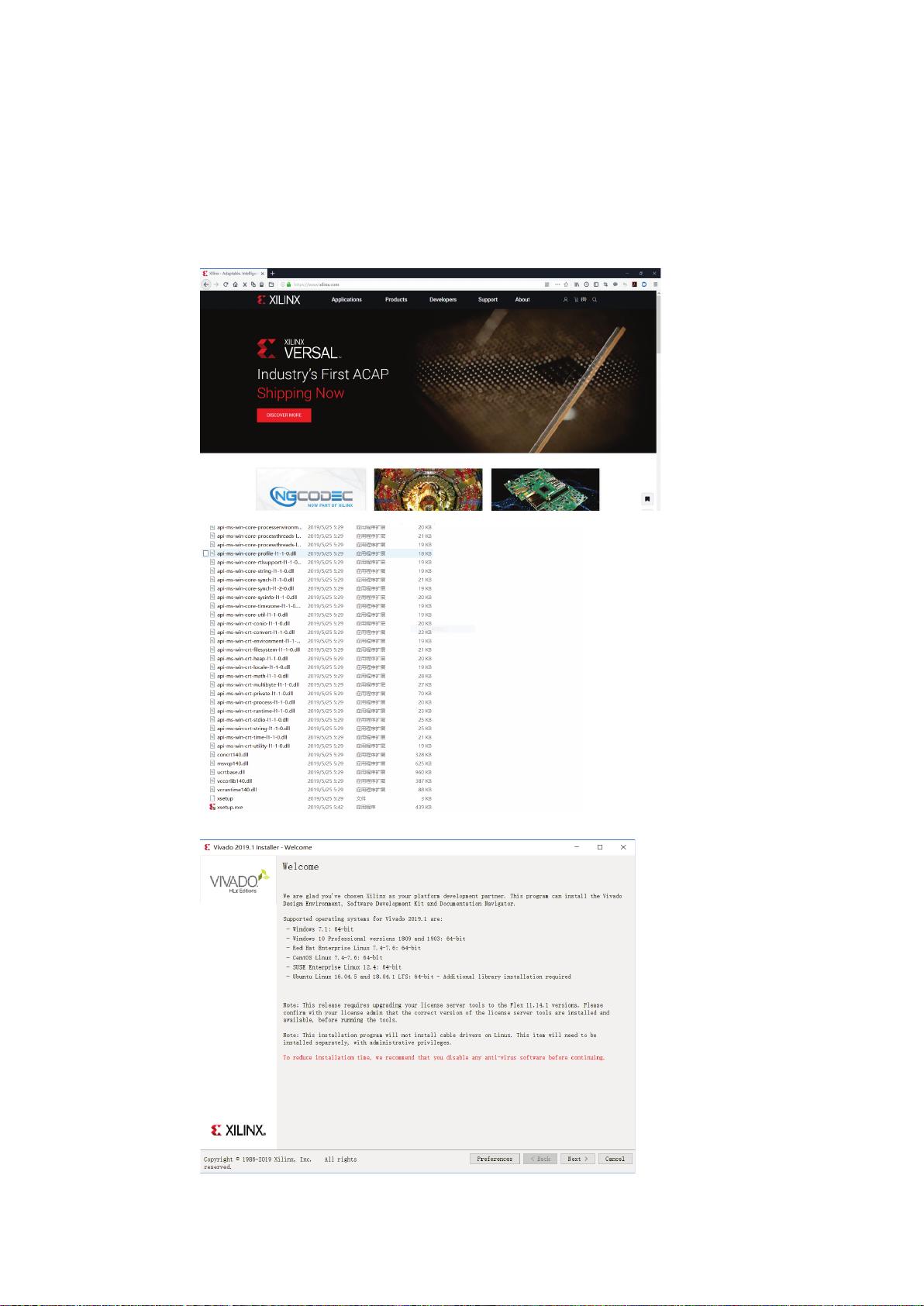

Vivado 软件下载安装及使用说明

Vivado是由Xilinx推出的一款集成开发环境(IDE)软件,用于FPGA设计与开发。首先,我们需要在Xilinx官网上下载Vivado软件,并根据指引进行安装。安装完成后,我们可以打开Vivado,并创建一个新项目。在创建项目时,需要指定FPGA型号和基本设计约束。接下来,可以选择添加设计文件,比如Verilog代码或VHDL代码。在设计文件添加完成后,可以进行代码仿真,以验证设计的正确性。

Minisys 实验平台介绍

Minisys是一款基于FPGA的实验开发平台,它集成了4*4键盘、8位七段显示和蜂鸣器等外设模块。通过Minisys平台,我们可以进行计算机组成原理相关的综合实验,比如流水灯实验等。

计算机组成原理综合实验实例

以流水灯实验为例,我们首先需要在Vivado中创建一个新项目,在项目中添加Verilog或VHDL代码,并进行代码仿真,以验证设计的正确性。接着,需要分配管脚并进行综合,最后生成二进制流文件。通过这些步骤,我们可以在Minisys平台上实现流水灯的效果,并进行实际的观察和测试。

实验总结

通过本次实验,我们深入了解了FPGA的基本原理和Vivado软件的使用方法。在实验过程中,我们对FPGA的内部结构有了更直观的了解,并通过实际操作掌握了FPGA设计与开发的基本流程。同时,我们也学习了如何在Minisys平台上进行计算机组成原理相关的综合实验,加深了对计算机组成原理知识的理解。

附录

在附录部分,我们可以添加一些实验过程中用到的代码、图片及实验数据等内容,以供更详细的参考。

综上所述,本次实验旨在通过Vivado软件在Minisys平台上进行FPGA设计与开发的综合实验,加深对FPGA原理和计算机组成原理的理解,同时也培养了我们在FPGA设计与开发领域的能力。希望通过本次实验,能够对参与者在FPGA领域的学习和实践起到积极的促进作用。

2023-07-14 上传

2022-08-08 上传

2022-08-08 上传

2015-12-27 上传

2009-09-11 上传

2024-09-15 上传

2021-04-22 上传

2021-03-21 上传

易烫YCC

- 粉丝: 30

- 资源: 315

最新资源

- CCOmPort,CRC32的c语言源码实现,c语言程序

- csanim:就像manim,但用于计算机科学!

- QT 编写的编译器,高亮显示,显示行号,一般编辑器的功能,代码填充

- Devopslearning

- react-project

- 大气扁平家居设计网站模板

- 家居装饰公司网站模板

- Raspi-rfid-temp

- cksc2.0,c语言中代码源码都是啥意思,c语言程序

- 串口调试助手 小程序 工具

- DeliverIt-documentation

- NginxAccess_AutoConfig:动态IPAddress进行Nginx访问配置(白名单)

- RegDiff:查找两个Windows注册表状态之间的差异-开源

- LiScEig 1.0:用于常规 Sturm-Liouville 问题的 MATLAB 应用程序。-matlab开发

- Myportforio1

- Proyecto-R-Face:R-Face Project是用Python编写的软件,利用Opencv库进行人脸识别

已收录资源合集

已收录资源合集