MAX+PLUSII入门教程:从安装到授权

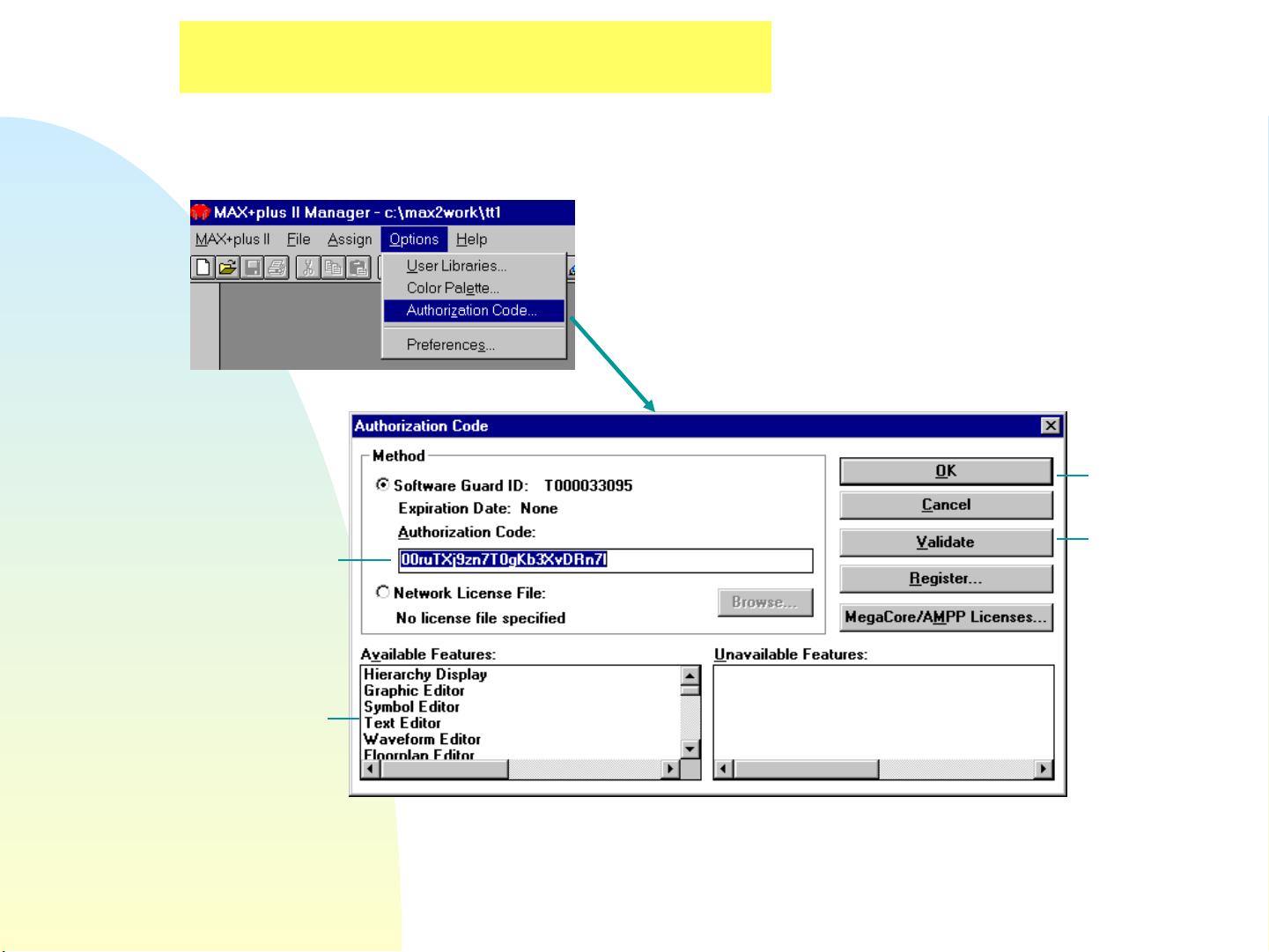

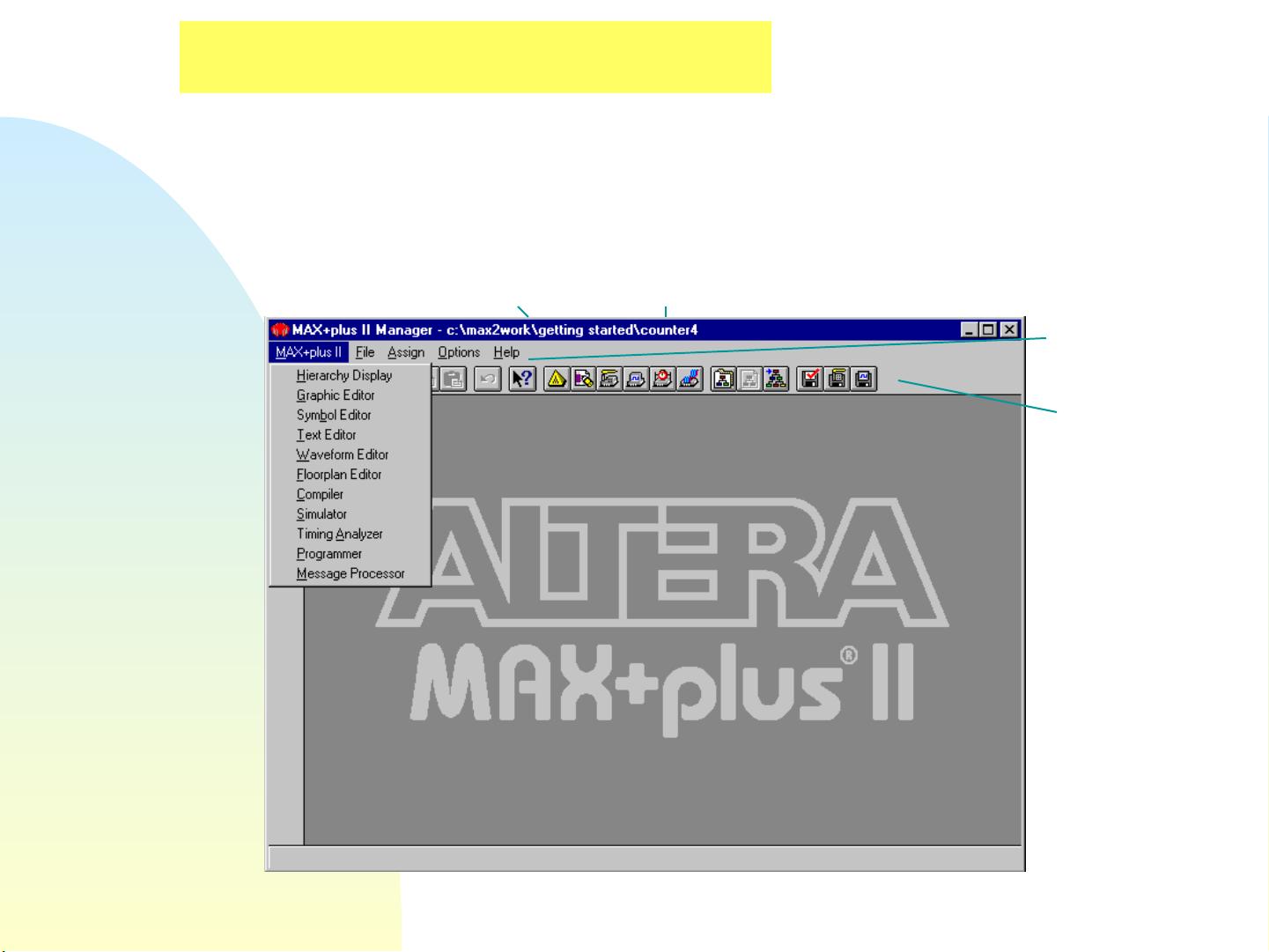

"Max+PlusII实用手册是一个针对初学者的简易入门指南,涵盖了软件的基本使用方法,包括设计输入、项目编译、器件编程等核心功能。手册还介绍了时间分析器、图形编辑器、文本编辑器、编程器、编译器、网表提取器、适配、逻辑综合器、数据库、建库器以及信息处理器等工具的使用。通过ES-Site和PLS-WEB,用户可以支持Classic、MAX5000、MAX7000(S)系列以及其他特定器件的设计。安装过程包括运行光盘中的安装程序,按照屏幕提示进行,并在成功安装后阅读read.me文件获取重要信息。首次运行MAX+PlusII需要进行ES-Site授权,包括申请和输入授权代码的步骤。"

在深入讲解Max+PlusII之前,我们先了解一下它的基础。Max+PlusII是一款由Altera公司开发的硬件描述语言(HDL)综合器和配置工具,主要用于设计和实现基于FPGA(现场可编程门阵列)和CPLD(复杂可编程逻辑器件)的数字系统。这个软件集成了设计流程的多个阶段,包括设计输入、编译、仿真、时序分析、布局布线以及器件编程。

1. **设计输入**:用户可以通过文本编辑器输入VHDL或Verilog代码,或者使用图形编辑器构建逻辑电路图。这些设计文件可以是用户自己创建的,也可以是从第三方工具导入的。

2. **项目编译**:在完成设计输入后,用户可以使用MAX+PlusII的编译器进行编译。这个过程包括语法检查、逻辑综合、时序优化和适配等步骤,将高级语言描述转化为适合目标器件的逻辑门级表示。

3. **项目校验**:在编译过程中,Max+PlusII会进行功能仿真和时序分析,确保设计在逻辑上正确且满足时序要求。

4. **器件编程**:一旦设计经过验证,用户可以使用编程器将生成的配置文件下载到目标FPGA或CPLD中,实现硬件电路的功能。

5. **时间分析器**:此功能用于评估设计的时序性能,提供关键路径的信息,帮助优化设计。

6. **图形编辑器**和**文本编辑器**:这两个工具分别用于图形化设计和文本编辑,为用户提供灵活的设计方式。

7. **ES-Site和PLS-WEB**:这两个特性允许用户支持多种Altera器件,提供了更广泛的设计平台。

8. **授权过程**:安装完成后,用户需要申请并输入ES-Site授权代码,这是使用软件的必要步骤,通常通过电子邮件或Altera公司的网站完成。

9. **数据库和建库器**:数据库存储设计信息,建库器则用于创建和管理自定义的逻辑库,方便复用和组织设计元素。

10. **信息处理器**:处理设计过程中产生的各种信息,如错误报告、警告信息等。

通过这个手册,初学者能够逐步学习和掌握Max+PlusII的使用,从而有效地进行数字系统的设计和实现。理解并熟练运用这些工具,是成为合格的FPGA/CPLD设计工程师的基础。

2023-07-13 上传

2013-03-26 上传

2011-12-09 上传

2022-09-22 上传

429 浏览量

2009-09-15 上传

2010-04-20 上传

yimaojing

- 粉丝: 0

- 资源: 1

最新资源

- 利用J2EE+Apache Tomcat搭建J2EE环境

- EIGRP的不等价负载均衡.pdf

- 搞活 富裕挥发油 答合金钢合金钢环境

- 函数信号发生器,函数信号发生器

- Struts2+Spring应用电子书

- ASP电子商务毕业设计论文

- Support Vector Machines for Classification and Regression

- dreamweaver asp 网上选课系统论文

- java笔记.pdf

- Flex 3 Cookbook

- 《控制反转,依赖注入》

- Flex与JSON及XML的互操作

- SQL语言艺术.pdf

- struts中文手册

- linux下搭建iscsi

- 软件无线电设计的A_D采样分析.pdf