HyperLynx DDR3后布局信号完整性仿真教程

下载需积分: 10 | DOCX格式 | 2.35MB |

更新于2024-07-09

| 10 浏览量 | 举报

"HyperLynx内存下DDR3后布局仿真SOP"

HyperLynx是一款强大的信号完整性(SI)和电源完整性(PI)仿真工具,广泛应用于电子设计领域,特别是对于高速数字系统如DDR3内存接口的设计验证。该文档详细介绍了如何使用HyperLynx进行DDR3内存的后布局信号完整性仿真,以确保设计满足性能要求。

首先,仿真的第一步是将PCB(印刷电路板)文件导入到HyperLynx中。这通常通过在Xpedition PCB设计环境中选择“Analysis”菜单,然后选择“Export To HyperLynx Signal Integrity”来实现。这一过程允许设计师将设计的物理布局与HyperLynx连接,以便进行信号完整性的分析。

接下来,设置叠层结构至关重要,因为这直接影响信号的传播特性。在HyperLynx中,通过“Setup Stackup Edit”可以定义每层的材料属性,包括厚度、介电常数和损耗角正切。这些参数需根据实际PCB材料的规格进行精确设定,以确保仿真结果的准确性。

在设置电源供应时,需要为DDR3信号拓扑中的电源平面如DSPA_VCC0V75指定正确的电压值。这在“Setup Power Supplies”中完成,通过“Edit Power-Supply Nets”对话框,找到相应的电源网络并输入实际电压值。

为了进行仿真,需要导入控制器和内存颗粒的IBIS(Input/Output Buffer Information Specification)模型。IBIS模型描述了电路元件的输入输出行为,是进行信号完整性仿真的关键。这些模型通常放在HyperLynx的库目录下,路径取决于操作系统是32位还是64位。

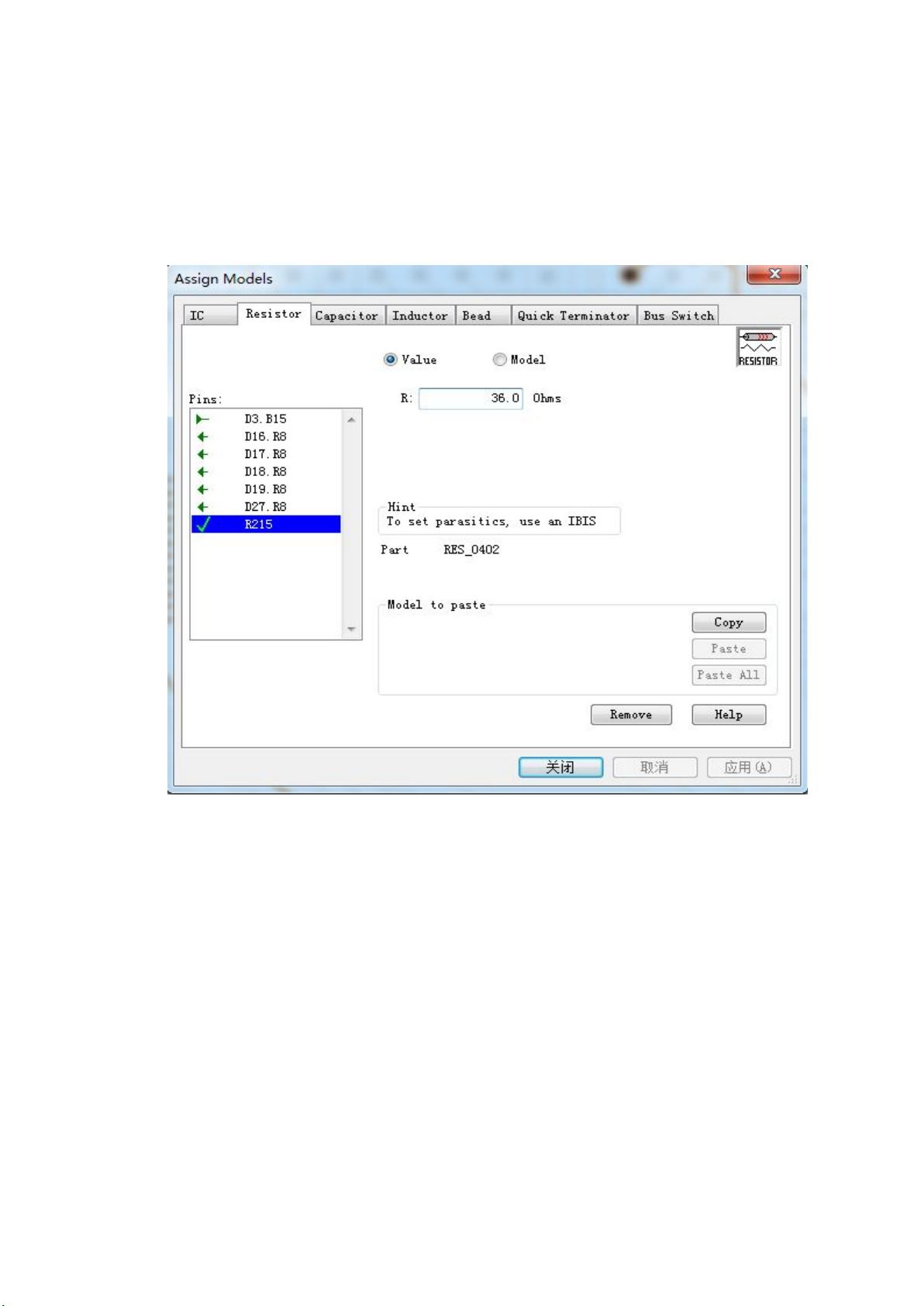

在选择要仿真的信号线(例如DSPB_DDR3_EDQ0)后,分配模型到相应的网络。在“Models Assign Models Values by Net”中,可以设置驱动端为Output,接收端为Input,确保模型正确地应用到每个信号线上。

接着,为信号线D3和D19选择合适的IBIS模型,并通过“Model Selector”确认模型分配。一旦所有模型分配完毕,便可以开始交互式仿真。

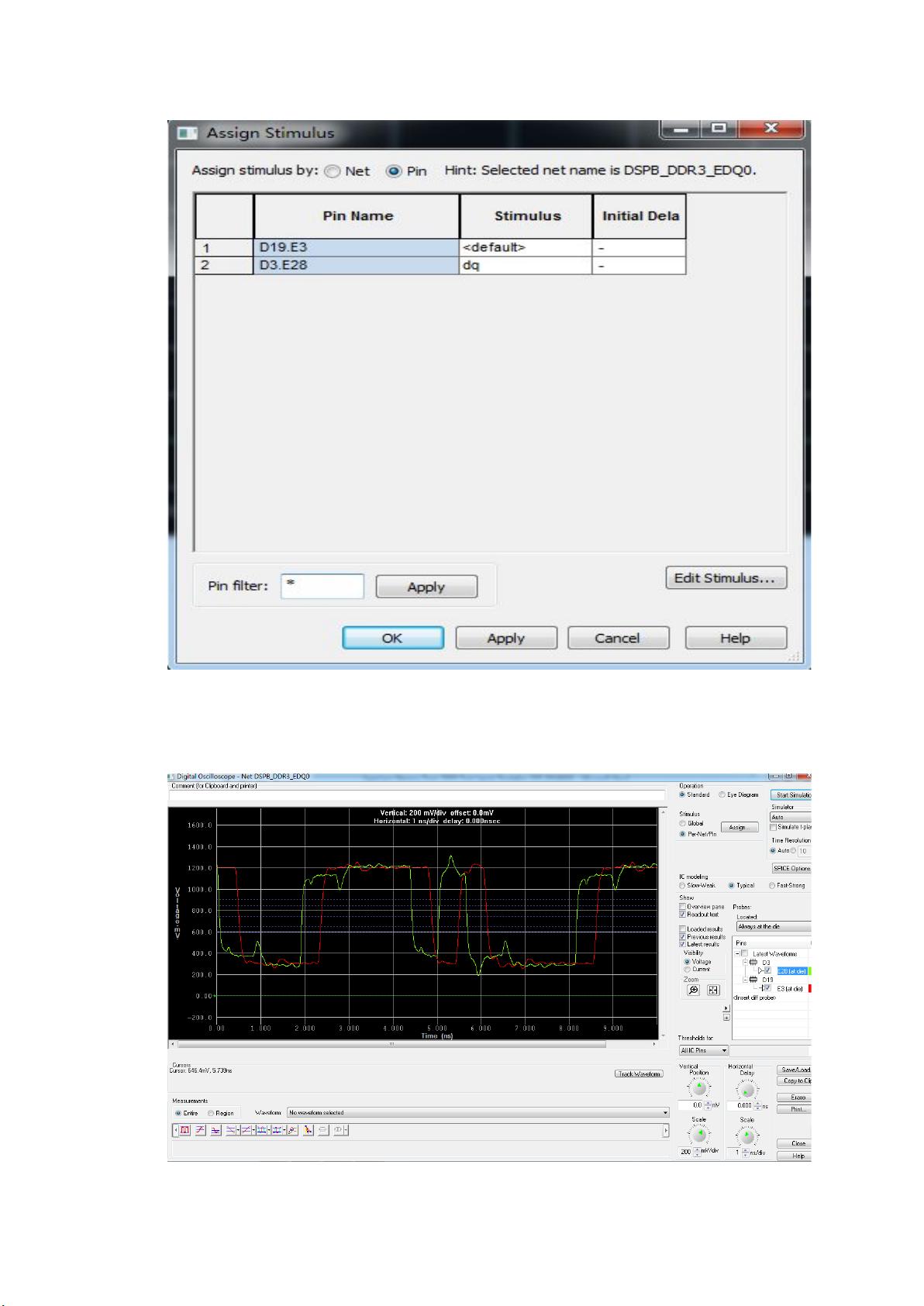

最后,设置仿真激励(Stimulus)。在“Simulate SIRun Interactive Simulation”中,勾选“Per-Net/Pin”的Stimulus选项,然后在“Assign Stimulus”界面中,将预定义的Stimulus(如dq)分配给D3。完成这些步骤后,选择适当的IC Modeling类型,点击“Start Simulation”开始仿真。

仿真的结果会显示信号的质量,包括眼图、时序分析和其他关键性能指标,设计师可以根据这些结果调整设计以优化信号完整性,防止信号失真或抖动。

总结来说,HyperLynx Memory Down DDR3 Simulation SOP是一个详细指导,涵盖了从导入PCB设计到设置叠层、电源、模型分配,再到仿真设置和结果分析的全过程,对于进行DDR3内存设计的工程师来说,是一个宝贵的参考资源。

相关推荐

clare0807

- 粉丝: 8

- 资源: 10

最新资源

- 送药小车毕业设计送药小车毕业设计

- sxiv-patches:一组用于sxiv图像查看器的补丁

- minikube-nfs-test:在minikube上安装NFS服务器客户端的各种资源

- FreeRiderHMC

- Box's Evolutionary algorithm:求解多变量无约束优化-matlab开发

- 动科(DK)企业网站管理系统 v9.2

- scheamer

- Karabiner-Elements-12.8.0.dmg.zip

- 校园志愿者活动管理系统-志愿者小程序(含管理后台)-毕业设计

- ditto-subgraph

- astlog:星号SIP日志解析器

- Addon-Bluetooth-WebGUI:适用于FABI和FLipMouse的ESP32插件,添加了蓝牙和WiFiWebGUI支持

- 模拟

- MP4

- unist-util-modify-children:修改父母直系子女的实用程序

- 信呼协同办公系统 v1.6.0