MC14LC5480MOTOROLA

5

version algorithm. All of the analog circuitry involved in the

data conversion (the voltage reference, RDAC, CDAC, and

comparator) are implemented with a differential architecture.

The receive section includes the DAC described above, a

sample and hold amplifier, a 5–pole, 3400 Hz switched ca-

pacitor low–pass filter with sinX/X correction, and a 2–pole

active smoothing filter to reduce the spectral components of

the switched capacitor filter. The output of the smoothing fil-

ter is buffered by an amplifier, which is output at the RO+ and

RO– pins. These outputs are capable of driving a 4 kΩ load

differentially or a 2 kΩ load to the V

AG

pin. The MC14LC5480

also has a pair of power amplifiers that are connected in a

push–pull configuration. The PI pin is the inverting input to

the PO– power amplifier. The non–inverting input is internally

tied to the V

AG

pin. This allows this amplifier to be used in an

inverting gain circuit with two external resistors. The PO+

amplifier has a gain of minus one, and is internally con-

nected to the PO– output. This complete power amplifier cir-

cuit is a differential (push–pull) amplifier with adjustable gain

that is capable of driving a 300 Ω load to +12 dBm. The

power amplifier may be powered down independently of the

rest of the chip by connecting the PI pin to V

DD

.

POWER–DOWN

There are two methods of putting this device into a low

power consumption mode, which makes the device nonfunc-

tional and consumes virtually no power. PDI

is the power–

down input pin which, when taken low, powers down the

device. Another way to power the device down is to hold both

the FST and FSR pins low. When the chip is powered down,

the V

AG

, TG, RO+, RO–, PO+, PO–, and DT outputs are high

impedance. To return the chip to the power–up state, PDI

must be high and the FST frame sync pulse must be present.

The DT output will remain in a high–impedance state for at

least two FST pulses after power–up.

MASTER CLOCK

Since this codec–filter design has a single DAC architec-

ture, the MCLK pin is used as the master clock for all analog

signal processing including analog–to–digital conversion,

digital–to–analog conversion, and for transmit and receive fil-

tering functions of this device. The clock frequency applied to

the MCLK pin may be 256 kHz, 512 kHz, 1.536 MHz,

1.544 MHz, 2.048 MHz, 2.56 MHz, or 4.096 MHz. This de-

vice has a prescaler that automatically determines the proper

divide ratio to use for the MCLK input, which achieves the re-

quired 256 kHz internal sequencing clock. The clocking re-

quirements of the MCLK input are independent of the PCM

data transfer mode (i.e., Long Frame Sync, Short Frame

Sync, IDL mode, or GCI mode).

DIGITAL I/O

The MC14LC5480 is pin selectable for Mu–Law or A–Law.

Table 1 shows the 8–bit data word format for positive and

negative zero and full scale for both companding schemes

(see Tables 3 and 4 at the end of this document for a com-

plete PCM word conversion table). Table 2 shows the series

of eight PCM words for both Mu–Law and A–Law that corre-

spond to a digital milliwatt. The digital mW is the 1 kHz cal-

ibration signal reconstructed by the DAC that defines the

absolute gain or 0 dBm0 Transmission Level Point (TLP) of

the DAC. The 0 dBm0 level for Mu–Law is 3.17 dB below the

maximum level for an unclipped tone signal. The 0 dBm0

level for A–Law is 3.14 dB below the maximum level for an

unclipped tone signal. The timing for the PCM data transfer is

independent of the companding scheme selected. Refer to

Figure 2 for a summary and comparison of the four PCM

data interface modes of this device.

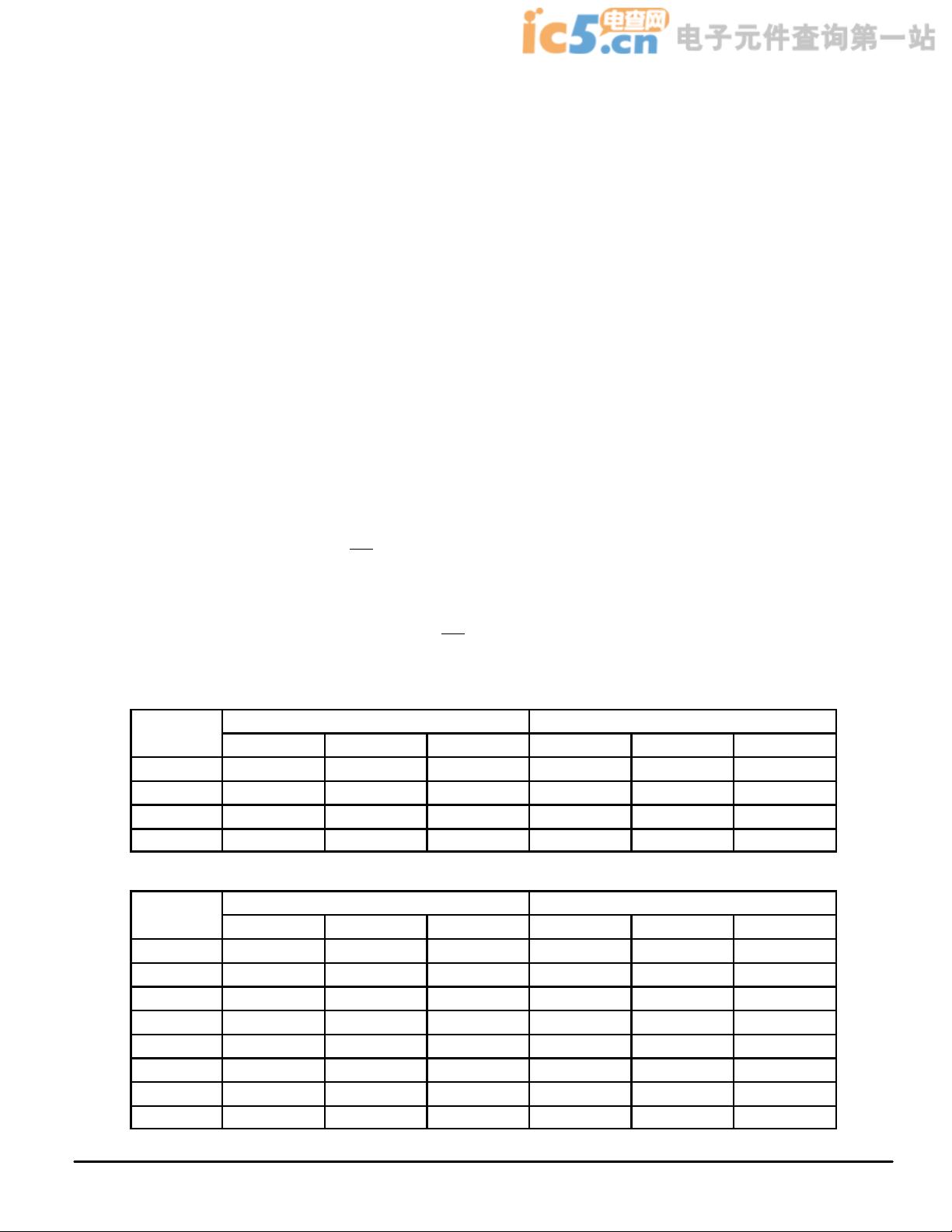

Table 1. PCM Codes for Zero and Full Scale

Mu–Law A–Law

Level

Sign Bit Chord Bits Step Bits Sign Bit Chord Bits Step Bits

+ Full Scale 1 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0

+ Zero 1 1 1 1 1 1 1 1 1 1 0 1 0 1 0 1

– Zero 0 1 1 1 1 1 1 1 0 1 0 1 0 1 0 1

– Full Scale 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0

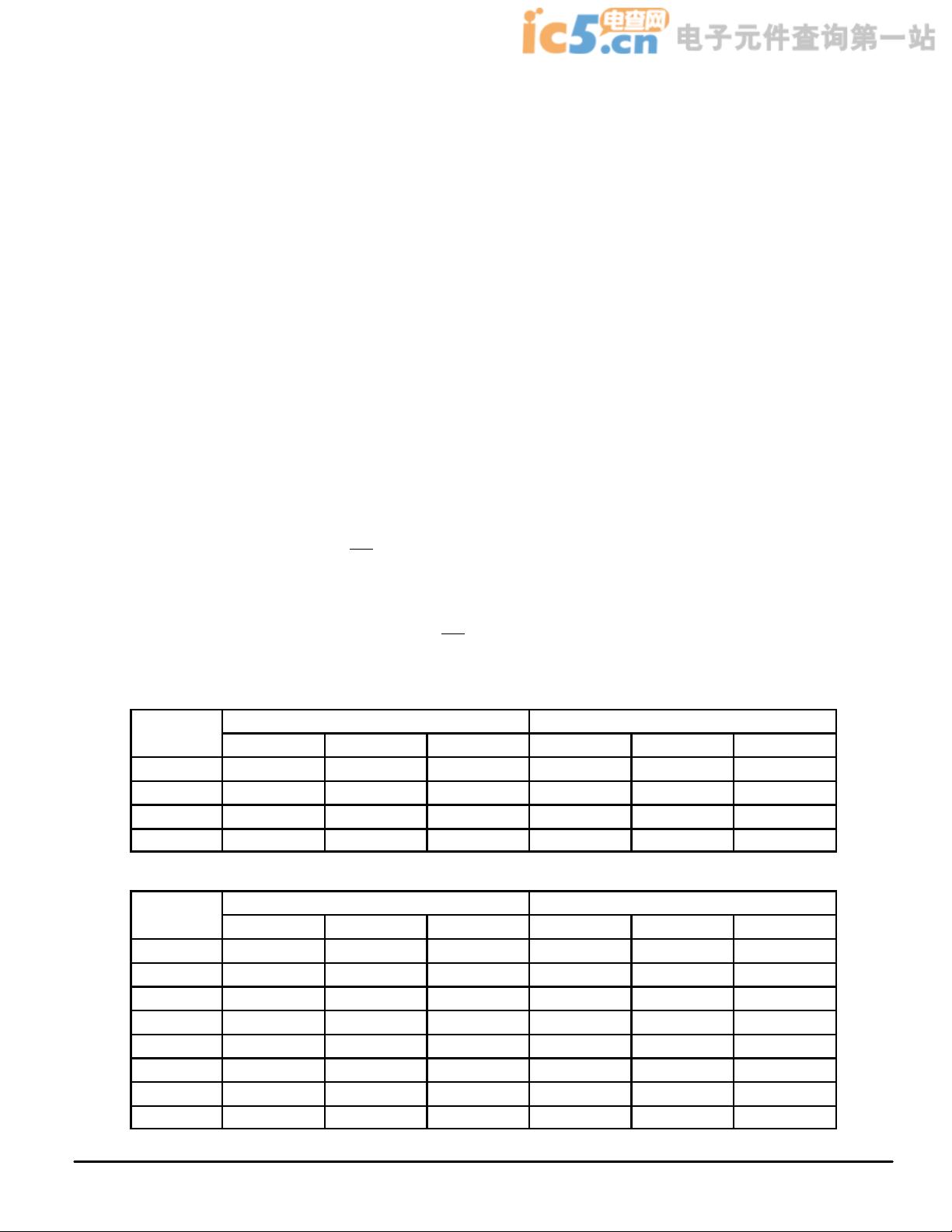

Table 2. PCM Codes for Digital mW

Mu–Law A–Law

Phase

Sign Bit Chord Bits Step Bits Sign Bit Chord Bits Step Bits

π/8 0 0 0 1 1 1 1 0 0 0 1 1 0 1 0 0

3π/8 0 0 0 0 1 0 1 1 0 0 1 0 0 0 0 1

5π/8 0 0 0 0 1 0 1 1 0 0 1 0 0 0 0 1

7π/8 0 0 0 1 1 1 1 0 0 0 1 1 0 1 0 0

9π/8 1 0 0 1 1 1 1 0 1 0 1 1 0 1 0 0

11π/8 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1

13π/8 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1

15π/8 1 0 0 1 1 1 1 0 1 0 1 1 0 1 0 0