FPGA入门:数字电路与逻辑设计基础

需积分: 17 166 浏览量

更新于2024-07-29

收藏 672KB PDF 举报

"FPGA入门教程"

本教程是针对FPGA初学者的一份综合指南,旨在帮助读者理解并掌握FPGA的基础知识和开发流程。FPGA(Field-Programmable Gate Array),即现场可编程门阵列,是一种集成电路,允许用户根据需求自定义逻辑功能。在数字电路设计中,FPGA因其灵活性和高速处理能力而在众多领域得到广泛应用。

1. 数字电路设计入门

- 逻辑设计:数字电路设计基于逻辑门,如与门、或门、非门等,通过这些基本单元构建复杂的逻辑功能。

- 电平标准:不同的逻辑电平标准(如TTL、CMOS等)用于确保电路间的兼容性和正确通信。

- 组合逻辑电路:不依赖于历史状态,仅由当前输入决定输出的电路,如加法器、编码器、解码器等。

- 时序逻辑电路:包含内部存储元件(如触发器),其输出不仅取决于当前输入,还与先前的状态有关,例如计数器、寄存器等。

2. FPGA简介

- FPGA的优势:可重复编程、快速原型验证、高性能、低功耗。

- FPGA结构:由可配置逻辑块、输入/输出单元、布线资源等构成,支持用户自定义逻辑设计。

3. FPGA开发流程

- 设计概念化:确定系统功能和性能要求。

- RTL设计:使用硬件描述语言(如VHDL或Verilog)编写代码。

- 布局与布线:编译和优化设计,分配逻辑资源。

- 仿真验证:通过软件工具(如ModelSim)模拟设计行为,确保正确性。

- 时序分析:检查设计满足速度和时序约束。

- 下载与测试:将编译后的比特流加载到FPGA上进行实际测试。

4. RTL设计

- RTL(Register Transfer Level)描述了数据在寄存器之间的转移和处理过程,是FPGA设计的关键步骤。

- 使用高级语言(如SystemVerilog、VHDL)描述硬件逻辑。

5. QuartusⅡ设计实例

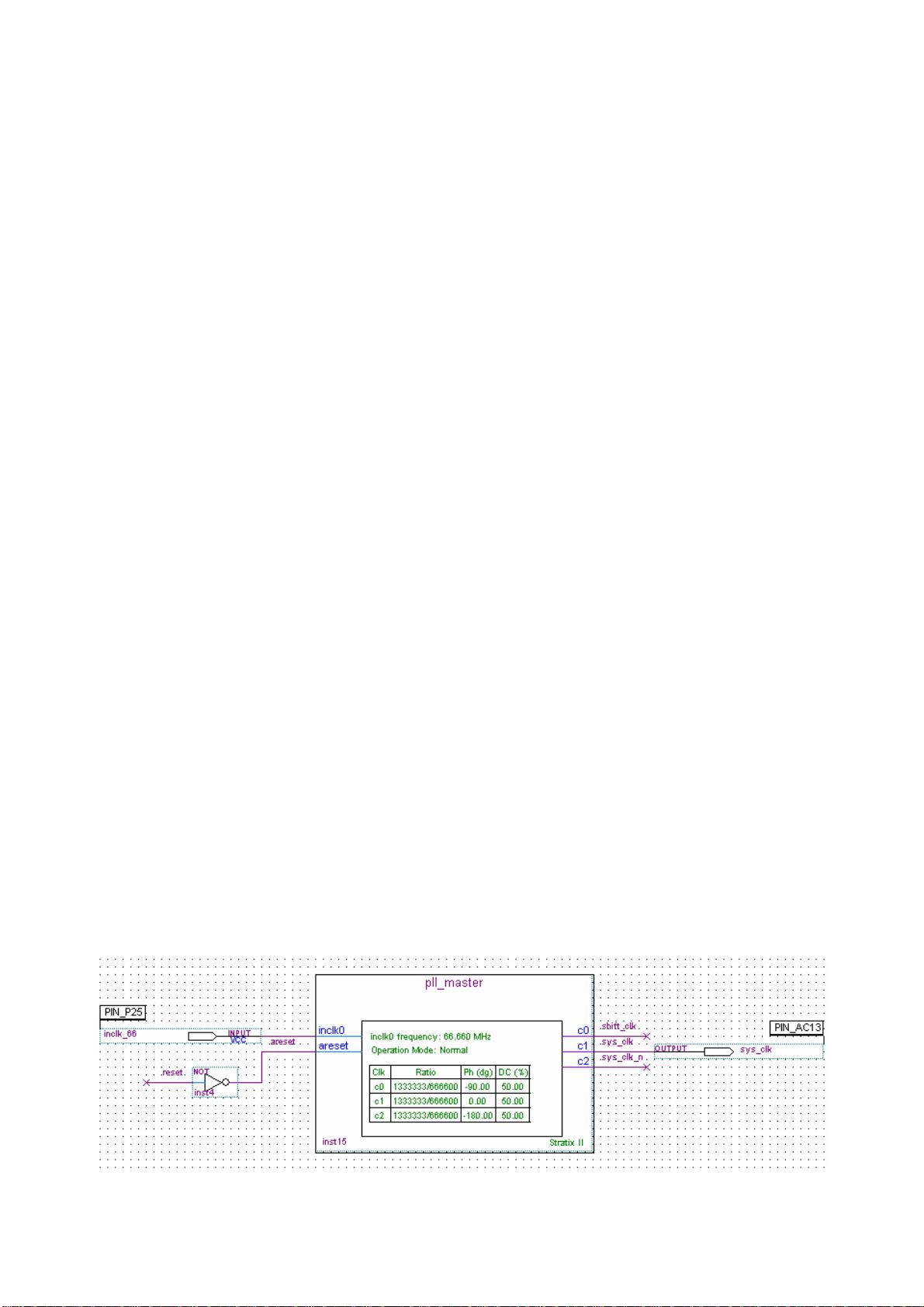

- QuartusⅡ是Altera(现Intel FPGA)提供的开发工具,用于FPGA设计、综合、布局和布线等。

- 学习如何创建项目、编写VHDL/Verilog代码、设置约束、编译和下载到FPGA板上。

6. ModelSim和Testbench

- ModelSim是常用的仿真工具,用于验证RTL代码的功能。

- Testbench是为验证设计而创建的虚拟环境,模拟输入信号和预期的输出响应。

在FPGA学习过程中,了解数字电路基础,掌握硬件描述语言以及熟悉FPGA开发工具至关重要。通过实践项目,如时钟分频器,可以加深对时序逻辑的理解,进一步提升设计技能。随着经验的积累,可以逐步挑战更复杂的设计,如高速接口、数字信号处理、嵌入式系统等。

2009-01-09 上传

2024-06-19 上传

2011-10-31 上传

2009-01-13 上传

点击了解资源详情

2024-12-19 上传

2024-12-19 上传

scowuyue

- 粉丝: 0

- 资源: 12

最新资源

- Elasticsearch核心改进:实现Translog与索引线程分离

- 分享个人Vim与Git配置文件管理经验

- 文本动画新体验:textillate插件功能介绍

- Python图像处理库Pillow 2.5.2版本发布

- DeepClassifier:简化文本分类任务的深度学习库

- Java领域恩舒技术深度解析

- 渲染jquery-mentions的markdown-it-jquery-mention插件

- CompbuildREDUX:探索Minecraft的现实主义纹理包

- Nest框架的入门教程与部署指南

- Slack黑暗主题脚本教程:简易安装指南

- JavaScript开发进阶:探索develop-it-master项目

- SafeStbImageSharp:提升安全性与代码重构的图像处理库

- Python图像处理库Pillow 2.5.0版本发布

- mytest仓库功能测试与HTML实践

- MATLAB与Python对比分析——cw-09-jareod源代码探究

- KeyGenerator工具:自动化部署节点密钥生成