Design of a Digital PID Regulator Based on Look-Up Tables

for Control of High-Frequency DC-DC Converters

Aleksandar Prodić and Dragan Maksimović

Colorado Power Electronics Center

Department of Electrical and Computer Engineering

University of Colorado at Boulder

Boulder, CO 80309-0425, USA

Aleksandar.Prodic@colorado.edu

Abstract – This paper describes design of a digital PID

regulator based on look-up tables for high frequency dc-dc

switching converters. The use of the look-up tables instead of

multipliers enables a small, low-power implementation and

operation at high switching frequencies. Design guidelines are

given for the resolution and size of entries in the look-up

tables. A design example and experimental results are

presented for a digital controller IC used to control a 1 MHz,

2.7 V, 3 W buck converter.

I. INTRODUCTION

Digital controllers can offer a number of advantages over

analog controllers, including flexibility, lower sensitivity,

and programmability without external components [1-6].

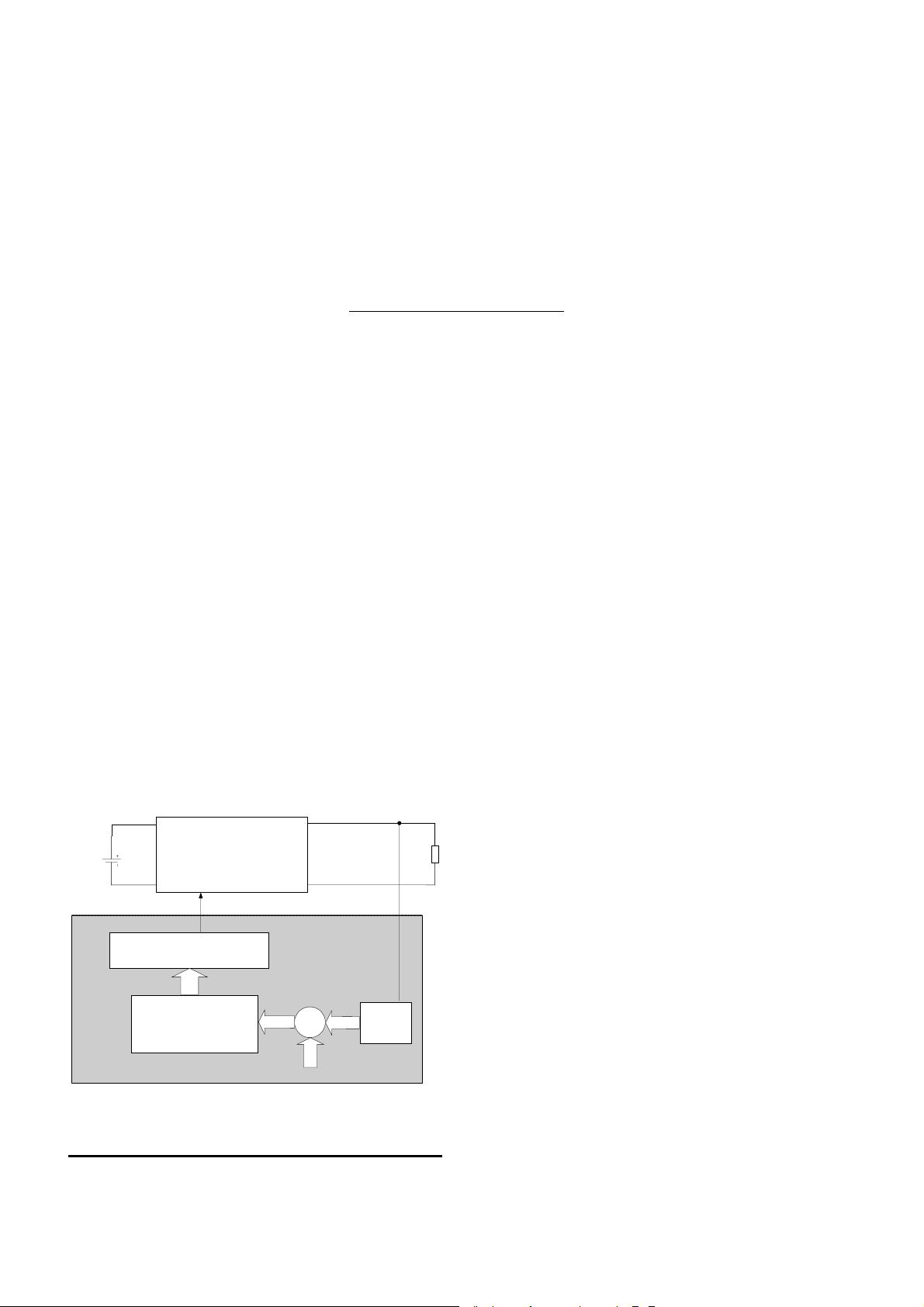

Figure 1 shows a digitally controlled switching converter.

It consists of an analog-to-digital converter, a processing

unit (regulator) that implements a control law, and a digital

pulse width modulator (DPWM). In order to achieve

dynamic characteristics comparable with analog PWM

controllers, fast implementation of a discrete-time control

law is required. For cost-driven low-power, high-frequency

applications, simplicity, small size and low power

consumption are important. In order to implement a digital

controller for these applications, hardware optimization is

needed. The hardware requirements that DPWM and

Load

V

in

A/D

Regulator

(Processing unit)

Digital Pulse Width

Modulator (DPWM)

Switching Converter

V

out

(t)

+

-

d[n]

+

V

ref

[n]

-

V

out

[n]

e[n]

d(t)

Figure 1. Block diagram of a digitally controlled dc-dc switching

converter.

This work was supported by National Semiconductor Corp. through the

Colorado Power Electronics Center.

analog-to-digital converter have to satisfy are defined in [7,

8]. In this paper, we focus on minimum hardware

requirements for the computational unit that implements a

discrete-time PID control law.

In Section II, the regulator structure is given and problems

of conventional implementation based on multipliers are

addressed. Design guidelines for selection of the resolution

of the computational unit are given in Section III. Section

IV shows experimental results obtained with an on-chip

implemented, look-up table based regulator for a buck

converter operating at 1 MHz switching frequency.

II. REGULATOR STRUCTURE

In the controller of Figure 1, the sampled output voltage is

compared to a reference and their difference forms an error

signal. A regulator that implements a control law processes

the error signal. The control law can be represented in the

following form:

...]2[]1[

][..]2[]1[][

21

021

+−+−+

+++−+−=

nene

nendndnd

ββ

βαα

(1)

where d[n] and e[n] are the current values of the duty ratio

and the error signal, while d[n-i] and e[n-i] are the values

of the duty ratio and the error signal i cycles before the

current cycle. The coefficients α

i

and β

i

determine the

regulator characteristics.

It can be seen that implementation of the discrete-time

control law (1) requires several multiplications and

additions. Digital multipliers are relatively large or slow

components.

For a properly operating feedback system, the difference

between the measured output voltage and the reference is

relatively small. This opens the possibility of

implementing the regulator using relatively small look-up

tables instead of multipliers [3].