Verilog实现数码管动态显示电子时钟

需积分: 23 79 浏览量

更新于2024-11-06

收藏 64KB DOC 举报

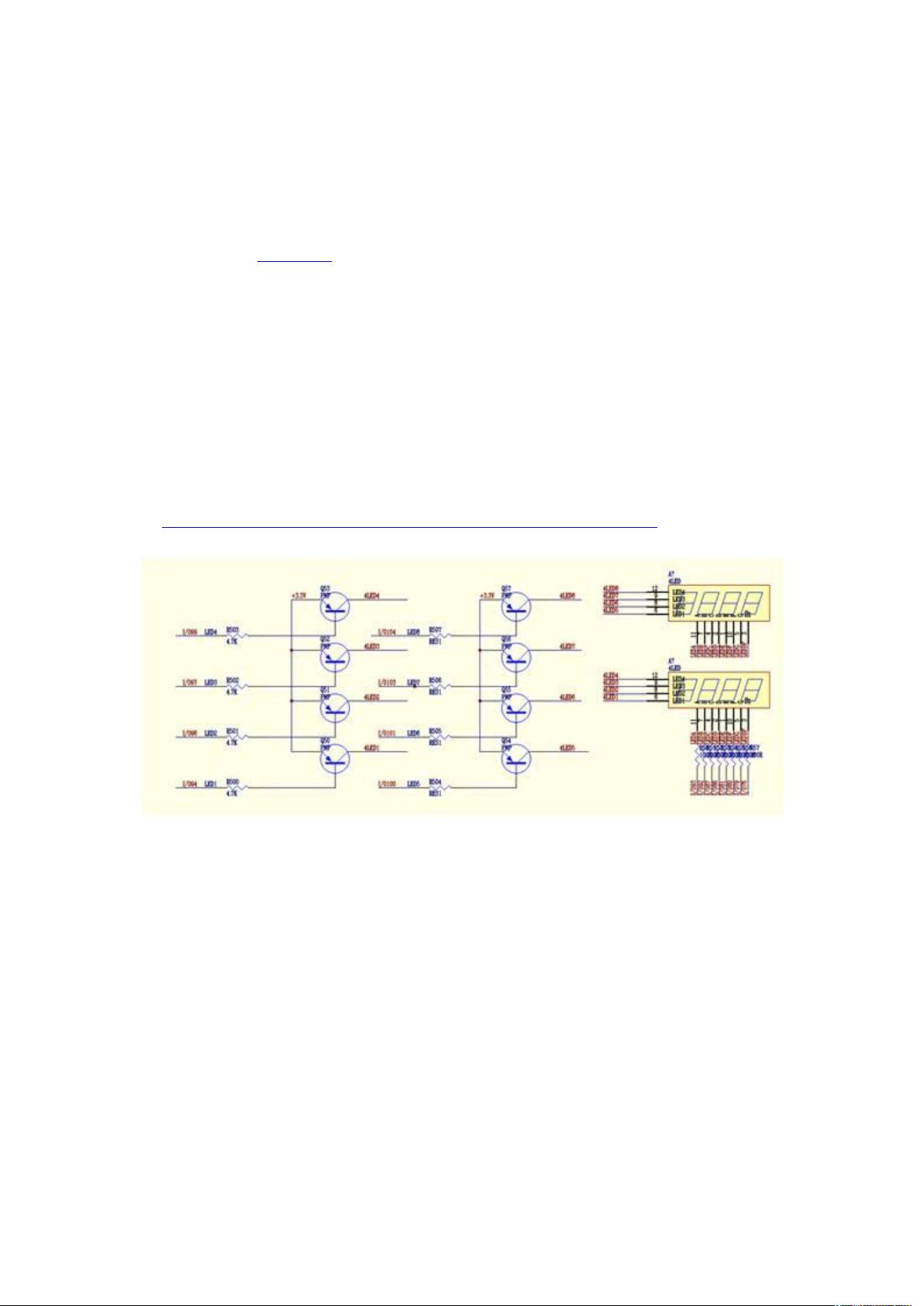

"这篇文档介绍了一个使用Verilog语言设计的数码管显示电子时钟项目,旨在帮助初学者通过简单的项目逐步学习。作者分享了程序代码并讨论了动态扫描显示技术,利用视觉暂留原理实现数码管同时点亮的效果。项目在一块实验板上实施,采用共阳极数码管,低电平选通。"

在电子设计领域,数码管显示是一种常见的输出设备,用于显示数字或特定字符。在这个项目中,作者设计了一个基于动态扫描的数码管显示系统。动态扫描是指通过轮流选通各个数码管来显示所有数字,而不是同时驱动所有数码管,这样可以节省硬件资源,尤其是在驱动多个数码管时。

Verilog是一种硬件描述语言(HDL),常用于数字逻辑系统的建模和仿真。在给出的程序中,`module seg`定义了设计的基本模块,它接受系统时钟`clk`、位选信号`wei`和段选信号`seg`作为输入。位选信号用于选择要显示的数码管,而段选信号则决定数码管上哪些段亮起,形成特定的数字形状。

程序中使用了分频器`reg clk1k`将系统时钟(50MHz)降低到1kHz,这样可以控制数码管的刷新速率。通过`reg [7:0] wei, seg`和`reg [3:0] coder`变量,程序可以存储当前选中的数码管和要显示的数字编码。`reg [15:0] count`可能是用来计数或控制显示循环的。

数码管显示技术通常需要译码器来将数字编码转换为对应的段选信号。在文中,`coder`变量可能就是这样的译码结果。作者提到由于不熟悉硬件部分,所以没有深入讨论,但他提供了程序运行效果的图片。

在学习过程中,由简单到复杂是常见路径,这个项目就是一个很好的实践案例。通过这个项目,学习者可以理解数字逻辑、时序控制以及Verilog编程的基本概念。同时,对于新手来说,实验板提供了一个实际操作和验证理论的平台,尽管可能会限制一些设计的灵活性,但它可以帮助初学者熟悉基本的硬件接口和工作原理。

这个数码管电子时钟设计涵盖了数字逻辑系统设计的基础知识,包括Verilog编程、时钟频率分频、动态扫描显示技术和数码管的控制。对于想要学习嵌入式系统或者FPGA设计的人来说,这是一个实用且有趣的入门项目。

316 浏览量

点击了解资源详情

2914 浏览量

688 浏览量

786 浏览量

120 浏览量

2021-10-03 上传

2021-10-04 上传

113 浏览量

shicunjie

- 粉丝: 0

- 资源: 2

最新资源

- DevKit:一个用于为COBI.Bike开发模块的Javascript库–智能手机和自行车的完美融合

- mydemo.rar

- evaluation1:第一次研究评估的github

- Instagram:初始提交

- timer_testing_type脚本

- tp01-isl

- AFLOWpi-1.2.1-cp35-cp35m-manylinux2010_x86_64.whl.zip

- refinr:聚类并合并相似的char值:Open Refine聚类算法的R实现

- 慧达网购防钓鱼下载 慧达网购防钓鱼 v1.0

- 基于fpga的信号发生器dds.zip

- Android SMS,Handler,Runnable和Service(新)

- nushell:一种新型的shell

- curso-de-python3-mundo-2:我从Curso emVídeo的Gustavo Guanabara教授的“ Curso de Python 3:Mundo 2”课程中学到的东西。 注意:这些是“ curso-de-python3-mundo-1”存储库的以下内容

- AFLOWpi-1.3-cp38-cp38-manylinux2010_x86_64.whl.zip

- circular-progress-chakra:使用React,Chakra和Javascript进行的简单循环进展

- Django学习最简单前后端项目代码