VERILOG实现USB2.0 IP核中文指南

需积分: 10 179 浏览量

更新于2024-07-15

收藏 3.36MB PDF 举报

"usb_doc中文修订版v1.1.pdf 是一份关于使用VERILOG代码实现USB2.0高速全速IP核的中文翻译文档,由Rudolf Usselmann编写,最初为英文版usb_doc.pdf。该文档详细介绍了如何使用这个USB功能IP核,并在2002年间经过多次修订和完善,包含了对寄存器、缓冲区、中断系统、DMA操作等方面的详细说明。IP核可从指定链接下载。"

这篇文档详细阐述了USB功能IP核的设计与实现,主要知识点包括:

1. **USB功能核心**:这是一个用VERILOG语言编写的USB2.0 IP核,支持高速和全速模式,用于实现USB设备控制器的功能。

2. **版本历史**:文档经过了多次修订,每次更新都涉及到功能的增强、错误的修正以及内容的完善,例如缓冲区设计的变化、中断系统的改进等。

3. **寄存器**:文档详细列出了USB核心中的寄存器,如帧号和时间寄存器(FRM_NAT)、控制寄存器、中断寄存器等,这些寄存器用于管理USB通信和设备状态。

4. **缓冲区设计**:文档描述了从单端口到双端口SSRAM的缓冲区变化,以及四倍缓冲和双缓冲的概念。还包含了缓冲区大小字段的添加,用于处理不同大小的数据包。

5. **中断系统**:文档详细介绍了中断机制,包括端点中断、挂起和继续中断,以及如何通过中断来响应USB事件。

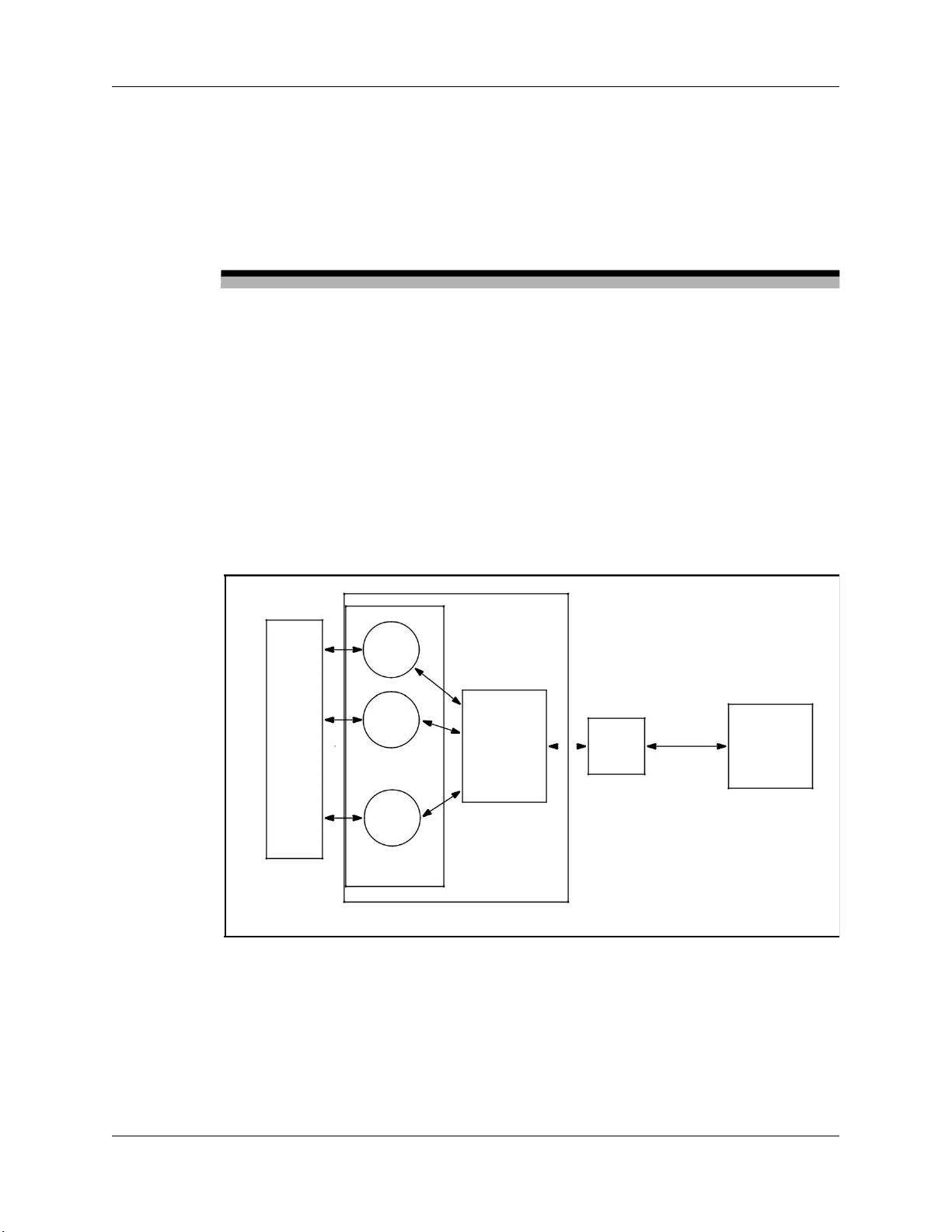

6. **DMA操作**:IP核支持DMA(Direct Memory Access)操作,提高了数据传输效率,降低了CPU的负担。

7. **WISHBONE接口**:WISHBONE是通用的片上系统(SoC)互连标准,IP核与外部系统通过WISHBONE接口进行通信,文档中提到添加了暂停输出功能,并对接口进行了优化。

8. **USB内核行为**:这部分详细说明了USB核心在处理数据传输、帧同步、错误检测等方面的行为。

9. **延迟和带宽要求**:文档中提到了关于延迟和带宽需求的分析,这对于理解和优化USB设备的性能至关重要。

10. **安装和使用指南**:除了技术细节,文档还包含了如何安装和使用IP核的说明,以及供应商控制IO端口寄存器的使用,方便开发者集成到自己的系统中。

11. **结构和附录**:文档附录详细解释了USB内核的结构,并提供了控制流程图,帮助读者理解USB功能核心的整体工作流程。

这份USB功能IP核的使用说明文档是VERILOG实现USB控制器的重要参考资料,为开发者提供了全面的技术指导。

点击了解资源详情

点击了解资源详情

335 浏览量

2025-01-06 上传

止涯丶

- 粉丝: 22

- 资源: 23

最新资源

- elasticsearch-analysis-ik-6.4.3.rar

- 4_dtsled_设备树驱动例程_

- SteamVR插件.rar

- HelloJava:一些java例子,希望对以后有帮助

- 网件A6100-V1.0.0.36驱动

- 【ssm项目源码】文档管理系统.zip

- clase_1_2021

- 使应用程序源不可知

- coffesploit:coffesploit是一个自动渗透测试框架

- driwwwle:Dribbble,但适用于Web开发人员。 与世界共享您的Web项目的门户

- WebSite2_数据稽核统计_

- DOTween Pro 1.0.zip

- MyTitlePageIndicatorDemo

- tc3kb_v500_upgrade TC3000B仪器固件

- 构建环境传播者插件

- sultan-spring